I Изобретение относится к измерительной технике и может быть, испол эовано для измерения различных динамических параметров.

- Известно устройство для измерени динамических параметров электронных блоков интегральных схем , в том числе времени установления выходного напряжения, содержащее дифференциальный дискриминатор, два порбговых устройства, времяамплитудный преобразователь, элемент задержки и элемент совпадения, выход которого соединен с входом элемента задержки, выход дифференциального дискриминатора соединен с входом времяамплитудного преобразователя l .

Недостатком его является то, что оно обладает сравнительно высокой температурной и временной погрешностью измерений, связанной с нестабильностью блоков устройства в первую очередь, элемента задержки и времяамплитудного преобразователя.

Наиболее близким по.технической сущности к предлагаемому является устройство для Измерения динамических параметров электронных блоков, содержащее последовательно соединенные элемент совпадения, блок задержки и.формирователь сигнала, вход которого соединен также с индикатором и первым входом элемента jfсовпадения, а выход - с входом испытуемого электронного блока, дифференциальный дискриминатор, первый вход которого подключен к выходу испытуемого электронного блока, второй и третий - к источнику опорных напряжений 2 .

Цель изобретения - расширение пределов измерения в область меньши значений.

Цель достигается тем, что в уст.ройство, содержащее последовательно соединенные первый элемент совпадения и блок задержки, выход которого соединен с первым входом первого элемента совпадения, с входом индикатора и с входом формирователя входного сигнала, выход которого соединен с зажимом для подключения входа испытуемого блока, источник опорного напряжения, первый и второ выходы которого соединены с первым и вторшм входами дифференциального дискриминатора напряжения, третий вход которого соединен с для подключения выхода испытуемого блока, введены последовательно соединенные второй элемент совпадения, одновибратор, интегратор и блок переменной задержки, причем первый вход второго элемента совпадения соединен с выходом Дифференциального дискриминатора напряжения, выход блока переменной задержки соединен с вторым входом первого элемента /

совпадения.и с втором входом второго элемента совп.адения, второй вход блока переменной задержки соединен с выходом блока задержки.

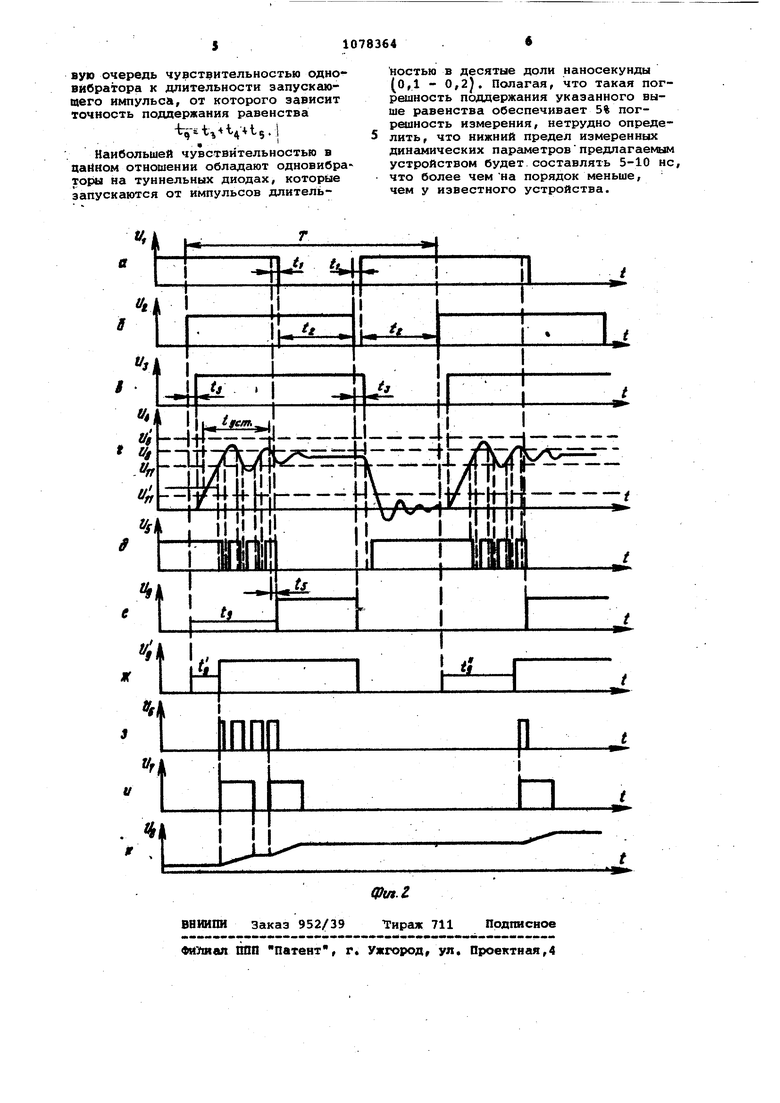

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - временные диаграммы, иллю стрирующие работу устройства.

Устройство содержит последовательно соединенные первый элемент 1 совпадения, блок 2 задержки, формирователь 3 сигнала, первый испытуемый блок 4, дифференциальный дискриинатор 5, второй элемент 6 совпадения , одновибратор 7, интегратор 8, блок 9 переменной задержки, а также индикатор 10 и источник 11 опорного напряжения. Вход индикатора 10 соединен с первым входом первого элемента 1 совпадения,и с входом блока 9 переменной задержки.

Источник 11 опорных напряжений соединен с вторыгл и третьим входами дифференциал1 ного дискриминатора 5, первый вход которого соединен с испытуемым блоком 4, а выход - с первым входом второго элемента 6 совпадения, второй вход которого соесоединен с выходом блока 9 переменной задержки, а выход - с входом одновибратора, выход которого соединен с входом интегратора 8, выход интегратора 8 соединен с первЕлм входом блока 9 переменной задержки, выход которого соединен с вторым входом первого элемента 1 совпгщения и с вторым входом втоЕюго элемента б совпадения. Вход формирователя 3 сигнала соединен с выходом блока 2 задержки, а выход - с входом испытуемого блока 4.

Элементы 1 и 6,совпадения осуществляют сравнение сигналов на входах и вырабатывают сигналы совпадения при равенстве этих сигналов. Блоки 2 и 9 задержки задерживают сигналы, поступающие на их входы. Формирователь 3 сигнала формирует испытательный сигнал для контроля блока 4. Дискриминатор 5 и источник 11 опорных напряжений обеспечивгиот отсчет динамических параметров на заданных . уровнях. Одновибратор . 7 вырабатывает импульс заданной формы при поступлении на его вход запускающего испульса. Интегратор 8 усредняет импульсы, поступающие на его вход fвыдeляeт постоянную составлякядую этих импульсов/. Индикатор 10 измеряет период (частоту) колебаний, устанавливающуюся в устройстве.

Устройство работает следующим образом.

Предположим, что на выходе блока 2 задержки появился положительный перепад напряжения (фиг. 2б) . Этот перепад, сформированный формирователем 3 .(фиг. 2в) , поступает на вход испытуемого блока 4, на выходе которого появляется выходной сигнал фиг. 2г). В течение интервала времени, когда выходное напряжение испытуемого блока 4 находится в зоне допустимой погрешности (между нижни и ц м верхним и в (фиг, 2г) порогами дискриминации дифференциального дискриминатора 5, задаваемь11-1и источ ником 11 опорных напряжений), сигнал на выходе дифференциального дискриминатора 5 равен нулю (фиг.2д Если же выходное напряжение испытуе мого блока 4 находится вне зоны допустимой погрешности, на выходе диф ференциального дискриминатора 5 появляется положительный потенциал (фиг. 2д). Импульсы с выхода дифференциального дискриминатора 5 поступают на второй элемент 6 совпадения, на вто рой вход которого приходит положительный перепад напряжения с выхода элемента 2 задержки, задержанный в блоке 9 переменной задержки. Если время задержки сигнала в блоке 9 переменной задержки меньше, чем вре мя установления выходного напряжения испытуемого блока 4 (фиг. 2ж), то на выходе второго элемента б совпадения появляются импульсы (фиг. 2з), запускающие одновибратор 7 (фиг. 2и). Импульсы одновибратора 7 поступают на интегратор 8, на выходе которого начинает увеличиваться напряжение (фиг. 2к), что вызывает увеличение задержки в блоке 9 переменной задержки. Возрастание времени задержки выходных сигналов блока 2 задержки в блоке 9 переменной задержки будет происходить до тех пор, пока величина его на станет равной (фиг. 2е) + tg, где i задержки сигналов в 3, 4 и 5 соответственно;Ьуст.- время установления напряжения в испытуемом блоке 4. При этом совпадении импульсов на входах второго элемента 6 совпадени не происходит, одновйбратор 7 не запускается и напряжение на выходе интегратора 8 не изменяется. При разряде интегратора описанный процесс повторяется, и напряжение на выходе интегратора 8 снова возрастает, поддерживая соотношение (1) с заданной степенью точности. в момент появления положительного перепада на выходе блока 9 переменной задержки (фиг. 2е) переключается элемент 1 совпадения (фиг.2а так как на его первом входе имеется положительное напряжение с выхода блока 2 за 1ержки (фиг. 2б) . Этот отрицательный перепад через время ij появится на выходе блока 2 задержки фиг. 2б) и под его действием на выходе элемента 1 совпадения, реализующего логическую функцию И-НЕ, появляется положительный перепад (фиг. 2а) , КОТОЕИЛЙ также задерживается блоком 2 задержки. Через время t2 на выходе блока 2 задержки появляется положительный перепал напряжения, и весь цикл повторяется. Таким образом, предлагаемое устройство представляет собой автогенератор с задержанной обратной связью, период .колебаний в котором равен (фиг. 2) T-tgVt 4t2 i,t t , где t, i и ie - задержка сигналов в блоках 1/ 2 и 9 .соответственно. В установившемся режиме, соответствукхцем условию (,i) , период равен T,2(t,+ +i3+i4U,j,;4tg. (з) ; Если в дифференциальном дискриминаторе 5 нижний порог дискриминации Кц установить на нижнем уровне отсчета t уст (обычно 0,. гдеОцст .ХСтаяЬвившёеся амплитудное значение Ьыходного напряжения испытуемого блока 4), а верхний И в - выше амплитудного значения выходного напряжения испытуемого блока 4(u|, и j на фиг. 2г), то в устройстве установится колебания с периодом T3-2(t,4t2V-t3 t44tg. (4) так как в этом случае выходное напряжение испытуемого блока 4 сразу входит .в зону допустимой погрешности и не выходит из нее ,. 2г , а время задержки в блоке 9 переменной задержки становится равным t(j 1 + i4 + 5. Из1.1ерив с помощью индикатора 10 периода (частоты) колебаний и Ту (f) можно определить время установления, испытуемого электронного блока 4 4 Т t ,.T,. Предлагаемое устройство, как и известное позволяет измерять другие динамические параметры электронвых блоков по методике, изложенной в 2} Аналогично производятся измерения и других динамических параметров испытуемого блока. В предлагаемой структуре погрешн6сть измерения-определяется в пер-

вую очередь чувствительностью одновибратора к длительности запускающего импульса, от которого зависит точность поддержания равенства

+ lj.l

Наибольшей чувствительностью в цаНном отношении обладают одновибраторы на туннельных диодах, которые запускаются от импульсов длительностью в десятые доли наносекунды (0,1 - 0,2. Полагая, что такая погрешность поддержания указанного выше равенства обеспечивает 5% погрелность измерения, нетрудно определить, что нижний предел измеренных динамических параметровпредлагаемым устройством будет составлять 5-10 не что более чемна порядок меньше, чем у известного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения динамических параметров электронных блоков | 1977 |

|

SU750402A1 |

| Устройство для измерения параметров дыхания | 1990 |

|

SU1803037A1 |

| Устройство для измерения дифференциальной нелинейности быстродействующих аналого-цифровых преобразователей | 1985 |

|

SU1282323A1 |

| Ультразвуковой измеритель скорости течений | 1981 |

|

SU987393A1 |

| Устройство для автоматического измерения параметров колебательных контуров | 1986 |

|

SU1406525A1 |

| Преобразователь напряжения в частоту | 1978 |

|

SU743195A1 |

| Устройство для измерения флуктуаций фазы импульсного сигнала | 1982 |

|

SU1019358A1 |

| Устройство для измерения частоты | 1979 |

|

SU813291A1 |

| Анализатор импульсных моментовлиНЕйНыХ СиСТЕМ АВТОМАТичЕСКОгОРЕгулиРОВАНия | 1979 |

|

SU847283A1 |

| Коммутационный фазометр | 1977 |

|

SU732761A1 |

УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДИНАМИЧЕСКИХ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ БЛОКОВ, содержащее последовательно соединенные первый элемент совпгщения и блок задержки, выход которого соединен с первым входом первого элемента совпадения, с входом индикатора и с входом формирювателя входного сигнала, выход которого соединен с зажимом для подключения входа испытуемого блока, источник опорного напряжения, первый и второй выходы которого соединены с первьчл и вторым входами дифференциального дискриминатора напряжения, третий вход которого соединен с зажимом для пoдкJнoчeния выхода испытуемого блока, отличающееся тем, что, -с целью расширения пределов измерения в область меньших значений, в него введены последовательно соединенные второй элемент совпадения, одновйбратор, интегратор и блок переменной задержки, причем первый вход второго элемента совпадения соединен с выходом дифференциального дискриминатора напряжения, выход блока переменной задержки соединен с вторым входом первого элемента совпадения и с вторым входом второ-ч го элемента совпадения, второй вход блока переменной задержки соединен с выходом блока згщержки

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Шатило Н.И | |||

| Автоматизация измерений динамических параметров линейных интегральных схем | |||

| - Тезисы докладов Всесоюзного научно-технического совещания | |||

| Линейные-интегральные схемы и их применение в приборостроении и промышлейной электронике | |||

| Л., 1977, с | |||

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для измерения динамических параметров электронных блоков | 1977 |

|

SU750402A1 |

| кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-03-07—Публикация

1982-11-02—Подача