;И С базой второго р -ti -р транзистора, соединенного эмиттером через включенный согласно-последовательно с ним светодиод и резистор с общей шиной и через т- 1 цепей, каждая из которых состоит из согласно-последовательно включенных с ним диода и резистора, с т- 1 выходами отрицательных блокирующих сигналов,коллектором - с отрицательным питающим входом, соединенным через резистор с коллектором первого р -п-р транзитора и с эмиттером п - р- п транзистора, коллектор которого подключе через резистор к положительному питающему входу и через п + 1 цепей, каждая из которых состоит из включенных встречно-последовательно с ним диода и резистора - к h + 1 выходам положительных блокирующих сигналов, при этом в состав каждой цейи нормализаторов введен стабилитрон, включенный между свободным выводом резистора цепи и входом нормализатора данной цепи, общая точка последовательно соединенных резисторов каждой цепи через резистор подключена к соответствующему выходу нормализатора, однополярные питающие входы блокираторов соединены с выходом инерционного звена одноименного по полярности источника питающего напряжения сигнальный вход каждого блокиратора соединен с соответствующим выходом одноименного с ним по полярности

нормализатора и с одним из однополяр.ных с ним выходов каждого из остальных блокираторов, а один из свободных выходов положительных блокирую;щих сигналов каждого блокиратора подключен к входу формирователя отклю(ающего сигнала, выход которого через датчик сигнала короткого замыкания соединен с управляющим входом ключевого элемента, а питающий вход соединен с выходом источника роложительного питающего напряжения.

2.Система по п. 1, отличающая с я тем, что формирователь

отключающего сигнала выполнен в виде триггера Шмитта, в коллекторную цепь одного из двух п - р - г транзисторов которого включена первичная обмотка импульсного трансформатора.

3.Система по п. 2, о т л и ч а -. ю щ а я с я тем, что в качестве датчика сигнала короткого замыкания использована вторичная обмотка импульс ного трансформатора формирователя

отключающего сигнала.

4.Система по п. 1, о т л и ч а ю щ а я с я тем, что, в качестве инерционного звена использован конденсатор, шунтирующий управляющий вход регулирующего элемента последовательного типа транзисторного стабилизатора линейного регулирования каждого из двух источников питающих

напряжений.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система вторичного электропитания | 1983 |

|

SU1171770A2 |

| Стабилизированный преобразователь напряжения | 1975 |

|

SU748390A1 |

| Преобразователь постоянного напряжения в переменное | 1990 |

|

SU1734178A1 |

| Источник электропитания с защитой от перегрузки по току | 1984 |

|

SU1325433A1 |

| Компенсационный стабилизатор постоянного напряжения | 1989 |

|

SU1665353A1 |

| Интегральная микросхема стабилизатора постоянного напряжения | 1990 |

|

SU1772794A1 |

| Компенсационный стабилизатор постоянного напряжения | 1989 |

|

SU1665354A1 |

| Источник питания с защитой | 1977 |

|

SU696434A1 |

| Стабилизированный источник постоянного тока | 1975 |

|

SU720422A1 |

| Устройство контроля сопротивления шлейфа | 1981 |

|

SU1226673A1 |

1. СИСТЕМА ВТОРИЧНОГО ЭЛЕКТРОПИТАНИЯ, содержащая электронную J аппаратуру, имеющую в своем составе незащищенный от короткого замыкания вторичный источник питания с п положительными гг отрицательными относительно общей шины контрольными выво.дами напряжений, нормализаторы положительных и отрицательных напряжений, составленных соответственно из п и hi цепей последовательно соединенных двух резисторов, один из которых свободным выводом подключен к общей шине, а входы указанных нормализаторов подключены к контрольным выводам аппаратуры, ключевой элемент с управляющим входом, выходом соединенный с питающим входом аппаратуры, а силовым входом - через выключатель с питающей сетью, и источник положительного питающего напряжения, вход которого соединен с cшloвы f входом ключевого элемента, а выход - с входом инерционного звена, отличающая с я тем, что, с целью сокращения времени поиска места короткого замыкания путем его локализации, в нее введены дополнительное инерционное звено, источник отрицательного питающего напряжения, вход и выход которого соответственно соединены с входом источника питающего напряжения и входом дополнительного инерционного звена, датчик сигнала короткого замыкания, формирователь отключающего сигнала, m блокираторов для отрицательных напряжений и п блокираторов для положительных напряжений, в состав каждого из которых входит п-р-п транзистор, соединенный базой с сигнальным входом, эмиттером - с общей шиной, а коллектором - через стабилитрон и резистор с базой р-п-р транзистора, и с базой второго п-р-п транзистора, соединенного эмиттером через включенный согласно-последовательно с ним светодиод и резистор с общей щиной и через h цепей, каждая из которых состоит из согласно-последовательно включенных с ним диода и ре- ; зистора -СП выходами положительных блокирующих сигналов, коллектором с положительным питающим входом,соециненным через резистор с коллектором первого ц-р-п транзистора и с э№1ттером р-п -р транзистора. Коллектор которого подключен через резистор к отрицательному питающему входу и через п цепей, каждая из которых состоит из включенных встречнопоследовательно с ним диода и резистора, - к m выходам отрицательных блокирующих сигналов, в состав каждого из m блокираторов осрицательных напряжений входит р - г - р транзистор, соединенный базой с сигнальным входом, эмиттером - с общей шиной, а коллектором - с базой г - р - п транзистора через стабилитрон н резистор

Изобретение относится к электротехнике и предназначено для защиты от короткого замыкания вторичного источника питания с п положительньми и m отрицательными выходными напряжениями, введенными на контрольные клеммы электронного прибора, в сос.тав которого входит указанный источник, с одновременной индикацией аварийной цепи по каждому из контролируемых выходнь1Х напряжений источника

Известно устройство для защиты источников питания, состоящее из нескольких стабилизаторов напряжения положительной и отрицательной полярности, в котором при пропадании одно го из контролируемых разнополярньк напряжений вторичного источника питания, для отключения его от первично5 ного источника формируется сигнал постоянного тока tl3«

I Недостатками этого устройства являются гальваническая связь отклю чающего сигнала с. контролируемыми 10 напряжениями и отсутствие элемента. Индицирующего состояние устройства

. заняты.

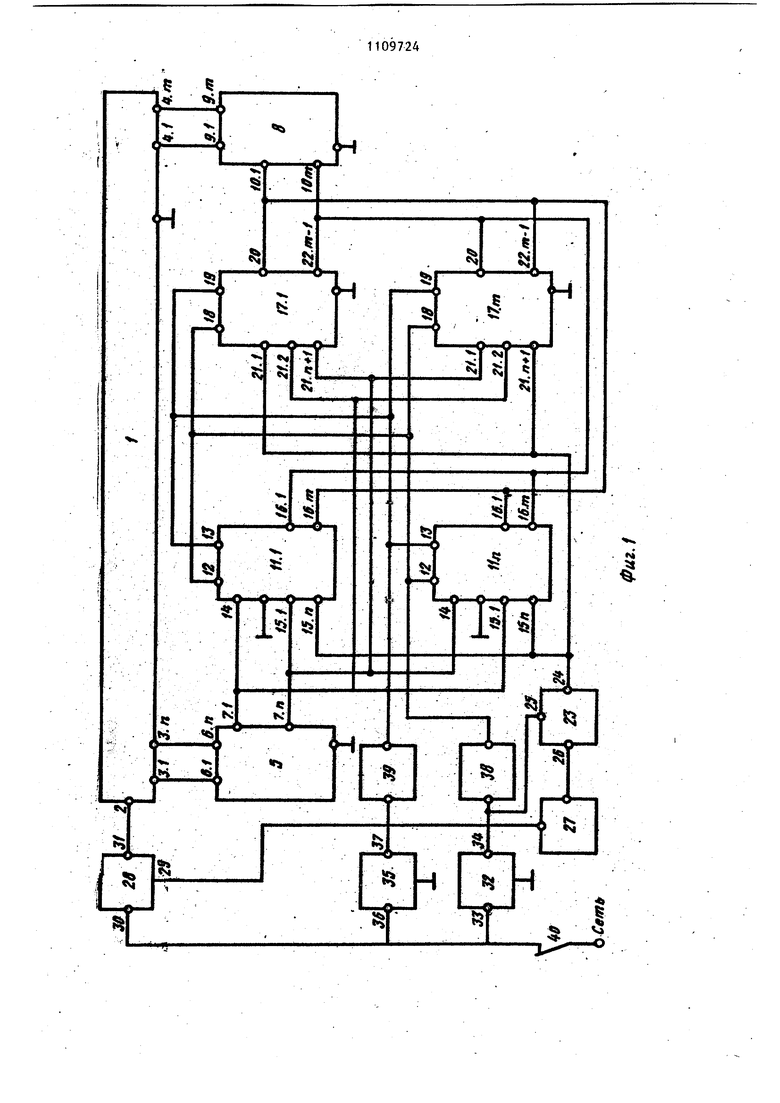

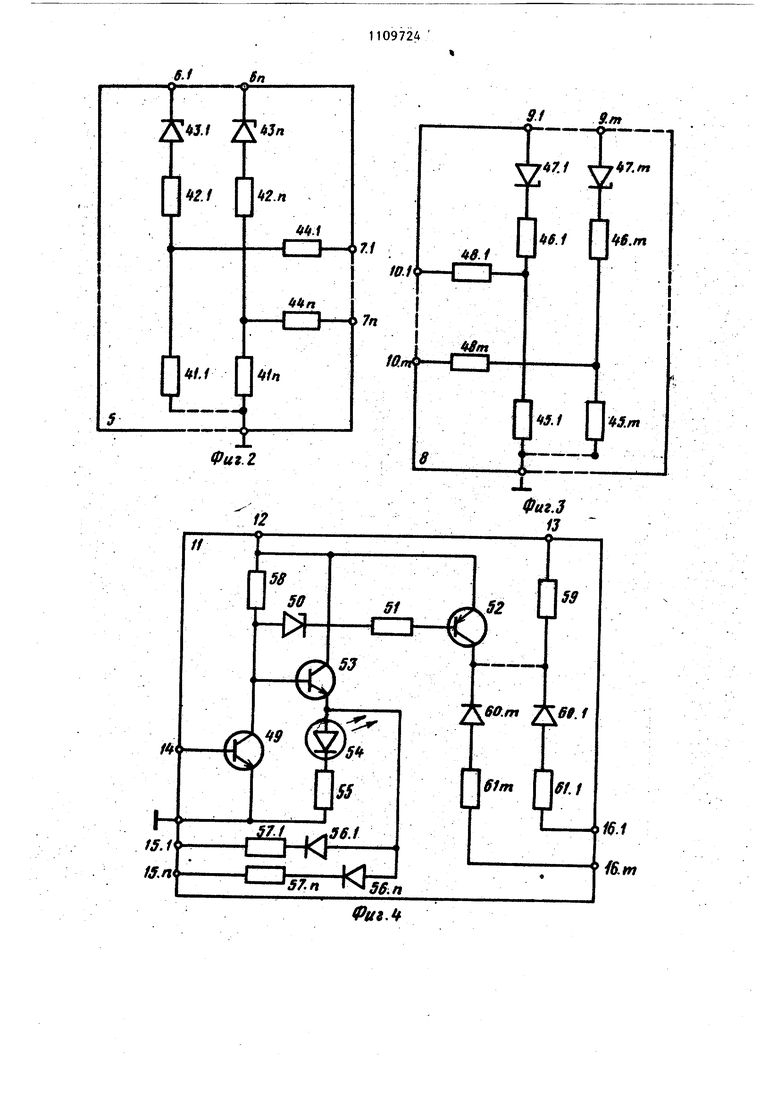

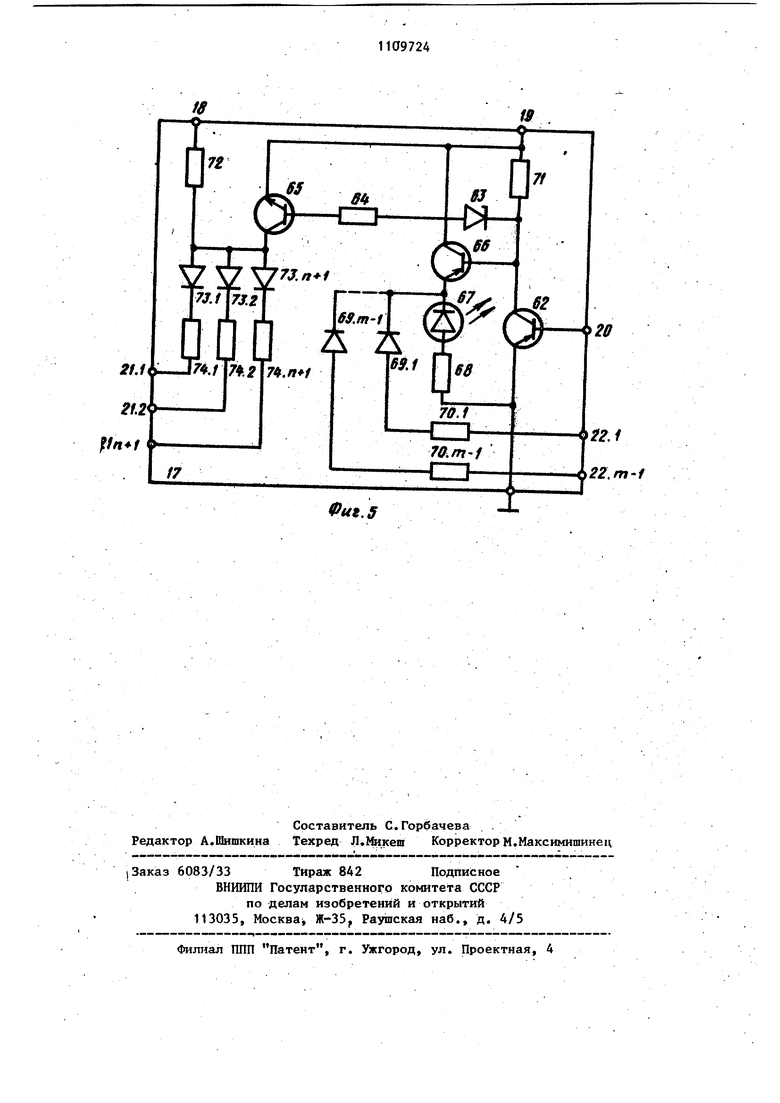

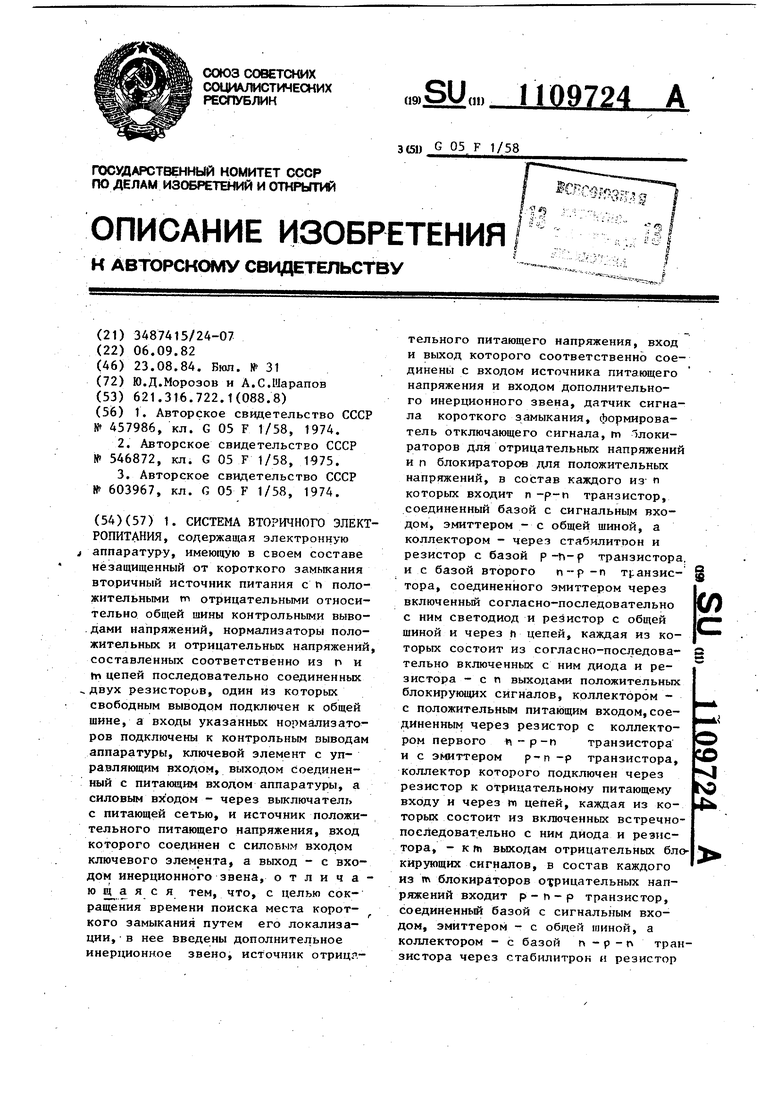

Известно устройство для защиты 15 источников питания, которое имеет элемент, индицирующий его состояние 2, Однако известное устройство также формирует отключающийся сигнал, галь ванически связанный с разнополярными контролируемыми напряжениями. Наиболее близкой к изобретению является система вторичлого электропитания, содержащая электронную аппа ратуру, имеющую в своем составе незащищенный от короткого замыкания вторичный источник питания с п положительными и Vn отрицательными напряжениями, введенными на контрольные выводы, нормализаторы положительных и отрицательных напряжений, составленных соответственно из п и m цепей последовательно соединенных двух резисторов, один из которых свободным выводом подключен к общей шине, а входы указанных нормализаторов подключены к контрольным выводам anrtapaтуры, ключевой элемент с. управляющим входом, выходом соединенный с питающим входом аппаратуры, а силовь1м входом - через выключатель - с питающей сетью, и источник положительного питающего напряжения, вход которого со единен с силовым входом ключевого элемента, а выход - с входомИнерцион ного звена З. Однако при использовании известного устройства нельзя определить пропадание или уменьшение до определенного уровня какого-то из контролируемьк напряжений, явивщегося причиной отключения вторичного источника питания от питающей сети. Этот недостаток свойственен всем известным устройствам и существенно увеличивает время определения места короткого замыкания или какой-либо другой подобной неисправности в системе электропитаняя. Это время увеличивается с увеличением числа контролируемых напряжений. Целью изобретения является сокращение времени поиска места короткого .замыкания путем его локализации. Поставленная цель достигается тем что в систему вторичного электропитания, содержащую электронную аппаратуру, имеющую в своем составе незащищенный от короткого замыкания вторичный источник питания с п положительны ми и № отрицательными относительно общей шины контрольными вьгеодами напряжений, нормализаторы положительных и отрицательных напряжений, составленных соответственно из Пит цепей последовательно соединенных двух резисторов, один из ко.торых свободным выводом подключен к общей шине, а входы указанных нормацизаторов подключены к контрольным выводам аппаратуры, ключевой элемент с управляющим входом, выходом соединенный .с питающим входом аппаратуры, а силовым входом через выключатель - с питающей сетью, и источник -положительного (питающего напряжения, вход которого соединен с силовым входом ключевого элемента, а выход - с входом инерционного звена, введены дополнительное инерционное звено, источник отрицательного питающего напряжения, вход и выход которого соответственно соединены с входом источника положительного питающего напряжения и входом, дополнительного инерционного звена, датчик сигнала короткого замыкания, формирователь отключающего сигнала, m блокираторов для отрицательных напряжений и п блокираторов для положительных напряжений, в состав каждого из п которых входит г - р - Г1 транзистор, соединенный базой с сигнальным входом, эмиттером - с общей шиной, а коллектором - через стабилитрон и резистор с базой р транзистора, и ,с базой второго h-р -п транзистора, соединенного эмиттером через включенный согласнопоследовательно с. ним светодиод и резистор с общей шиной и через п це- пей, каждая из которых состоит из согласно-последовательно включенных с ним диода и резистора, - с п выходами положительных блокирующих сиг-, налов, коллектором - с положительным питающим входом, соединенным через резистор с коллектором первого п р - п транзистора и с эмиттером p-H-p транзистора, коллектор которого подключен Через резистор к отрицательному питающему входу и через m цепей, каждая из которых состоит из включенньк встречно-последовательно с ним диода и резистора, - к гп.. выходам отрицательных блокирующих сигналов, в состав каждого из № блокираторов отрицательных напряжений входит р -h -р транзистор, соединенный базой с сигнальным входом, эмиттеров - с общей шиной, а коллектором - с базой г« - р -h транзистора через стабилитрон и резистор и с базой второго n-p-n транзистора, соединенного эмиттером через включенный согласно-последовательно с ним светодиоД и резистор с общей шиной и через 1 цепей, каждая )из которых состоит из согласно-последовательно включенных с ним диода и резистора, - с tti - 1 выходами отр1щательныхблокирующих сигналов, коллектором - с отрицательным питающим входом, соединенным через резисT jp с коллектором первого р - п - р транзистора и с эмиттером h- р-п транзистора, коллектор которого подключен через резйЪтор к положительному питающему входу и через п + 1 цепей, каждая из сострит из включенных встречно-последовательно с ним диода и резистора, - к п + 1 вьвсодам положительных блокируннцих сигналов, при этом в состав каждой цепр нормализаторов введен стабилит,рон, включенный между свободным выво |дом резистора цепи и входом нормализатора данной цепи, общая точка последовательно соединенных резисторов каждой цепи через резистор подключена к соответствуюичему выходу нормали затора, однополярные питакнцие входы блокираторов соединены с выходом инерционного звена одноименного по полярности источника питакщего напря жения, сигнальный вход каждого блоки ратора соединен с соответствующим вы .ходом одноименного с ним по полярнос ти нормализатора и с одним из однополярных с ним выходов каждого из остальных блокираторов, а один из св бодных вькодов положительных блокиру ющих сигналов каящого блокиратора подключен к входу формирователя отключаюо го сигнала выход которого .через датчик сигнала короткого sai iкания соединен с управляющим входом влючевогр элемента, а питающий вход соединен с выходом источника положительного питакщего напряжения. При этом формирователь отключающе го сигнала выполнен в виде триггера ПЫитта, в кбллекторную цепь одного из двух р- транзисторов которо .го включена первичная обмотка импульсного трансформатора. Причем вторичная обмотка импульсного трансфорь4атора формирователя отключакщего Ьигнапа использована в качестве датчика сигнала короткого замыкания. Кроме того, в качестве инерционного звена использован конденсатор, шунтирующий управляющий вход регулирующего элемента последовательного типа транзисторного стабилизатора линейного регулирования каждого из двух источников питающих напряжений. На фиг. 1 представлена структурная схема системы вторичного электропи;тания; на фиг. 2 - принципиальная схема нормализатора положительного напряжения; на фиг. 3 - принципиальная схема нормализатора отрицательных напряженийi на фиг. 4 - принципиальная схема блокиратора для положительных напряжений/ на фиг. 5 - принципиальная схема блокиратора для отрицательных напряжений. Система вторичного электропитания содержит электронную аппаратуру 1, для питания которой используется входящий в ее состав незащищенный от короткого замыкания вторичный rfcTO4 ник питания с питакицим входом 2, положительными выходными напряжениями, введенными на контрольные клеммы 3.1 - 3п,m отрицательными выходными напряжениями, введенньми на контрольные клем1 в 1 4.1 - 4. m и выводом , на общую шину, нормализатор 5 положительныхнапряжений с выводом на общую шину, входами 6.1 - 6. п и г выходами 7.1 - 7.к, нормализатор 8 отрицательных напряжений с выводом на общую шину, входами 9.1 - 9,fn и п вькодами 10.1 - 10.hn,-h блокираторов 11 для положительных напряжений (11.1 - 11. 1 ), каждый из которых снабжен выводом на общую шину, положительным питающим входом 12, отрицательным питающим входом 13, сигнальным входом 14,п выходами 15.1 - 15. 15.г положительных блокирующих сигналов и m выходами 16.1 - 16.т отрицательных блокирующих сигналов, m блокираторов 17 для отрицательных напряжений (17.1 - 17. пп), каждый из которых снабжен выводом иа общую шину, положительным питающим входом 18, отрицательным питающим входом 19-, сигнальным входом 20, t +1 выходами 21. -2t.n+ 1 положительных блокирующих сигналов и 1 выхода- мй 22.1 - 22i го- I отрицательных блокирукицих сигналов, фopмиpoвaтeлJЬ; 23 отключающего сигнала с сигнальным входом 24, питающим входом 25 и выходом 2б| датчик 27 сигнала короткого замыкания, ключевой элемент 28 с управляю1цим входом 29, силовым входом 30 и выходом 31, источник 32 положительного питающего напряжения с выводом на общую шину, входом 33 и выходом 34, источник 35 отрицатель него питающего напряжения с вьгоодом на общую шину, входом 36 и выходом 37, два инерционных звена 38 и 39 и сетевой выключатель 40. Функциональные узлы системы соединены между собой следующим образом. Положительный питающий вход 12 блокираторов 11, положительный питаю щий вход 18 блокираторов 17 соединены через инерционное звено 38 с вых&двм 34 источника 32 положительного питанще го напряжения, который соединен также с питающим входом 25 формирователя 23 отключающего сигнала. Отрицательный питающий вход 13 блокираторов 11, отрицательный питаю щий вход 19 блокираторов 17 соединены через инерционное звено 39 с выхр дом 37 источника 35 отрицательного питающего напряжения. Контрольные клеммы 3.1 - 3.t anгпаратуры 1 соединены соответственно .с входами 6.1 - 6.И Нормализатора 5 а контрольные клеммы 4.1 - 4.п аппаратуры 1 соединены соответственно с входами 9.1 - 9.1TI нормализатора 8. Каждый из входов 7 нормализатора 5 соединен с сигнальным входом 14 соответствующего контролируемому напря жению блокиратора 11, с одним из выходов 15 положитепьньк блокирующих сигналов каждого из остальных блокираторов 11 и с одним из выходов 21 положительных блокирующих сигналов каждого из блокираторов 17. Кажды nit выходов 10 нормализатора 8 соединен с сигнальньи входом 20 соответствующего контролируемому напряжению блокиратора 17, с одним из выходов 22 отрицательных блокирующих сигналов каждого из остальньк блокираторо 17 и с одним из выходов 16 отрицательных блокирующих сигналов каждого из блокираторов 11. Свободные от сое динений выходы положительных блокирующих сигналов, например выход 15 каждого из блокираторов 11 и выход 21. ь+ 1 каждого из блокираторов 17 соединены с сигнальным входом 24 формирователя 23 отключающего сигнала, выход 26 которого чбрез датчик 27 сигнала короткого замыкания подключен к управляющему-входу 29 ключе- вого злемента 28j соединенного своим выходом 31 с питающим входом 2 электронной аппаратуры 1.. Силовой вход 30 ключевого злемента 28 соединен с входом 33 источника 32 положительного питающего напряжения, с входом 36 источника 35 отрицательного питающего напряжения и через сетевой выключатель 40 - с питающей систему сетью. Нормализатор 5 положительных напряжений (фиг. . 2) состоит из п цепей последовательно соединенных резисторов 4Т (41.1 - 41.h) и 42 (42.1 42.и), свободный вывод одного из которых. Например 41 (41.1 -. 41.h), соединен с общей шиной, свободный вывод другого резистора 42 (42.1 42.п) соединен через включенный в режиме стабилизации стабилитрон 43(43. 1 - 43. п ) с соответств тощим входом - 6.ti для подачи на него положительного контролируемого напряжения, а общая точка резисторов 41 (41.1 - 41.п) и 42 (42.1 - 42.П) каждой цепи соединена через резистор 44(44.1 - 44oti) с соответствующим йыходом 7.1-7.1. НормализатЪр 8 отрицательных напряжений (фиг. 3) состоит из цепей последовательно соединенных резисторов 45 (45.1 - 45.т) и 46 (46.1 46.tr), свободный вывод одного из которых, например 45 (45.1 - 45.ч), . соединен с общей шиной, свободный вывод другого резистора 46 (46.1 46.т) соединен через включенный в режиме стабилизации стабилитрон 47 (47.1 - 47.т) с соответствующим входом 9.1 - 9.т для подачи На него отгрицательных контролируемых напряжений, а общая точка резисторов 45 и 46 каждой цепи соединена через резистор 48 (48.1 - 48.т) с соответствующим выходом 10.1 - 10.1Г1, В блокиратор 11 для положительных напряжений 11 (11.1 - 11.Ю (фиг.4) входит п-р-п транзистор 49, соединенный базой с сигнальным входом 14, эмиттером - с общей шиной, а коллектором через включенный в режиме стабилизации стабилитрон 50 и реэис-ч тор 51 - с базой р -п -р транзисторА 52 и с базой п-р-п транзистора 53, соединенного эмиттером через включенный согласно-последовательно с ним светодиод 54 и резистор 55 с общей шиной, и через п цепей из сргласнопоследовательно включенных с этим эмиттером диода 56 (56.1 - 56,м) и резистора 57 (57,1 - 57.п) - с выходами 15,1 - 15,г«. Коллектор транзистора 53 соединен с положительным питающим входом 12, соединенным с коллектором м -р- h транзистора 49 через резистор 58 и с эмиттером р-Н-р транзистора 52. Коллектор транзистора 52 подключен через резистор.59 к отрицательному питающему входу 13 и через m цепей, каждая из которых состоит из включенньк встречно-последовательно с ним диода 60 и (60,160,(я) и резистора 61 (61,1 - 6l,w), к выходам 16,1 - 16,(ti, , В блокиратор 17 для отрицательных напряжений входит р - ti - р транзистор 62, соединенный базой с сигнальным входом 20, эмиттером - с общей шиной, а коллектором через включенный в режиме стабилизации стабилит рон 63 и резистор 64 - с базой ц- р- п транзистора 65 и с базой .р-п-р транзистора 66, соединенного эмиттером через включенный согласнопоследовательно с ним светодиод 67, и резистор 68 с общей шиной и через fn- 1 цепей, каждая из которых сое-, тоит из согласно-последовательно включенных с этим эмиттером диода 69 (69.1 - 69. Гр- 1) и резистора 70 (70,1 - 70. tn- 1), - с выходами 22,1 22, т- 1, Коллектор транзистора 66 соединен с отрицательным питающим входом 19, соединенным через резистор 71 с коллектором р- м-р транзистора 62 и с эмиттером транзистора 65, Коллектор транзистора 63 подключен через резистор 72 к положительному питающему входу 18 и через Ъ + 1 цепей, каждая изкоторых состоит из включен1а1х встречно-после довательно с ним диодов 73 (73,1 73.П + 1) и резисторов 74 (74,1 74. h+ 1), - к выходам 21.1 - 21. В качестве формирователя 23 отклю чающего сигнала использован, наприме .триггер Шмитта, в коллектор одного и двух транзисторов которого включена первичная обмотка импульсного трансформатора. В качестве датчика 27 сиг нала короткого замьжания использована, например, вторичная обмотка импульсного трансформатора формировагвйя 23,Источники положительного 32 и отрицательного 35 питающих напряжений составлены, например, каждый из силового трансформатора, выпрямителя, фильтра и транзисторного стабилизатора линейного регулирования с последовательным регулирующим элементом. Инерционные звенья 38 и 39 выполне- ны каждое, например, в виде конденсатора, шунтирующего управляющий вход регулирующего элемента источника 32 и 35 соответственно. Система работает следующим образом, В установившемся рабочем режиме все п положительные и tn отрицательные выходные напряжения вторичного источника питания электронной аппаратуры 1 имеются соответственно на контрольных клеммах 3,1 - 3. h и 4,1 - 4. т) относительно общей шины. Каждое из этих напряжений поступает на соответствующий вход 6.1 - 6,п нормализатора 5 положительных напряжений и вкод 9, 1 - 9,hfi нормализатора S отрицательных нап)ряжений и доводится каждой из п и in цепей соответствующего нормализатора до напряжения минимальной величины, необходимой для поддержания транзистора 49 каждого из и блокираторов 11 (11,1 - 11,Ь) и транзистора 62 каждого из гг« блокира-.торов 17 (17.1 - 17.т) в открытом состоянии. Эти напряжения являются входными напряжениями блокираторов 11 (11.1 - ll.h) и 17 (17,1 - 17,пО. При этрм для увеличения чувствительности блокираторов It (11,1 - 11,h) и 17 (17.1 - 17.n) целесообразно вы бирать стабилитроны 43(43.1 - 43,h) нормализатора 5 ( 5.1 - 5.п) и стабилитроны 47 (47,1 - 47,т) нормализатора 8 (8.f - 8.™) на напряжение, возможно, близкое к разности контролируемого выходного напряжения вторичного . источника питания электронной аппаратуры 1 и входного напряжения соответствухяцего из блокираторов 11 (11.1 11.о) и 17 (17.1 - 17,hi). Таким о браг, зом, наличие на контрольных клеммах 3 (3.1 - З.п) и 4 (4.1 - 4.т) выходных напряжений вторичного источника питания электронной аппаратуры 1 обуславливает наличие .на сигнальных входах 14 каждого из п блокираторов 11 (11.1 - И.п) и на сигнальных входах 20 каждого из m блокираторов 17 (17.1 - 17.ID) входного напряжения.

Все блокираторы 11 (11.1 - 11.h) одинаковы, а блокираторы 17 (17.1 17. )отличаются от них лишь полярностью входного сигнала и, в связи с этим, изменением npoBOJ5(HMOCTH на противоположную соответствующих транзисторов.. Поэтому дальнейшая работа системы может быть понята на примере работы одного блокиратора, например 11.1.

При наличии на сигнальном, входе 14 входного сигнала транзистор 49 открыт и .замыкает своим переходом коллектор - эмиттер общую шину с бат ЗОЙ транзистора 53, запирая его, и через стабилитрон 50 и резистор 51 с базой транзистора 52, поддерживая его В открытом состоянии. Ввиду зтого ток через светодиод 54 и ограничительный резистор 55 не идет, светодиод 54 не светится, а диоды 56.1 56.h заперты, так как напряжение на эмиттере запертого транзистора 53 относительно общей ишны близко к нулю. Вместе с этим через открытый переход коллектор - змиттер транзистора 52 на катоды диодов 60.1,- 60.w поступает потенциал с источника 32 положительного питающего напряжения, запирая их. попаданий на сигнальном входе 14 входного напряжения вследствие короткого замыкания контролируемого положительного напряжения вторичного источника питания электронной аппаратуры 1, выведенного на контрольную клемму 3.1, или его перегрузки, транзистор 49 закрьтается. Смена состояния транзистора 49 вызьюает смену состояния транзистора 53 (он откроется) и транзистора 52 (он закроется). Закрывшийся тран зис-гор 52 отключит от катодов диодов 60 (60.1 - 60.) запирающий их положительный потекхи ал источника 32, присутствующий на питающем входе 12. Все m диодов 60 (60.1 - 60.т) откроются приложенным к их катодам через резистор 59 отрицательным потенциалом , источника 35, присутствующие на

питающем входе 13, передавая на У выходов 16 (16.1 - 16.т) через м ре, зисторов 61 (61.1 - 61.г«) отрицательные блокирующие сигналы,, которые, поступив на сигнальные входы 20 тл блокираторов 17 (17.1 - 17.т), задублируют их входные напряжения.

Открывщийся транзистор. 53 подклю1чит положительный потенциал питающего входа 12 к аноду све одиода 54, который, засветившись,вследствие проходящего через него и резистор 55 к общей шине тока, -определит аварийную цепь э.лектронной аппаратуры 1, и к анодам ti диодов 56 (56.1 - 56.п) Все ft диодов 56 (56.1 - 56.п) откроются, передавая через г« резисторов 57 (57.1 - 57.гп) на h выходов 15 (15.1 -15.h) блокирующие сигналы. п- 1 из этих сигналов поступят на сигнальные входы 14 блокираторов 11.2 - tl.h, дублируя их входные напряжения, а один из положительных блокирующих сигналов, например с выхда 15.п, поступит на сигнальный вход 24 формирователя 23 отключающего сигнала. На выходе 26 формирователя 23 появится выходной сигнал,, который через датчик 27 тока поступит на управлякишй вход 29 ключевого элемента 28 и отключит им сетевое напряжение от питающего входа 2 электронной аппаратуры 1.

По получении информации от засветившегося светодиода 5Асистему отключают от питающей сети вьислючателем 40 и устраняют неисправность аварийной цепи электронной аппаратуры 1

По устранению неисправности электронной аппаратуры 1 выключателем 40 покдлючают к системе сетевое напряжение, которое вследствие отсутствия сигнала на управляющем входе 29 ключевого элемента 28 поступит через него на питающий вход 2 электронной аппаратуры t. Одновременно с этим напряжение питающей сети поступит на входы 33 и 36 источников .32 и 35 питания соответственно. Инерционные звенья 38 и 39 задержат появление напряжений от источников 32 и 35 на питающих: входах 12, 13, 18, 19 и 25 всех блокираторов 11 (11.1 - 11.П) и 17 (17.1 - 17.т) на время, не меньшее максимального времени установления выходных напряжений вторичного источника питания электронной аппаратуры 1 на всех ее п и m контрольных клеммах 3 и 4 соответственно. Пктание формирователя 23 осуществляется без задержки.

Система допускает подключение к сети при наличии ; необнаруженной неисправности.

В этом случае после установления вькодных напряжений вторичного источника питания элек11)онной аппаратуры

1 на ее контрольных клеммах 3 (3.13. ) и 4 (4,1 - 4. ) кроме напряже-. :ния, одного или нескольких, питающих аварийные цепи электронной annapaiTy{ры 1 и по истечении времени задерж ки инерционных звеньев 38 и 39, выс1 ветятся светодиоды блокираторов, контролируемых выходные напряжения вторичного источника питания электронной аппаратуры 1, питай1|||(ге ее неисправные цепи

Предложенная система вторичного электропитания, по сравнению с известным устройством, позволяет локализировать поиск неисправности в электронной аппаратуре до известной аварийной цепи, что существенно уменьшает время поиска неисправности особенно При значительном количестве выходных напряжений вторичного исто;чника питания этой аппаратурьл

«vt

Фиг, 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля и защиты от коротких замыканий источников питания | 1973 |

|

SU457986A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1984-08-23—Публикация

1982-09-06—Подача