2. Реле по п.1, отличающ-е е с я тем, что ключевой блок содержит два транзистора разного типа проводимости и дьа резистора, причем база первого транзистора подкпючена к первому входу блока, его эмиттер - к второму его входу, коллектор через первый резистор соединен с базой второго транзистора, подключенной через второй резистор к потенциальной шине внешнего источника йостоянного напряжения, к которому подключен и эмиттер второго транзистора, коллектор которого подключен к выходу ключевого блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для допускового контроля напряжений | 1981 |

|

SU1091124A1 |

| Устройство для воспроизведения зоны нечувствительности | 1982 |

|

SU1119038A1 |

| Многоканальное резервированное аналоговое устройство | 1980 |

|

SU984089A2 |

| Устройство для мажоритарного выбора непрерывных сигналов | 1982 |

|

SU1027826A1 |

| Импульсный регулятор | 1990 |

|

SU1829026A1 |

| Мажоритарное устройство для выделения проекций векторной величины | 1983 |

|

SU1115235A2 |

| Устройство выбора непрерывного сигнала по принципу большинства | 1984 |

|

SU1193800A2 |

| Устройство для воспроизведения разрывных функций | 1985 |

|

SU1297083A1 |

| Устройство для допускового контроля напряжений | 1985 |

|

SU1287121A1 |

| Устройство для мажоритарного выбора составляющих многомерного векторного сигнала | 1983 |

|

SU1136335A1 |

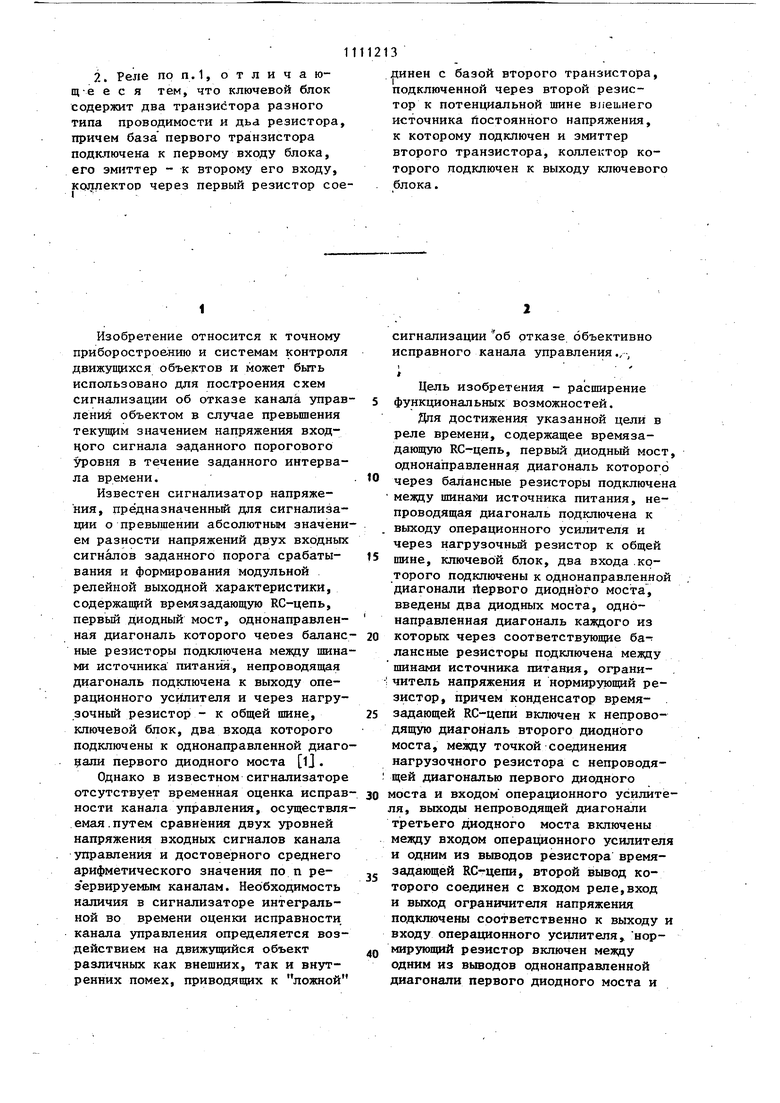

РЕЛЕ ВРЕМЕНИ, содержащее времязадающую RC-цепь, первый диодный мост, однонаправленная диагональ которого через балансные резисторы подключена между шинами источника питания, непроводящая диагональ подключена к выходу операцион- кого усилителя и через нагрузочный резистор к общей шине, ключевой блок, два входа которого подключены к од:нонаправленной диагонали первого ди1 одного моста, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены два диодных моста, однонаправленная диагональ каждого из которых через соотвеЕствующие балансные резисторы подключена между шинами источника питания, ограничитель напряжения и нормирующий резистор, причем конденсатор времязадающей КС-цепи включен в,непроводящую диагональ второго диодного моста, между точкой соединения нагрузочного резистора с непроводящей диагональю первого диодного моста и входом опе1 рационного усилителя,выводы непроводящей диагонали третьего диодного моста включены между входом операционного усилителя и одним из выво- . дов резистора времязадающей КС-цепи, СП второй вывод которого соединен с входом реле, вход и выход ограничителя напряжения подключены соответственно к выходу и входу операционg ного усилителя, нормирующий резистор включен мезвду одним из выводов ,однонаправленной диагонали первого диодного моста и одним из входов ключевого блока, выход которого подключен к выходу реле.

Изобретение относится к точному приборостроению и системам контроля движущихся объектов и может быть использовано для построения схем сигнализации об отказе канала управлений объектом в случае превышения текущим значением напряжения входного сигнала заданного порогового уровня в течение заданного интервала времени.

Известен сигнализатор напряжения, прёдназначенньй для сигнализации о превышении абсолютным значением разности напряжений двух входных сигналов заданного порога срабатывания и формирования модульной релейной выходной характеристики, содержапщй времязадающую RC-цепь, первый диодный мост, однонаправленная диагональ которого чеоез балансные резисторы подключена между шинами источника питания, непроводящая диагональ подключена к выходу операционного усилителя и через нагрузочньй резистор - к общей шине, ключевой блок, два входа которого подключены к однонаправленной диаго али первого диодного моста lj .

Однако в известном сигнализаторе отсутствует временная оценка исправности канала управления, осуществляемая, путем сравнения двух уровней напряжения входных сигналов канала управления и достоверного среднего арифметического значения по п резервируемым каналам. Необходимость наличия в сигнализаторе интегральной во времени оценки исправности канала управления определяется воздействием на движущийся объект различных как внешних, так и внутренних помех, приводящих к ложной

сигнализации об отказе, объективно исправного канала управления.,

1 f

Цель изобретения - расширение функциональных возможностей.

Для достижения указанной цели в реле времени, содержащее времязадающую RC-цепь, первый диодный мост, однонаправленная диагональ которого через балансные резисторы подключена меядчу шинайи источника питания, непроводящая диагональ подключена к выходу операционного усилителя и

через нагрузочный резистор к общей шине, ключевой блок, два входа .которого подключ-ены к однонаправленной диагонали rtepaoro диоднЬго моста, введены два диодных моста, однонаправленная диагональ каждого из которых через соответствующие ба-; лансные резисторы подключена между шинами источника питания, ограничитель напряжения и нормирующий резистор, причем конденсатор времязадающей RC-цепи включен к непроводящую диагональ второго диодного моста, меащу точкой соединения нагрузочного резистора с непроводящей диагональю первого диодного моста и входом операционного усилителя, выходы непроводящей диагонали третьего диодного моста включены между входом операционного усилителя и одним из выводов резистора времязадающей RC-цепи, второй вывод которого соединен с входом реле,вход и выход ограничителя напряжения подключены соответственно к выходу и входу операционного усилителя, нормирующий резистор включен меяоду одним из выводов однонаправленной диагонали первого диодного моста и 3 одним из входов ключевого блока, вы ход которого подключен к выходу рел В реле времени ключевой блок мо-жет содержать два транзистора разно типа проводимости и два резистора, причем база первого транзистора подключена к первому входу блока, его эмиттер - к второму его входу, коллектор через первый резистор сое динен с базой второго транзистора, подключенной через второй резистор потенциальной шине внешнего источни ка постоя«ного напряжения, к которо му подключен и эмиттер второго тран зистора, коллектор которого подключен к выходу ключевого блока. На чертеже представлена принципиальная электрическая схема предлагae гo устройства. , т, Реле времени содержит операционный усилитель 1, первый диодный мост 2, балансные резисторы 3 и 4, резистор 5, .конденсатор 6, формирующие времязадающую КС-цепь, однонаправленная диагональ первого диод ного моста через балансные резистор 3 и 4 подключена между шинами источ ника питания, непроводящая диагонал диодного моста 2 подключена к выход операционного усилителя 1 и через нагрузочный резистор 7 к общей шине ключевой блок 8, второй диодный мост 9, однонаправленная диагональ которого -через балансные резисторы 10 и 11 подключена между шинами источника питания, третий диодный мост 12, однонаправленная диагональ которого через балансные резисторы 13 и 14 подключена между шинами источника питания, ограничитель 15 напряжения, нормирующий резистор 1 включенный между одним из выводов однонаправленной диагонали первого диодного моста и одним из входов ключевого блока 8, входную клемму 17, вьшод 18 непроводящей диагонали третьего диодного моста, вывод 19 которой соединен с входом операционного усилителя 1, к входу которого подключен вывод 20 непроводяще диагонали моста. 9, вывод 21 соедине с выводом 22 непроводящей диагонали первого, диодного моста 2, вывод 23 которой соединен с выходом оп ационного усилителя 1, входом 24 ограничителя 15 напряжения, выход 25 которого соединен с входом операционного усилителя 1. Нормирующий 134 резистор 16 включен между выходным выводом 26 однонаправленной диагонали первого диодного моста 2 г первым входом 27 ключевого блока 8, а входной вьшод 28 однонаправленной диагонали первого диодного Mocta 2 соединен с первым выходом 29 ключевого блока 8, второй вход 30 которого соединен с клеммой 31 поЛожительной-полярности внешнего источника постоянного напряжения, а второй выход 32 - с выходной клеммой 33 устройства. Рабочий процесс в предлагаемом реле времени представляет собой совокупность пяти режимов работы: исходного нулевого состояния, слежения за изменением текущего значения напряжения -входного сигнала меньше заданного порогового уровня, когда. 12ex |Vnopor«i формирования временной задержки входного сигнала от времени to, когда текущее значение напряжения входного сигнала | Р I i VnopotAl, до t формирования выход.ного сигнала, сигнализирующего об отказе канала управления, восстановления схемы в режим слежения. I . , Режим исходного нулевого состояния. Для простоты описания работы устройства примем значения проходных сопротивлений (в непроводящей диагонали) открытых диодных мостов 2,9 и 12 равными пулю Ссаг.откр 0/, а закрытых -V 00 (enp.ifticp.oo Тогда, при отсутствии напряжения входного сигнала Gg 0 в однонаправленной диагонали диодных мостов ,9 и 12 протекают токи ограничения :3о1, суммарные значения которых будут определяться выражениями °2 :;:щ7 2) ,т .2§ (3) , где dq;, ;3ог,о1 значения токов граничения в однонаправленных иагоналях диодных мостов 2, 9 и 12, 51 Е - значение напряжения источника питания относительно средней точ ки нулевого потенциала. , Rs,,A, R.. номиналы балансных резисторов. При этом в схеме необходимо соблюдение соотношений aov 3 Ль (4) Joi « Напряжения на выходе операционного усилителя 1 2о на нагрузочном резисторе 7, а также токи во входной цепи Jg и цепи обратной связи Зое операционного усилител 1 равны нулю. Разность потенциалов между входным 28 и выходным 26 выводами однонаправленной диагонали первого диод ного моста 2 равна 2 ПР (где trip падение напряжения на открытом диоде) , а ее полярность соответствует закрытому состоянию база-эмиттерног перехода входного транзистора в клю чевом блоке 8, и напряжение сигнала отказа на выходной клемме33 устрой ;ства отсутствует. Режим слежение. Этому режиму соответствует наличие текущего уровня входного напряжения Uey на клемме 17 устройства определяемое им в соответствии с выражением (5) значение выходного 4тока Оцу на входной клемме опера ционного усилителя 1 ВВУ ... RE -bftup-arKp -значение входного тока; -текущее значение напряжения входного сигнала; R -номинал входного ре зистора; пр.откр. -значение проходного сопротивления откры того третьего диодного моста 12. Значение тока в обратной связи Зое в линейном режиме работы опера ционного усилителя 1 однозначно свя зано с значением входного тока ОЙУ соотношением - Пос. С учетом принятых Допущений, что открытых диодных мостов равно нулю, напряжение ot и OQI а следо 3 вательно, и ток в нагрузочном резисторе 7 равны нулю. - Конденсатор 6 зашунтирован нулевым проходным сопротивлением непроводящей диагонали-ДИОДНОГО моста 9 (выводы 20 и 21), что определяет заданньй режим слежения как режим арречирования для интегратора. Режим формирования временной задержки входного сигнала. При достижении текущим значением ь-апряжения входного сигнала заданного порогового уровня, при котором вьтолняется равенство Зое 3 происходит запирание второго диодного Моста 9 и его проходное сопроRHPтивление Rno а операционный усилитель 1 из режима арретирования переходит в режим интегрирования. Значение тока ограничения ог выбирается несколько большим тока 3 с тем, расчетом, чтобы вызвать надежное запирание второго диодного моста 9 и в то же время минимально влиять на скорость заряда конденсатора 6 при возрастании напряжения входного сигнала 5вк от значения VnopoPA ДО своего максимально возможного значения 7 ч/ 1-|Зо,1й5): с момента to, когда операционный усилитель 1 из режима арретирования переходит в режим интегрирования, изменение напряжений 1 и 1 опрееляется вьфажением ;e((ao.-3oz). (7) где DQ J(yj - токи ограничения третьего 12 и второго 9 диод ньк мостов, . заданное значение временной задержки сигнала отказа канала управления i Cj - номинал емкости конденсатора 6. Текущему изменению значения наряжения на выходе операционного силителя 1 соответствует значение ыходного тока Og, , определяемое выажением

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство контроля напряжения | 1980 |

|

SU991318A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-08-30—Публикация

1981-01-09—Подача