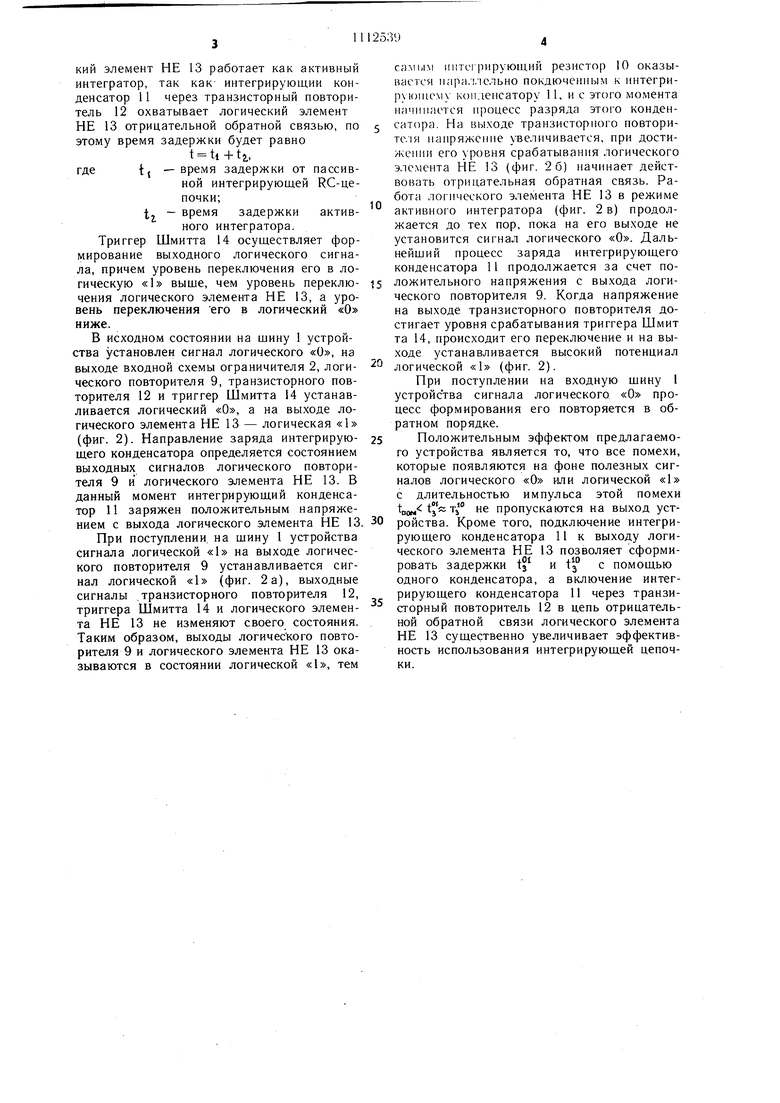

kl3(jGpeTeHHe относится к импульсной тех пике, в частности к формирователям им11ул1 со з с подавлением кратковременных помех, и может быть использовано в вычислительной технике и автоматике. Известно устройство подавления помех содержащее логические элементы НЕ и интегрирующие цепочки, состоящие из резистора и конденсатора 1. Недостатками данного устройства являются наличие двух интегрирующих цепочек и сложность получения длительных задержек. Наиболее близким по технической сущности к изобретению /является устройство, содержащее последовательно соединенные триггер Шмитта, интегрирующую цепочку, а также схему ограничения входного сигнала, в которую входят диод, резисторы и стабилитроны 2. Недостатком известного устройства является низкая помехоустойчивость при логической «1 на его входе. Это Объясняется различием постоянных времен для зарядной и разрядной цели, так как при закры том разрядном диоде резистор интегрирующей цепи отключен от входной схемы формирования и выполняет только функцию заряда емкости, а при открытом разрядном диоде образуется цепь разряда емкости, но кроме-того должно выполниться условие обеспечения подачи напряжения логического «О на вход триггера Шмитта. Это условие соблюдается только в том случае, если резистор, через который разряжается емкость, будет на порядок и более меньще резистора интегрирующей цепи. Тем самым помехоустойчивость для входного сигнала логического «О и логической «1 сильно отличается. Цель изобретения - повышение помехоустойчивости устройства. Поставленная цель достигается тем, что в устройство для подавления помех, содержащее ограничитель входного сигнала, вход которого соединен с входной щиной, последовательно соединенные резистор и конденсагор интегрирующей цепи и триггер Шмит та. введены транзисторный и логический повторители и элемент НЕ, причем выход ограничителя входного сигнала через последовательно соединенные логический повторитель и резистор интегрирующей цепи соединен с входом транзисторного повторителя, выход которого через элемент НЕ соединен с второй обкладкой конденсатора интегрирующей цепи, выход транзисторного повторителя соединен с входом триггера Шмитта, выход которого является выходной щиной устройства. На фиг. 1 представлена функциональная схема устройства подавления помех; на фиг. 2 - временная диаграмма его работы. Устройство содержит входную щину 1, ограничитель 2 входного сигнала, состоящий из первого резистора 3, соединенного с анодами первого 4 и второго 5 стабилитронов, катод второго стабилитрона через второй резистор 6 соединен с щиной нулевого потенциала и через диод 7 и третий резистор 8 - с щиной источника питания, катод первого стабилитрона соединен с щиной нулевого потенциала, анод диода через логический повторитель 9 и резистор 10 интегрирующей цепи - с первой обклад кой конденсатора 11 интегрирующей цепи и через транзисторный повторитель 12 и элемент НЕ 13 с второй обкладкой конденсатора интегрирующей цепи, выход транзисторного повторителя через триггер 14 Шмитта соединен с выходной щиной 15. Устройство работает следующим образом. Входная схема ограничителя 2 осуществляет согласование поступающего сигнала на входную щину 1 с уровнем входного напряжения логического повторителя 9. Ограничение входного сигнала по верхнему уровню производится стабилитроном 4, а по нижнему уровню - стабилитроном 5. Ограниченный входной сигнал по верхнему и нижнему уровню выделяется на резисторе 6 и прикладывается к катоду диода 7, а к аноду этого диода через резистор 8 прикладывается напряжение Ч-иц Если на щину 1 устройства приложить положительное напряжение, равное Ик-Ис,. + И„, то диод 7 полностью закрыт и все напряжение + И„ через резистор 8 приложено к входу логического повторителя 9, который в свою очередь сформирует сигнал логической «1. Если на вход устройства подать положительное напряжение, равное .,, то вход логического повторителя через диод 7 замкнут на резистор 6, и тем самым на его входе устанавливается нааряжеиие логического «0. Формирование задержки сигнала в устройстве подавления помех осуществляется интегрирующей R С-цепочкой из резистора 10 и конденсатора 11 логическим элементом НЕ 13 и транзисторным, повторителем 12. Логический элемент НЕ 13 предназначен для подключения обкладки интегрирующего конденсатора 11 к -|-И„ или к общей щине питания, таким образом, при поступлении с логического повторителя сигнала логического «О или логической «1 перезаряд интегрирующего конденсатора происходит по одним и тем же цепям. Кроме того, в зоне своего переключения логический элемент НЕ 13 работает как активный интегратор, так как- интегрирующий конденсатор 11 через транзисторный повторитель 12 охватывает логический элемент НЕ 13 отрицательной обратной связью, по этому время задержки будет равно t ti+ti, где{ -время задержки от пассивной интегрирующей RC-цепочки;i - время задержки активного интегратора. Триггер Шмитта 14 осуществляет формирование выходного логического сигнала, причем уровень переключения его в логическую «1 выше, чем уровень переключения логического элемента НЕ 13, а уровень переключения его в логический «О ниже. В исходном состоянии на щину 1 устройства установлен сигнал логического «О, на выходе входной схемы ограничителя 2, логического повторителя 9, транзисторного повторителя 12 и триггер Шмитта 14 устанавливается логический «О, а на выходе логического элемента НЕ 13 - логическая «1 (фиг. 2). Направление заряда интегрирующего конденсатора определяется состоянием выходных сигналов логического повторителя 9 и логического элемента НЕ 13. В данный момент интегрирующий конденсатор 11 заряжен положительным напряжением с выхода логического элемента НЕ 13 При поступлении, на шину 1 устройства сигнала логической «1 на выходе логического повторителя 9 устанавливается сигнал логической «1 (фиг. 2 а), выходные сигналы транзисторного повторителя 12, триггера Шмитта 14 и логического элемента НЕ 13 не изменяют своего состояния. Таким образом, выходы логического повторителя 9 и логического элемента НЕ 13 оказываются в состоянии логической «1, тем самым интегрирующий резистор 10 оказывается паря.ьчсльно покдюченным к ннтегрирукинему конденсатору 11, и с этого момента нгпщпастея процесс разряда этого конденсатора. На выходе транзисторного повториТС1Я панряжсмие увеличивается, при достижении его уровня срабатывания логического элемента НЕ 13 (фиг. 26) начинает действовать отрицательная обратная . Работа логического элемента НЕ 13 в режиме активного интегратора (фиг. 2 в) продолжается до тех пор, пока на его выходе не установится сигнал логического «О. Дальнейший процесс заряда интегрирующего конденсатора 11 продолжается за счет положительного напряжения с выхода логического повторителя 9. Когда напряжение на выходе транзисторного повторителя достигает уровня срабатывания триггера Шмит та 14, происходит его переключение и на выходе устанавливается высокий потенциал логической «1 (фиг. 2). При поступлении на входную щину 1 устройства сигнала логического «О процесс формирования его повторяется в обратном порядке. Положительным эффектом предлагаемого устройства является то, что все помехи, которые появляются на фоне полезных сигналов логического «О или логической «1 с длительностью импульса этой помехи to(iK tjs; Tj не пропускаются на выход устройства. Кроме того, подключение интегрирующего конденсатора 11 к выходу логического элемента НЕ 13 позволяет сформировать задержки tj и tj с помощью одного конденсатора, а включение интегрирующего конденсатора 11 через транзисторный повторитель 12 в цепь отрицательной обратной связи логического элемента НЕ 13 существенно увеличивает эффективность использования интегрирующей цепочки. В;(од -/- /--Д 5 T-Z: „1:гт г : - Выход

Фиг.2 По/iexa /

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕКТРОННАЯ СИСТЕМА ЗАЖИГАНИЯ | 1992 |

|

RU2078246C1 |

| Многоканальное устройство согласования коммутационной цепи переменного тока с интегральной микросхемой | 1984 |

|

SU1307552A1 |

| Формирователь импульсов | 1980 |

|

SU869003A1 |

| ЭЛЕКТРОННАЯ СИСТЕМА | 1996 |

|

RU2103796C1 |

| Релаксационный формирователь импульсов | 1977 |

|

SU734871A1 |

| Одновибратор | 1978 |

|

SU733088A1 |

| СТАБИЛИЗИРОВАННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ | 2014 |

|

RU2541519C1 |

| Устройство для автоматического контроля герметичности | 1987 |

|

SU1464094A1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ПИКОВЫЙ ДЕТЕКТОР | 2019 |

|

RU2708687C1 |

| Транзисторный генератор -образного напряжения | 1975 |

|

SU738123A1 |

УСТРОЙСТВО ДЛЯ ПОДАВЛЕНИЯ ПОМЕХ, содержащее ограничитель входного сигнала, вход которого соединен с входной шиной, последовательно соединенные резистор и конденсатор интегрирующей цепи и триггер Шмитта, отличающееся тем, что, с целью повыщения его помехоустойчивости, в него введены транзисторный и логический повторители и элемент НЕ, причем выход ограничителя входного сигнала через последовательно соединенные логический повторитель и резистор интегрирующей цепи соединен с входом транзисторного повторителя, выход которого через элемент НЕ соединен с второй обкладкой конденсатора интегрирующей цепи, выход транзисторного повторителя соединен с входом триггера Шмитта, выход которого является выходной щиной устройства. (П Фиг.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| КРОМКООБРЕЗНЫЕ НОЖНИЦЫ | 2009 |

|

RU2419521C2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Формирователь импульсов | 1980 |

|

SU869003A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-09-07—Публикация

1983-05-11—Подача