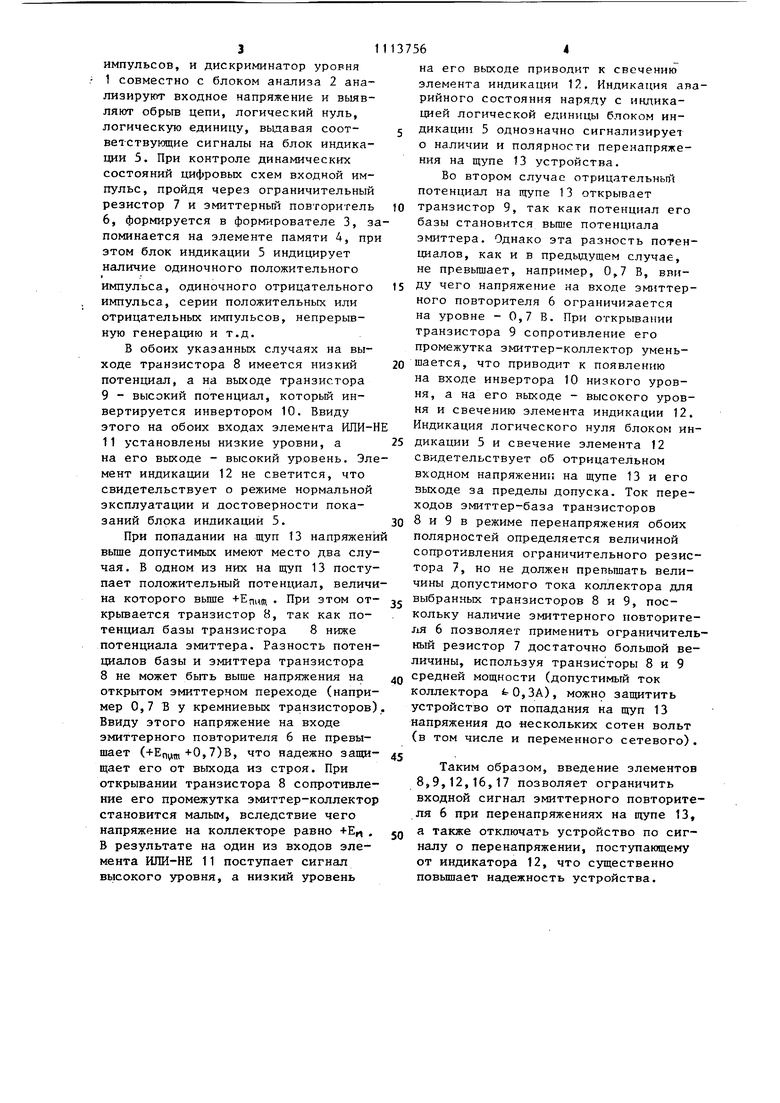

1 Изобретение относится к автоматик и вычислительной технике и может най ти применение при разработке, наладке и ремонте цифровьсх измеритель11ых устройств и ЭВМ. Известно устройство для контроля логических состояний цифровых схем, содержащее логический блок, блок индикации, формирователь импульсов, элемент памяти и инвертор 11. Недостатком известного устройства является его недолговечность, ввиду отсутствия защиты от аномального вхо ного сигнала превышающего допустимое значение. Наиболее близким к изобретению является устройство для контроля логических состояний цифровых схем содержащее ограничительный резис тор, элемент ИЖ-НЕ, инвертор, щуп, клеммы для подключения положительно и отрицательного выводов источника питания, соединенные с соответствующими выводами питания эмиттерного повторителя, блока анализа, блока и дикации, элемента памяти, формирователя импульсов и дискриминатора уро ней, соединенного входом с входом формирователя импульсов, выход кото рого соединен через элемент памяти с первым входом блока индикации, со диненного вторым входом через блок анализа с выходом дискриминатора уровней 23. Недостатком такого устройства является низкая надежность, обуслов ленная тем, что попадание на вход устройства напряжений больше допуст мых приводит к отказу его входных блоков, поскольку вход устройства в этом случае не отключается от кон ролируемой цифровой схемы. Цель изобретения - повьшение надежности устройства. Поставленная цель достигается те что в устройство для контроля логических состояний цифровых схем, содержащее ограничительный резистор, элемент ИЛИ-НЕ, инвертор, щуп, клем мы для подключения положительного и отрицательного выводов источника питания, соединенные с соответствующими выводами питания эмиттерного повторителя, блока анализа, блока индикации, элемента памяти, формирователя импульсов и дискриминатора уровней, соединенного входом с входом формирователя импульсов, выход 62 которого соединен через элемент памяти с первым входом блока индикации,i соединенного вторым входом через блок анализа с вькодом дискриминатора уровней, введены первый и второй резисторы, первьй и второй транзисторы, соединенные эмиттерами чераз ограничительный резистор с щупом, через эмиттерньй повторитель с входом дискриминатора уровня, базами-соответственно с клеммами для подключения положительного и отрицательного выводов источника питания, коллекторами соответственно через первый и второй резисторы - с клеммами для подключения положительного и отрицательного выводов источника питания, первый вход элемента ИЛИ-НЕ соединен с коллектором первого транзистора, второй вход через инвертор - с коллектором второго транзистора, выход с входом элемента индикации, соединенного выходом с клеммой для подключе-г ния положительного вывода источника питания. На чертеже приведена блок-схема устройства. Устройство содержит дискриминатор уровней 1, блок анализа 2, формирователь импульсов 3, элемент памяти 4. блок индикации 5, эмиттерный повторитель 6, ограничительной резистор 7, первый 8 и второй 9 транзисторы, инвертор 10, элемент ИЛИ-НЕ 11, элемент индикации 12, щуп 13, клеммы для подключения отрицательного 14 и положительного 15 выводов источника питания, первый 16 и второй 17 резисторы. Устройство работает следующим образом. В режиме нормальной эксплуатации, когда напряжение на щупе 13 находится в пределах 0-(+Rnum 5 транзисторы 8 и 9 заперты. Падение напряжения от нормального входного сигнала на ограничительном резисторе 7 способствует надежному запиранию транзисторов 8 и 9, так как их базовые выводы подключены к клеммам 14 и 15, имеющим соответственно потенциалы О и +Епут Входной сигнал поступает полностью на эмиттерный повторитель 6, а с его вь1хода - на вход дискриминатора уровня 1 и вход формирователя импульсов 3. При контроле статических состояний цифровых схем формирователь импульсдв 3 не вырабатьшает

импульсов, и дискриминатор уровня

Iсовместно с блоком анализа 2 анализируют входное напряжение и выявляют обрыв цепи, логический нуль, логическую единицу, выдавая соответствунлцие сигналы на блок индикации 5. При контроле динамических состояний цифровых схем входной импульс, пройдя через ограничительный резистор 7 и эмиттерньш повторитель 6, формируется в формирователе 3, запоминается на элементе памяти А, при этом блок индикации 5 индицирует наличие одиночного положительного импульса, одиночного отрицательного импульса, серии положительных или отрицательных импульсов, непрерывную генерацию и т.д.

В обоих указанных случаях на выходе транзистора 8 имеется низкий потенциал, а на выходе транзистора 9 - высокий потенциал, который инвертируется инвертором 10. Ввиду этого на обоих входах элемента ИЛИ-НЕ

IIустановлены низкие уровни, а на его выходе - высокий уровень. Элемент индикации 12 не светится, что свидетельствует о режиме нормальной эксплуатации и достоверности показаний блока индикации 5.

При попадании на щуп 13 напряжений выше допустимых имеют место два случая . В одном из них на щуп 13 поступает положительный потенциал, величина которого вьше +Епи(ц . При этом открывается транзистор 8, так как потенциал базы транзистора 8 ниже потенциала эмиттера. Разность потенциалов базы и эмиттера транзистора 8 не может быть выше напряжения на открытом эмиттерном переходе (например 0,7 Б у кремниевых транзисторов) Ввиду этого напряжение на входе эмиттерного повторителя 6 не превышает (+ЕП |Щ-0,7)В, что надежно защищает его от выхода из строя. При открывании транзистора 8 сопротивление его промежутка эмиттер-коллектор становится малым, вследствие чего напряжение на коллекторе равно +Еи . В результате на один из входов элемента ИЛИ-НЕ 11 поступает сигнал высокого уровня, а низкий уровень

на его выходе приводит к свечению элемента индикации 12. Индикация аварийного состояния наряду с индикацией логической единицы блоком индикации 5 однозначно сигнализирует о наличии и полярности перенапряжения на щупе 13 устройства.

Во втором случае отрицательный потенциал на щупе 13 открывает транзистор 9, так как потенциал его базы становится выше потенциала эмиттера. Однако эта разность потенциалов, как и в предьвдущем случае, не превьщ1ает, например, 0,7 В, ввиду чего напряжение на входе эм}1ттерного повторителя 6 ограничигается на уровне - 0,7 В. При открывании транзистора 9 сопротивление его промежутка эмиттер-коллектор уменьшается, что приводит к появлению на входе инвертора 10 низкого уровня, а на его выходе - высокого уровня и свечению элемента индикации 12. Индикация логического нуля блоком индикации 5 и свечение элемента 12 свидетельствует об отрицательном входном напряжении на щупе 13 и его выходе за пределы допуска. Ток переходов эмиттер-база транзисторов 8 и 9 в режиме перенапряжения обоих полярностей определяется величиной сопротивления ограничительного резистора 7, но не должен превышать величины допустимого тока коллектора для выбранных транзисторов 8 и 9, посКОЛЬКУ наличие эмиттерного повторителя 6 позволяет применить ограничительный резистор 7 достаточно большой величины, используя транзисторы 8 и 9 средней мощности (допустимый ток коллектора tO,3A), можно защитить устройство от попадания на щуп 13 напряжения до нескольких сотен вольт (в том числе и переменного сетевого). Таким образом, введение элементов 8,9,12,16,17 позволяет ограничить входной сигнал эмиттерного повторителя 6 при перенапряжениях на щупе 13, а также отключать устройство по сигналу о перенапряжении, поступающему от индикатора 12, что существенно повьшает надежность устройства.

/J 7

| название | год | авторы | номер документа |

|---|---|---|---|

| Индивидуальный радиометр-индикатор | 1990 |

|

SU1795396A1 |

| Импульсный зонд для контроля цифровых схем | 1982 |

|

SU1093994A1 |

| НЕСИММЕТРИЧНЫЙ ТРИГГЕР | 2020 |

|

RU2743452C1 |

| Логический пробник | 1983 |

|

SU1132268A1 |

| Устройство для передачи телеграфного сигнала | 1980 |

|

SU1202067A1 |

| УНИВЕРСАЛЬНЫЙ ПРОБНИК | 1991 |

|

RU2022272C1 |

| Формирователь импульсов | 1980 |

|

SU886225A1 |

| Импульсный зонд для контроля цифровых схем | 1978 |

|

SU788054A1 |

| ЛОГИЧЕСКИЙ ТЕСТЕР | 1997 |

|

RU2133475C1 |

| Функциональный преобразователь | 1985 |

|

SU1322326A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ СОСТОЯНИЙ ЦИФРОВЬК СХЕМ, содержащее ограничительный резистор, элемент ИЛИ-НЕ, инвертор, щуп, клеммы для подключения положительного и отрицательного выводов источника питания, соединенные с соответствующими выводами питания эмиттерного повторителя, блока анализа, блока индикации, элемента памяти, фopмIipoвателя импульсов и дискриминатора уровней, соединенного входом с входом формирователя импульсов, выход которого соединен через элемент памяти с первым входом блока индикации, соединенного вторым входом через блок анализа с выходом дискриминатора уровней, отличающееся тем, что, с целью повьшения надежности устройства, в него введены первый и второй резисторы, первый и второй транзисторы, соединенные эмиттерами через ограничительный резистор с щупом, через эмиттерный повторитель - с входом дискриминатора уровня, базами - соответственно с клеммами для подключения положительного и отрицательного выводов источника питания, коллекторами соответственно через первый и второй (Л резисторы - с клеммами для подключес ния положительного и отрицательного выводов источника питания, первый вход элемента ИЛИ-НЕ соединен с коллектором первого транзистора, второй вход через инвертор - с коллектором второго транзистора,, выход - с входом элемента индикации, соединен00 ного выходом с клеммой для подклю ел чения положительного вывода источника питания. 35

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Логический зонд | 1976 |

|

SU612412A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Пробник в составе комплекта испытательных тестеров КИТ, Техническое описание, 1981 (прототип) | |||

Авторы

Даты

1984-09-15—Публикация

1982-04-23—Подача