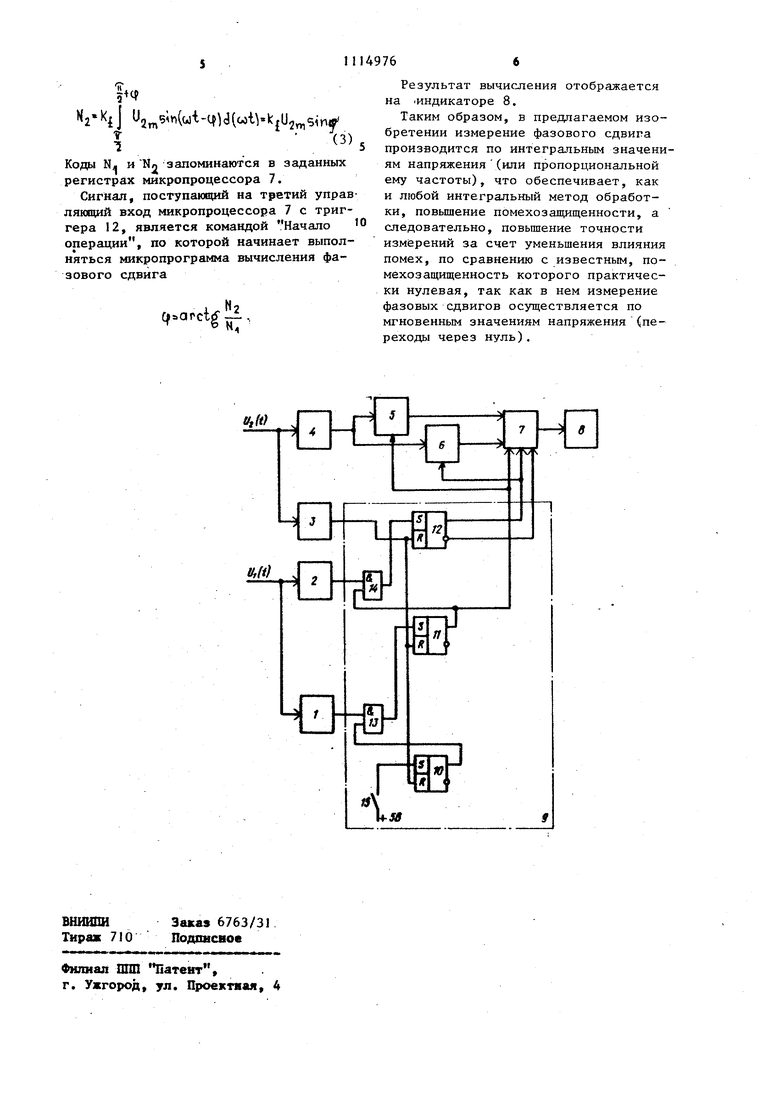

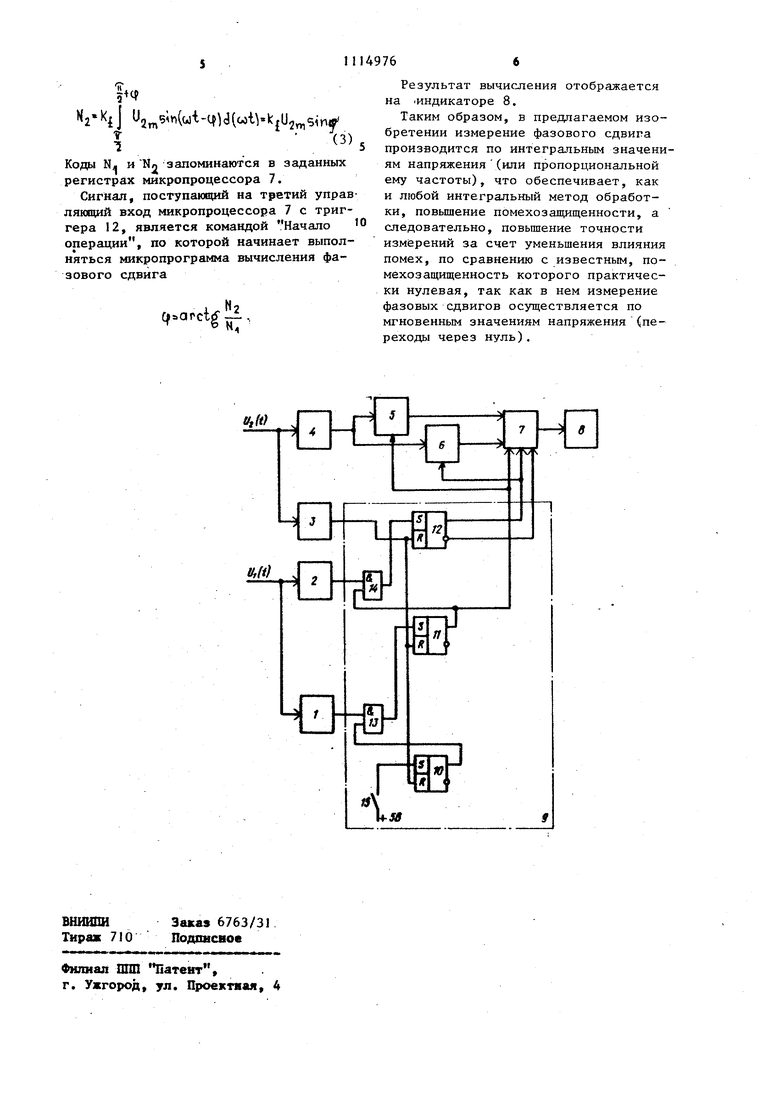

Изобретение относится к измеритель ной технике и может быть использовано при создании фазометрической аппаратуры. Известно цифровое устройство для измерения мгновенного значения сдвига фаз, которое состоит из блока фор мирования интервалов времени, равных периоду и сдвигу фаз исследуемых сиг налов, ключа периода, ключа фазы,клю ча счетчика импульсов периода,счетчи ков импульсов сдвига фаз, общего счетчика, регистрирующего счетчика, генератора опорной частоты, делителя частоты, двух блоков совпадения, бло ка управления, блока индикации, сбор ки ключей I Q Недостатками этого устройства являются большая сложность аппаратурной реализации, недостаточное быстро действие и низкая точность измерения Наиболее близким к изобретению является цифровой фазометр мгновенных значений, содержащий блок формирования сигналов (нуль-орган), два элемента И, первые входы которых соединены с выходом генератора опорного напряжения (формирователя опорной частоты), а вторые входы - с блоком формирования сигналов, счестчики импульсов периода и сдвига фаз, входы которых соединены с выходами элементов И, блок управления и последова-; тельно соединенные коммутатор, микро процессор и индикатор, причем выходы счетчиков соединены с сигнальными входами коммутатора, а выходы бло ка управления соединены с входами уп равления блока форьшрования сигналов коммутатора, микропроцессора и индикатора 23. . Однако известный фазометр обладает невысокой точностью за счет низкой п мехозащищенности вьщеления временных интервалов по мгновенным значениям входных напряжений - по переходам че рез нуль. Целью изобретения является повышение точности измерений путем уменьшения влияния помех. Поставленная цепь достигается тем, что в фазометр, содержащий нуль-орган, включенный между первым входом фазометра и входом блока управления f соединенного через микропроцессор о индикатором, и два элемента И, первые входы жоторых соединены с формирователем опорной частоты дополнительно введены два временных дискриминатора максимумов, при этом первый временной дискриминатор максимумов включен между первым входом фазометра и вторым входом блока управления, вход второго временного дискриминатора максимумов соединен с вторым входом фазометра и входом формирователя опорной частоты, а выход с третьим входом блока управления, два выхода которого подсоединены к вторым входам элементов И, выходы которых соединены с входами микропроцессора. Кроме того, блок управления выполнен в виде двух элементов И, трех триггеров и кнопки Пуск, при этом первые входы элементов И соединены с выходами второго дискриминатора максимумов и нуль-органа, вторые - с выходами соответственно первого и вто-рого триггеров, выход первого элемента И соединен с единичным входом пернего триггера, а выход второго - с единичным входом третьего триггера, при этом нулевые входы всех триггеров объединень и подсоединены к выходу первого временного дискриминатора максимумов, единичный вход второго триггера соединен с кнопкой Пуск, выхода первого и третьего триггеров являются выходами блока управления . На чертеже приведена блок-схема фазометра. В состав фазометра входят нуль-орган I, временные дискриминаторы 2 и 3 максимумов, формирователь 4 опорной частоты, элементы И 5 и 6, микропроцессор 7, индикатор 8 и блок 9 управления. Блок 9 управления содержит триггеры 10 - 12, элементы И 13 и 14 и кнопку 15 Пуск. Входы нуль-органа I и первого временного дискриминатора 2 максимумов объединены между собой и подключены к первому входу прибора. Входы второго временного дискриминатора 3 максимумов и формирователя 4 опорной частоты объединены между собой и подключены к второму входу прибора. Формирователь 4 через элементы И 5 и 6 соединен с двумя информационными входами микропроцессора 7, подключенного к индикатору 8. Выход нуль-органа 1 соединен с первым входом элемента И 13, ЯВЛЯЮ1ЦИМСЯ первым входом блока-9 управления. Второй вход эле31

мента И 13 подключен, к выходу триггера 10, единичный вход которого соединен с кнопкой 15 Пуск. Выход элемента И 13 подключен к единичному входу триггера 11. Выход первого временного дискриминатора 2 максимумов соединен с первым входом элемента И 14, являкицимся вторым входом блока 9 управления. Второй вход элемента И 14 соединен с точкой, объединяющей выход триггера 11, управляющий вход элемента И 5 и первый управляющий вход микропроцессора 7 и представляющей первый выход блока 9 управления . Выход элемента И I4 подключен к единичному входу триггера 12. Нулевые входы триггеров 10 - 12 объединены между собой, представляют третий вход блока 9 управления и соединены с выходом второго временного дискриминатора 3 максимумов. Единич-т ный выход триггера 12 представляет второй выход блока 9 управления, который подключен к управляющему входу элемента И 6 и второму управляющему входу микропроцессора 7. Нулевой выход триггера 12 является третьим выходом блока 9 управления, который подключен к третьему управлякяцему входу микропроцессора 7.

Фазометр работает следующим образом.

Пусть синусоидальные напряжения, между которыми измеряется фазовый сдвиг,

U,(tbU 6incot ,5iniu)t-Cfi ,

подаются соответственно на первый и второй вход прибора.

Нуль-органом 1 вьщеляются переходы напряжения U (t) через нуль, а временным дискриминатором 2 - переходы этого напряжения через максимум.Временным дискриминатором 3 выделяются моменты переходов через максимукш напряжения U (t). В эти моменты времени формируются управляющие сигналы, поступающие в блок 9 управле-« ния. Формирователем 4 осуществляется преобразование напряжения U (t) в пропорциональную частоту следования импульсов

iiii l f lllWXi h, ( где K - коэффициент передач формирователя 4 опорной частоты.

14976 .4

Элементы И 5и 6 в исходном состоя-. НИИ закрыты соответствующими потенциалами триггеров 11 и 12 соответственно блока 9 управления. 5 При нажатии кнопки 15 Пуск опрокидывается триггер 10 и подготавливает к работе элемент Н..13. Первый же импульс с вькода нуль-органа 1 проходит через этот элемент и перёво10 дит в единичное состояние триггер 11, выходным потенциалом которого переводятся в рабочее состояние элемент И 5 и элемент И 14. Импульсы с выхода формирователя 4 начинают поступать

IS в один из запоминающих регистров

ьеткропроцессора 7, адрес которого выбирается по управлякицему сигналу с триггера 11. С поступлением сигнала временного дискриминатора 2 максиму0 мов на элемент И 14 опрокидывается триггер 12, который открывает своим потенциалом элемент И 6 и задает адрес второго регистра микропроцессора 7 для записи импульсов, поступаюпщх 5 с формирователя -4 через элемент И 6. Сигнал с выхода временного дискриминатора 3 максимумов поступает на нулевые входы триггеров 10 - 12, возвращая их в исходное состояние.

0 Тем элементы И 5 и 6 становятся нечувствительными к импульсам формирователя 4, прекращая их доступ в микропроцессор 7. С нулевого выхода триггера 12 поступает сигнал на

5 третий управляющий вход микропроцессору 7.

Таким образом, элемент И 5 оказывается открытым для прохождения импульсов в течение фазового шггервала О f -f

(Jii- -Kf), a элемент И 6 - в течение

it

фазового интервала - ).

За время открытого состояния элемента И 5 и 6 на соответствуюпще регист5 ры микропроцессора 7 поступает соответственно количество импульсов

i

V ГН

r,.j Jt)d(ut)k:J mi)d(ut),

j+Cf O. .4.(

ЧЛ b-k u.zit)d(ut).

It

Подставляя в эти формулы выражение (l)i получаем

« |

-H,i;jJ V5(()5 coecf,M)

Ъ

2XiJ

(3)

5 5

Коды N. и Nj эапоминаются в заданных регистрах микропроцессора 7,

Сигнал, поступающий на третий управляющий вход микропроцессора 7 с триггера 12, является командой Начало операции, по которой начинает выполняться микропрограмма вычисления фазового сдвига

Cj.arcl.

Результат вычисления отображается на Индикаторе 8.

Таким образом, в предлагаемом изобретении измерение фазового сдвига производится по интегральным значениям напряжения(или пропорциональной ему частоты), что обеспечивает, как и любой интегральный метод обработки, повышение помехозащищенности, а следовательно, повьшение точности изм1ерений за счет уменьшения влияния помех, по сравнению с известным, помехозащищенность которого практически нулевая, так как в нем измерение фазовых сдвигов осуществляется по мгновенным значениям напряжения (переходы через нуль).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1986 |

|

SU1368808A1 |

| Цифровой одноканальный инфранизкочастотный фазометр | 1987 |

|

SU1472831A1 |

| Цифровой анализатор частотных характеристик линейных четырехполюсников | 1985 |

|

SU1315946A1 |

| Устройство для контроля угловых положений элементов периодических структур осесимметричных деталей | 1989 |

|

SU1789850A1 |

| Генератор-фазометр инфранизких частот | 1977 |

|

SU690406A1 |

| СПОСОБ ДИАГНОСТИКИ СОСТОЯНИЯ БИООБЪЕКТА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1994 |

|

RU2118121C1 |

| Цифровой фазометр | 1988 |

|

SU1638654A1 |

| Цифровой фазометр | 1987 |

|

SU1420547A1 |

| Устройство для измерения угловых положений несплошностей или элементов формы деталей вращения | 1974 |

|

SU572645A1 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

1. ЦИФРОВОЙ ФАЗОМЕТР, содержащий нуль-орган, включенный между перым входом фазометра и входом блока управления, соединенного через микропроцессор с индикатором, и два элемента И, первые входы которых соединены с формирователем опорной частоты, отличающийся тем, что, с целью повьшения точности путем уменьшения влияния помех, в него дополнительно введены два временных дискриминатора максимумов, при этом первый временной дискриминатор максимумов включен между первым входом фазометра и вторым входом блока управления, вход второго временного дискриминатора максимумов соединен с втоВСЕ€ОЮЗ ;АЯ .. T 5f -;t:v f,i,; шы-т ш, рым входом фазометра и входом формирователя опорной частоты, а выход - с третьим входом блока управления, два выхода которого подсоединены к вторым входам элементов И выходы кртерых соединены с входами микропроцессора. 2. Фазометр по п.1. отличающийся тем, что блок управления в нем выполнен в виде двух элементов И, трех триггеров и кнопки Пуск, при этом первые входы элементов И соединены с выходами второго дискриминатора максимумов и нуль-органа, вторые - с выходами соответственно i первого и второго триггеров, выход первого элемента И соединен с единич(О ным входом первого триггера, а выход второго - с единичным входом третьего триггера, при этом нулевые входы всех триггеров объединены и подсоединены к выходу первого временного дискриминатора максимумов, единичный вход второго триггера соединен .с кноп кой Пуск, выходы первого и третьего триггеров являются выходами блока 4 СО Эд управления.

4-Se

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровое устройство для измерения мгновенного значения сдвига фаз | 1972 |

|

SU441523A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой фазометр мгновенныхзНАчЕНий | 1978 |

|

SU811158A1 |

Авторы

Даты

1984-09-23—Публикация

1982-04-23—Подача