элемента И, выход которого подключен к другому входу первого элемен- та И, стабилизатор тока подключен к

информационному ключа, выход которого подключен к другому входу интегратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1983 |

|

SU1146803A1 |

| Преобразователь угол-фаза-код | 1983 |

|

SU1153335A2 |

| Преобразователь угол-фаза-код | 1985 |

|

SU1254582A1 |

| Преобразователь угол-фаза-код | 1980 |

|

SU858051A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1305858A1 |

| Преобразователь угла поворота вала в код | 1980 |

|

SU942095A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1261116A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU734776A1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1016808A1 |

| Цифровой кондуктометр | 1986 |

|

SU1374144A1 |

1. ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД, содержащий генератор импульсов, подключенный к входу делителя частоты, первый выход которого подключен к первому и второму входам, а второй выход - к третьему входу блока формирования синусоидального тока,, третий выход делителя частоты подключен к первому и второму входам, а четвертый выход к третьему входу блока формирования крсинусоидального тока первые выхода блоков формирования синусоидального и косинусоидального тока подключены к входам формирователя синусоидальных напряжений, выходы которого через усилитель подключены к одни выводам одной и другой перви ный обмоток фазовращателя, другие выводы которых подключены к четвертым входам блоков формирования синусоидального и косинусоидального токов соответственно, выводы вторичной обмотки фазовращателя подключены к входам формирователя импульсов, выходы разрядов делителя частоты подключены к одним входам блока управления, выходы которого подключены к одним вхорам арифметического блока, вторые выходы блоков формирования синусоидального и косинусоидального токов подключены к блоку сравнения амплитуд, выход которого подключен к пятым входам блоков формирования синусои альнр го и косинусоидального токов, отличающийся тем, что, с целью повышения точности преобразователя, в него введены синхронизатор, временной дискриминатор и блок преобразования тока в код, первый выход делителя частоты подключен к первому входу блока преобразования тока в код, выход формирователя импульсов подключен к первым входам синхронизатора и временного дискриминатора, второй и третий входы синхронизатора соединены соответственно с выходом младшего разряда делителя частоты и первым выходом блока преобразования тока в код, а выход подключен к дру«f гому входу блока управления и второму входу временного дискриминатора, второй и третий входы блока преобразования тока в кодсоединены соответственно с пятым выходом делителя частоты и выходом временного дискри-д минатора, а второй выход блока преобразования тока в код подключен к другому входу арифметического блока. 2. Преобразователь по п.1, о т личающийся тем, что блок преобразования тока в код содержит иJ тeгpaтop, компаратор, триггер, перВ1лй и второй злементы И, делитель частоты блока, счетчик, стабилизатор тока и ключ, первый вход блока через делитель частоты блока подключен к первому выходу блока и одному входу первого, элемента И, выход которого через счетчик подключен к второму выходу блока, второй вход блока подключен к синхронизирующему входу триггера и одному входу второго элемента И, третий вход блока подключен к одному входу .интегратор|1, выход которого через компаратор подключен к управляющему входу т риггера, выход триггера подключен к управляющему .входу ключа и другому входу второго

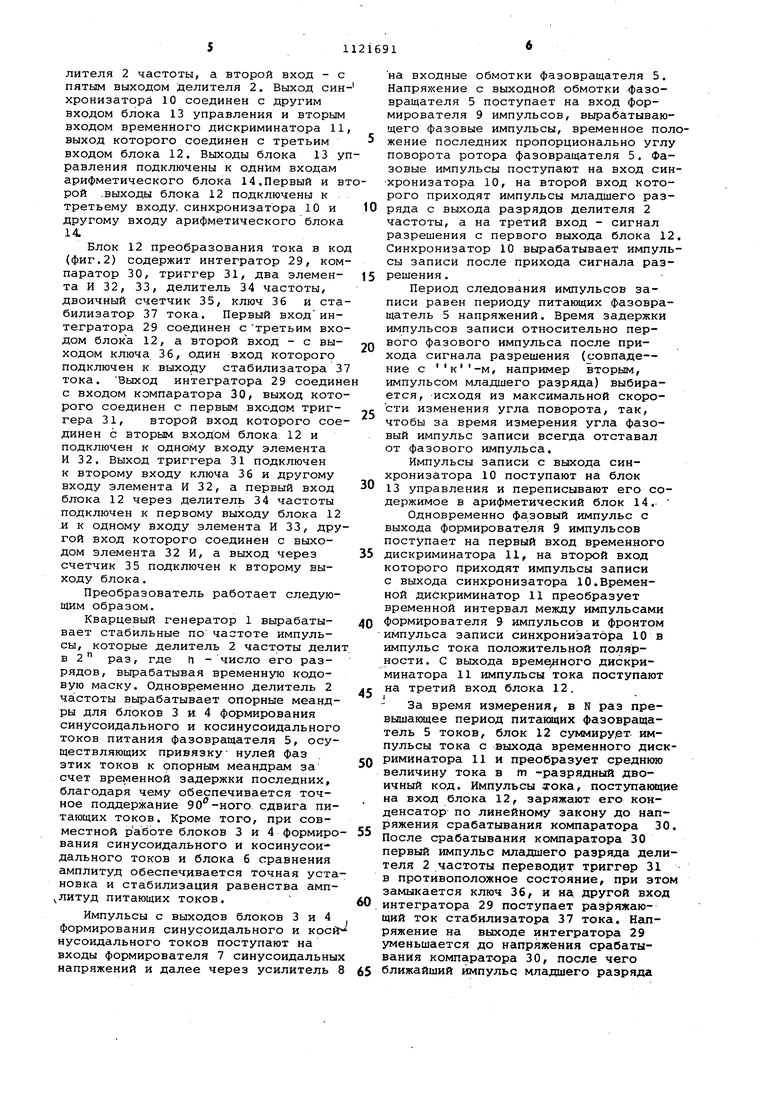

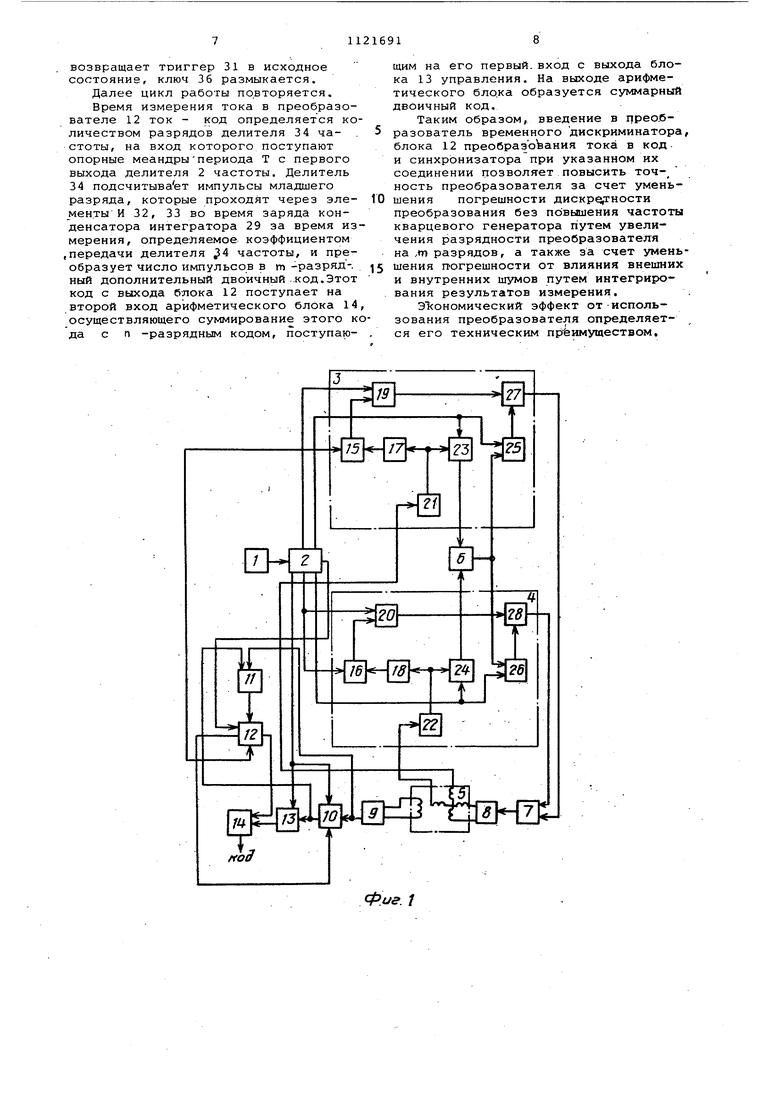

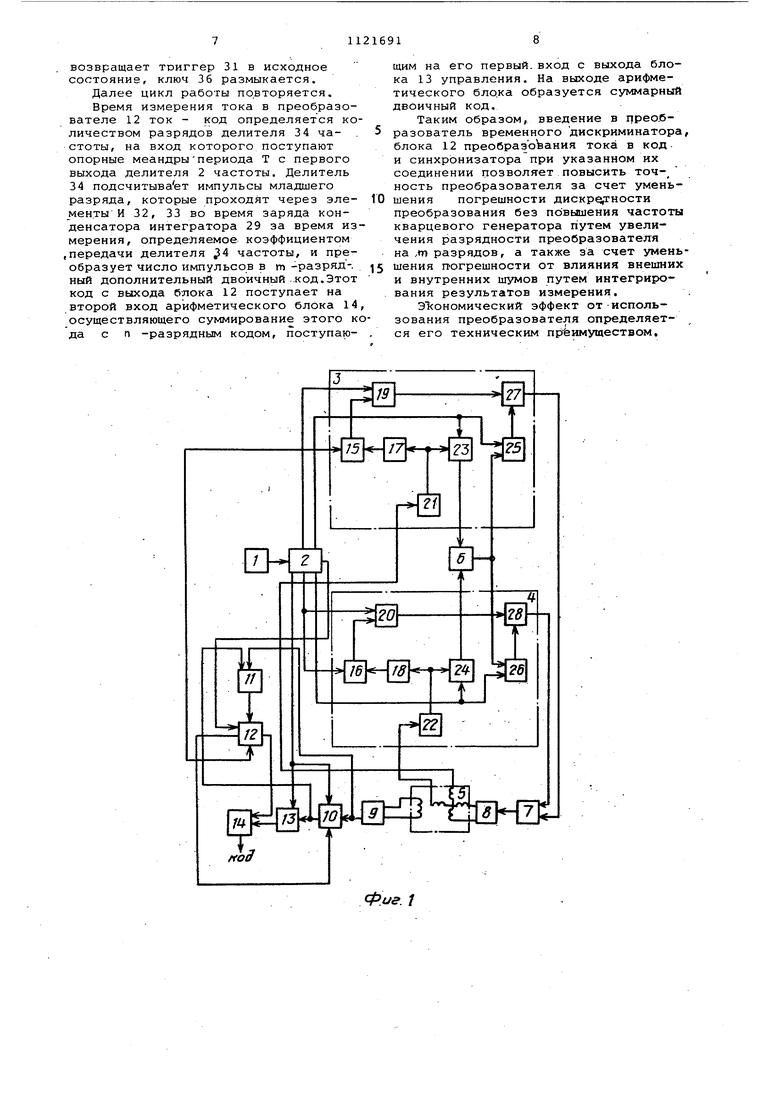

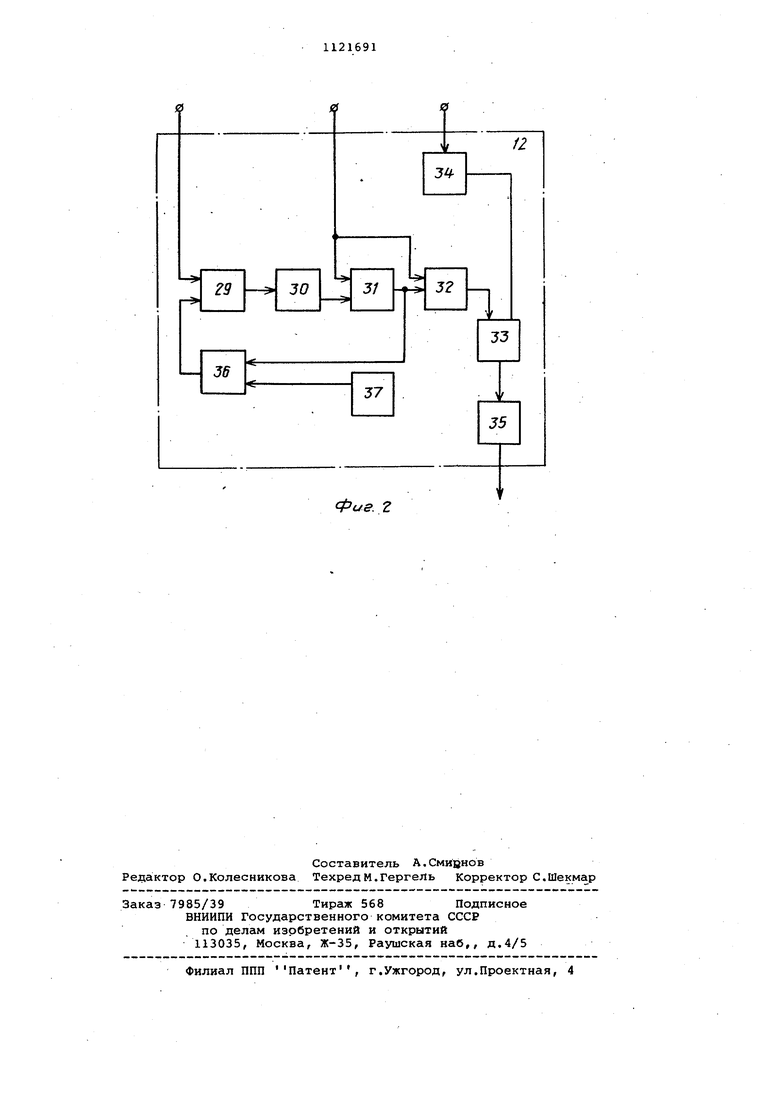

Изобретениеотносится к области автоматики и вычислительной техники и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством Известен преобразователь угол код, содержащий фазовращатель,.блок питания, преобразователь разности фа во временной интервал, генератор импульсов , триггеры, элементы И и два счетчика, один из которых подсчитывает количество импульсов генератора в пачках между старт- и стоп-импульсами, пропорциональное углу поворота, а другой счетчик считает количество пачек, определяющее время измерения угла. В преобразователе производится суммирование мгновенных значений угловых положений, т.е. .интегрирование результатов измерения, что позволяет повысить точность преобразования за счет уменьшения погрешности, вызванной внешними и внутренними шумами l . Недостатком такого преобразователя является погрешность, вызванная неопределенностью расположения старт и стоп-импульсов временного интервала относительно импульсов генератора Известен преобразователь угла поворота вала в код, содержащий блок преобразования урла поворота в последовательность временных интервалов два блока синхронизации, генератор импульсов, счетчик, реверсивный счетчик, интегратор, два компаратора источник эталонного напряжения, дешифратор, восемь триггеров, десять элементов И, четыре элемента ИЛИ, ин вертор с соответствующими связям. Известный преобразователь Интегрирую ще/о типа путем точного измерения концов временных интервалов позволяет практически исключить погрешность дискретности 2j . Недостатком преобразователя является егмэ сложность. Наиболее близким техническим решением к данному .является преобразователь угла поворота вала в код, содержащий генератор импульсов,подключенный к входу делителя частоты, первый выход которого подключен к первому и второму входам, а второй выход - к третьему входу бЛока формирования синусоидального тока, третий выход делителя частоты подключен к первому и второму входам, а четвертый выход --к третьему входу блока формирования косинусоидального тока, первые выходы блоков формирования синусоидального и косинусоидального тока подключены к входам формирователя синусоидальных напряжений, выходы которого через усилитель подключены к одним выводам одной и другой первичных обмоток фазовращателя, другие выводы которых подключены к четвертым входам блоков формирования синусоидального и косинусоидального токов соответственно, выводы вторичной обмотки фазовращателя подключены к входам формирователя импульсов, выходы разрядов делителя частоты подключены к одним входам блока управления, выходы которого подключены к одним входам арифмети ческого блока, вторые выходы блоков формирования синусоидального и косинусоидального токов подключены к блоку сравнения амплитуд, выход которого подключен к пятым входам блоков формирования синусоидального и : косинусоидального токов, выход формирователя импульсов подключен к другому входу блока управления. Каждый из блоков формирования синусоидального и косинусоидального токов содержит компаратор фаз,, формирователь импульсов, два элемента задержки, датчик токов (резистор), ключ, триггер, регулирующий элемент. Блок управления- представляет собой регистр с входными ключами, информационные входы которых соединены с выходами эазрядов делителя частоты, а управляющий вход - с выходом формирователя импульсов 3j . Недостатком известного преобразователя является его невысокая точность, вызванная наличием погрешности дискретности. , Цель изобретения - повышение точности преобразователя. Поставленная цель достигается тем, что в преобразователь угла поворота вала в код, содержащий генератор импульсов, подключенный к входу де- лителя частоты, первый выход которого подключен к первому и второму входам, а второй выход - к третьему входу формирования синусоидального тока, третий выход делителя частоты подключен к первому и второму входам, а четвертый выход - к третьему вход блока формирования косинусоидальног тока, первые выходы блоков формирования синусоидального и косинусоидального тока подключены к входам формирователя синусоидальных напряжений, выходы которого через усилитель подключены к одним выводам одной и другой первичных обмоток фазо вращателя, другие выводы которых по ключены к четвертым входам блоков формирования синусоидального и коси нусоидального токов соответственно, выводы вторичной обмотки фазовращателя подключены к входам формирователя импульсов, выходы разрядов делителя частоты подключены к одним входам блока управления, выходы кот рого подключены к одним входам ариф 1 етического блока, вторые выходы блоков формирования синусоидального и косинусоидального токов подключены к блоку сравнения аплитуд, вЕдход которого подключен к пятым входам блоков формирования синусоидального и косинусоидального токов, введены синхронизатор, временной дискриминатор и блок пре образования тока в код, первый выход делителя частоты подключен к первом входу блока преобразования тока в код, выход формирователя импульсов подключен к первым входам синхронизатора и временного .дискриминатора второй и третий входы синхронизатор соединены соответственно с выходом младшего разряда делителя частоты и первым выходом блока преобразования тока в код, а выход подключен к другому входу блока управления и второму входу временного дискримина тора, второй и третий, входы блока преобразования тока в код соединены соответственно с ПЯТЕЛМ выходом де- л лителя частоты и выходом временного дискриминатора, а второй выход блока преобразования тока в код подключен к другому входу арифметического блока. Блок преобразования тока в код содержит интегратор, компаратор, триггер, первый и второй элементы И делитель . частоты блока, счетчик, стабилизатор тока и ключ, первый вход блока через делитель частоты блока подключен к первому выходу блока и одному входу первого элемен та И, выход которого через счетчик подключен к второму выходу блока, второй вход блока подключен к синхронизирующему входу триггера и одному входу второго элемента И, трети вход блока подключен к одному входу интегратора, выход которого через компаратор подключен к управляющему входу триггера, выход триггера подключей к управляющему входу ключа и другому входу второго элемента И, выход которого подключен к другому входу первого элемента И, стабилизатор тока подключен к информационному входу ключа, выход которого подключен к другому входу интегратора . На фиг.1 представлена структурная схема преобразователя; на фиг.2 структурная схема блока преобразования тока в код. Преобразователь угла поворота вала в код содержит кварцевый генератор 1, делитель 2 частоты,.блоки 5 и 4 формирования синусоидального и косинусоидального токов, фазовращатель 5, блок 6 сравнения амплитуд, формирователь 7 синусоидальных напряжений, усилитель 8, форми- . рователь 9 импульсов, синхронизатор 1U, временной дискриминатор 11, блок 12 преобразования тока в код, блок 13 управления и арифметичес1 йй блок 14. Идентичные по структуре блоки 3 и 4 формирования синусоидального и косинусоидального токов содержат соответственно компараторы 15 и 16 фаз, формирователи 17 и 18 импульсов, управляемые элементы 19 и 20 задержки, датчики 21 к 22 тока, ключи 23 и 24, триггеры 25 и 26 с раздельными входами и регулирующие элементы 27 и 28. Выход кварцевого генератора 1 соединен с входом делителя 2 частоты, к первому выходу которого подключены первый и второй входы, а к второму выходу - третий вход блока 3 формирования синусоидального тока, к третьему выходу делителя 2 часто-ты подключены первый и второй входы, а к его четвертому выходу третий вход блока 4 формирования косинусоидального тока. Четвертые входы блоков 3 и 4 формирования синусоидального и косинусоидального токов соединены с входными обмотками фазовращателя 5, к которым через усилитель 8 подключен выход формирователя 7 синусоидальных напряжений, входы которого соединены с первЕдми выходами блоков 3 и 4 формирования синусоидального и косинусоидального токов. Вторые выходы блоков 4 и 3 соединены с соответствующими входами блока 6 сравнения амплитуд, выход которого подключен к пятым входам этих блоков. Выходная обмотка фазовращателя 5 соединена с входами формирователя 9 импульсов, выход которого соединен с первым входом синхронизатора 10 и первым входом временного дискриминатора 11.. Второй / вход синхронизатора 10 соединен с выходом младшего разряда делителя 2 частоты. Одни входы блока 13 управения соединены с выходами разрядов елителя 2 частоты. Первый вход блоа 12 соединен с первым выходом делителя 2 частоты, а второй вход - с пятым выходом делителя 2. Выход син хронизаторй 10 соединен с другим входом блока 13 управления и вторым входом временного дискриминатора 11 выход которого соединен с третьим входом блока 12. Выходы блока 13 у равления подключены к одним входам арифметического блока 14.Первый и в рой .выходы блока 12 подключены к третьему входу, синхронизатора 10 и другому входу арифметического блока 14 Блок 12 преобразования тока в ко (фиг.2) содержит интегратор 29, ком паратор 30, триггер 31, два элемента И 32, 33, делитель 34 частоты, двоичный счетчик 35, ключ 36 и ста билизатор 37 тока. Первый входинтегратора 29 соединен с третьим вхо дом блока 12, а второй вход - с выходом ключа 36, один вход которого подключен к выходу стабилизатора 3 тока. Выход интегратора 29 соедин с входом компаратора 30, выход кото рого соединен с первым входом триг- гера 31, второй вход которого сое динен с вторым входом блока 12 и подключен к одному входу элемента И 32. Выход триггера 31 подключен к второму входу ключа 36 и другому входу элемента И 32, а первый вход блока 12 через делитель 34 частоты подключен к первому выходу блока 12 и к одному входу элемента И 33, дру гой вход которого соединен с выходом элемента 32 И, а выход через счетчик 35 подключен к второму выходу блока. Преобразователь работает следующим образом. Кварцевый генератор 1 вырабатывает стабильные по частоте импульсы, которые делитель 2 частоты дели в 2 раз, где h - число его разрядов, вырабатывая временную кодовую маску. Одновременно делитель 2 частоты вырабатывает опорные меандры для блоков 3 и. 4 формирования синусоидального и косинусоидального токов питания фазовращателя 5, осуществляющих привязку нулей фаз этих токов к опорным меандрам за счет временной задержки последних, благодаря чему обеспечивается точное поддержание 9 О -него, сдвига питающих токов. Кроме того, при совместной работе блоков 3 и 4 формиро вания синусоидального и косинусои дального токов и блока 6 сравнения амплитуд обеспечивается точная уста новка и стабилизация равенства амп литуд питающих токов. Импульсы с выходов блоков 3 и 4 формирования синусоидального и косй нусоидального тоКов поступают на входы формирователя 7 синусоидальны напряжений и далее через усилитель на входные обмотки фазовращателя 5. Напряжение с выходной обмотки фазовращателя 5 поступает на вход формирователя 9 импульсов, вырабатывающего фазовые импульсы, временное положение последних пропорционально углу поворота ротора фазовращателя 5. Фазовые импульсы поступают на вход синхронизатора 10, на второй вход которого приходят импульсы младшего разряда с выхода разрядов делителя 2 частоты, а на третий вход - сигнал разрешения с первого выхода блока 12, Синхронизатор 10 вырабатывает импульсы записи после прихода сигнала разрешения . Период следования импульсов записи равен периоду питающих фазовращатель 5 напряжений. Время задержки импульсов записи относительно первого фазового импульса после прихода сигнала разрешения (совпаде- к- ние с , например вторым, импульсом младшего разряда) выбирается, исходя из максимальной скорости изменения угла поворота, так, чтобы за время измерения угла фазовый импульс записи всегда отставал от фазового импульса. Импульсы записи с выхода синхронизатора 10 поступают на блок 13 управления и переписывают его содержимое в арифметический блок 14.Одновременно фазовый импульс с выхода формирователя 9 импульсов поступает на первый вход временного дискриминатора 11, на второй вход которого приходят импульсы записи с выхода синхронизатора 10,Временной дискриминатор 11 преобразует временной интервал между импульсами формирователя 9 импульсов и фронтом импульса записи синхронизатора 10 в импульс тока положительной полярности . С выхода временного дискриминатора 11 импульсы тока поступают на третий вход блока 12. За время измерения, в N раз превышаквдее период питающих фазовращатель 5 токов, блок 12 суммируэт импульсы тока с выхода временного дискриминатора 11 и преобразует среднюю величину тока в m -разрядный двоичный код. Импульсы тока, поступающие на вход блока 12, заряжают его конденсатор по линейному закону до напряжения срабатывания компаратора 30, После срабатывания компаратора 30 первый импульс младшего разряда делителя 2 частоты переводит триггер 31 в противоположное состояние, при этом замыкается ключ 36, и на другой вход интегратора 29 поступает разряжающий ток стабилизатора 37 тока. Напряжение на выходе интегратора 29 уменьшается до напряжения срабатывания компаратора 30, после чего ближайший импульс младшего разряда возвращает триггер 31 в исходное состояние, ключ 36 размыкается. Далее цикл работы повторяется. Время измерения тока в преобразователе 12 ток - код определяется ко личеством разрядов делителя 34 частоты, на вход которого поступают опорные меандрыпериода Т с первого выхода делителя 2 частоты. Делитель 34 подсчитывает импульсы младшего разряда, которые проходят через элементы И 32, 33 во время заряда конденсатора интегратора 29 за время из мерения, определяемое коэффициентом .передачи делителя 4 частоты, и преобразует число импульсов в m -разрядный дополнительный двоичный ..код.Этот код с выхода блока 12 поступает на второй вход арифметического блока 14 осуществляющего суммирование этого к да с п -разрядным кодом, поступающим на его первый, вход с выхода блока 13 управления. На выходе арифметического блока образуется суммарный двоичный код. Таким образом, введение в прео.бразователь временного дискриминатора, блока 12 преобразования тока в код. и синхронизатора при указанном их соединении позволяет повысить точ- ность преобразователя за счет уменьшения погрешности дискре;гности преобразования без повышения частоты кварцевого генератора путем увеличения разрядности преобразователя на ,т разрядов, а также за счет уменьшения п огрешности от влияния внешних и внутренних шумов путем интегрирования результатов измерения. Экономический эффект от-использования преобразователя определяется его техническим пр еимуществом.

f}

Фие. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1984-10-30—Публикация

1983-07-29—Подача