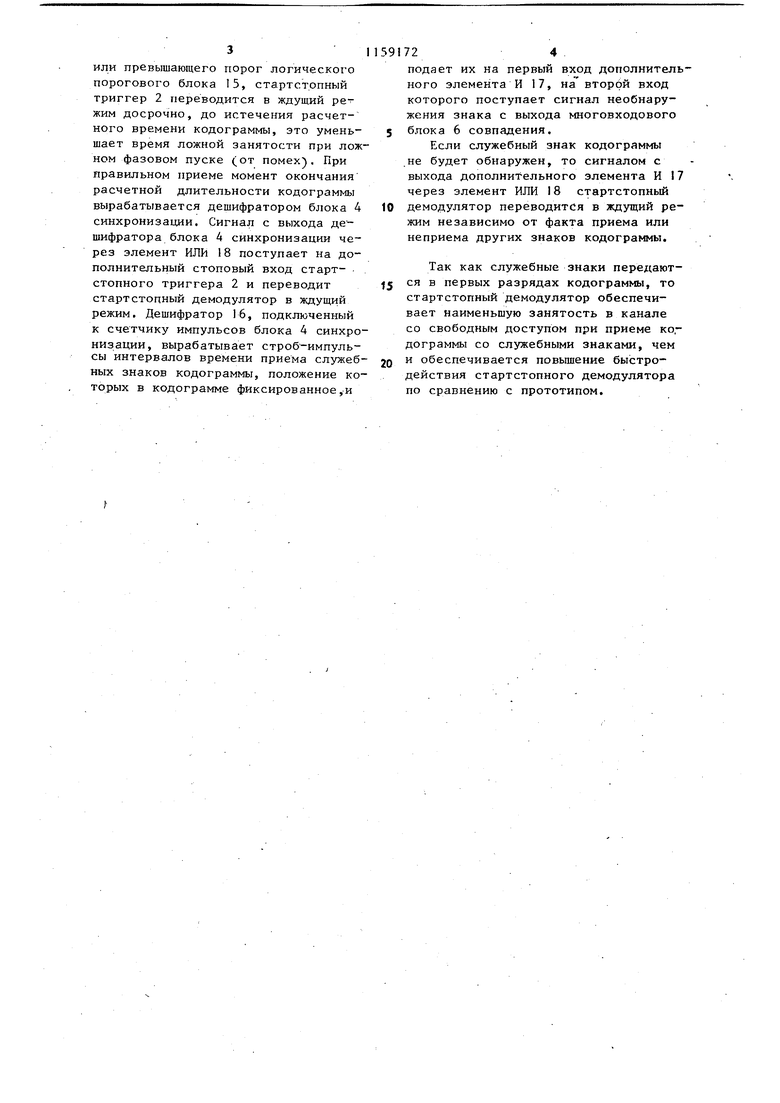

1 Изобретение относится к электросвязи и может быть использовано для стартстопной демодуляции информационных блоков. По основному авт. св.(| 497741 известен стартстопный демодулятор, содержащий последовательно включенные обнаружитель адресного синхросигнала, стартстопный триггер, элемент.И, блок синхронизации и решающий блок с подключенными к нему обнаружителями знаков, а также генера тор опорной частоты, подключенный к второму входу элемента И, выходы об наружителей знаков дополнительно по гслючены через инверторы к многовход вому блоку совпадения, выход -которо через последовательно включенные счетчик знаков и логический порогов блок подключен к стоповому входу стартстопного триггера, причем управляющий и обнуляющий входы счетчи знаков подсоединены соответственно стартовому и стоповому выходам стар стопного триггера, а выход блока синхронизации дополнительно соединен с одним из входов многовходовог блока совпадения OJ .. Недостатком известного стартстопного демодулятора является низкое быстродействие при работе в канале со свободным доступом. Цель изобретения - повышение быс родействия при работе в канале со свободным доступом. . Поставленная цель достигается тем что в стартстопный демодулятор, содержащий последовательно включенные обнаружитель адресного синхросигнала, стартстопный триггер, элемент И блок синхронизации и решающий блок с подключенными к нему обнаружителями знаков, а также генератор опорной частоты, подключенный к второму вход элемента И, выходы обнаружителей зна ков дополнительно подключены через инверторы к многовходовому блоку сов падения, выход которого через последовательно вклю.енные счетчик знаков и логический пороговый блок подключен к стоповому входу стартстопного триггера, лричем управляющий и обнуляющий входы счетчика знаков подсоединены соответственно к стартовому и стоповому выходам стартстопного .триг гера, а выход блока синхронизации дополнительно соединен с одним из входов многовходового блока совпадения, введены последовательно соеди722ненные дешифратор и дополнительный элемент И, а также элемент ИЛИ, при этом элемент ИЛИ включен между первым дополнительным выходом блока синхронизации и дополнительным стоповым входом стартстопного триггера, вход дешифратора и выход дополнительного элемента И подключен соответственно к второму дополнительному выходу блока синхронизации и второму входу эл,емента ИЛИ, а второй вход дополнительного элемента И подключен к выходу многовходового блока совпадения. Блок синхронизации содержит последовательно соединенные счетчик импульсов и первый дешифратор, а также второй дешифратор, вход которого подключен к выходу счетчика импульсов, причем счетный и обнуляющий входы счетчика импульсов являются соответственно первым и вторым входами блока синхронизации, а выходы первого и второго дешифраторов и выход счетчика импульсов являются соответственно выходом, первым дополнительным выходом и вторым дополнительным выходом блока синхронизации. На чертеже представлена структурная электрическая схема стартстопного демодулятора, Стартстопный демодулятор содержит обнаружитель 1 адресного- синхросигнала, стартстопный триггер 2, элемент ИЗ, блок 4 синхронизации, решающий блок 5, многовходовой блок 6 совпадения, инверторы 7-9, обнаружители 10-12 знаков, генератор 13 опорной частоты, счетчик 14 знаков, логи шский пороговый блок 15, дешифратор 16, дополнительный элемент И 17, элемент ИЛИ 18. Стартстопный демодулятор работает следующим образом. Адресный синхросигнал от обнаружителя 1 через стартстопный триггер 2 и элемент И 3 осуществляет фазовьш пуск блока 4 синхронизации, в кото-, ром счетчик импульсов начинает отсчитывать такты опорного генератора 13, а дешифратор 16 обеспечивает тактовую синхронизацию, т.е. вырабатывает сигналы Моменты отсчета для решающегр блока 5, осуществляемого демодуляцию знаков, поступающих на обнаружители знаков 10-12. Число необнаруженных знаков подсчитывается счетчиком 14 знаков, При необнаружении некоторого числа знаков, равного

3

или превышающего порог логического порогового блока 15, стартстопный триггер 2 переводится в ждущий режим досрочно, до истечения расчетного времени кoдoгpaм я I, это уменьшает время ложной занятости при ложном фазовом пуске (от помех). При правильном приеме момент окончания расчетной длительности кодограммы вырабатывается дешифратором блока 4 синхронизации. Сигнал с выхода дешифратора блока 4 синхронизации через элемент ИЛИ 18 поступает на дополнительный стоповый вход стартстопного триггера 2 и переводит стартстопный демодулятор в ждущий режим. Дешифратор 16, подключенный к счетчику импульсов блока 4 синхронизации, вырабатывает строб-импульсы интервалов времени приема служебных знаков кодограммы, положение которых в кодограмме фиксированное,и

591724

подает их на первый вход дополнительного элемента И 17, на второй вход которого поступает сигнал необнаружения знака с выхода многовходового 5 блока 6 совпадения.

Если служебный знак кодограммы не будет обнаружен, то сигналом с выхода дополнительного элемента И I7 через элемент ИЛИ 18 стартстопный 10 демодулятор переводится в ждущий режим независимо от факта приема или неприема других знаков кодограммы.

Так как служебные знаки передаются в первых разрядах кодограммы, то стартстопный демодулятор обеспечивает наименьшую занятость в канале со свободным доступом при приеме кодограммы со служебными знаками, чем и обеспечивается повышение быстродействия стартстопного демодулятора по сравнению с прототипом.

/ (

Л -M

| название | год | авторы | номер документа |

|---|---|---|---|

| Стартстопный демодулятор | 1986 |

|

SU1363516A1 |

| Стартстопный демодулятор | 1982 |

|

SU1062876A1 |

| Хронизатор сеансов связи | 1982 |

|

SU1088147A1 |

| Стартстопный хронизатор сеансов ведомой станции | 1977 |

|

SU661832A1 |

| Стартстопный хронизатор сеансов ведомой станции | 1982 |

|

SU1125762A1 |

| Стартстопный хронизатор сеансов ведомой станции | 1982 |

|

SU1078657A2 |

| Генератор импульсной последовательности | 1986 |

|

SU1370737A1 |

| Устройство для настройки стартстопного приемника на скорость передачи | 1976 |

|

SU620026A1 |

| Система передачи дискретной информации | 1981 |

|

SU978374A1 |

| Электронный стартстопный распределитель | 1979 |

|

SU966927A1 |

1. СТАРТСТОПНЫЙ ДЕМОДУЛЯТОР по авт.св.№ 4.97741, о т л и ч аю щ и и с я тем, что, с повышения быстродействия при работе в канале со свободным доступом, в демодулятор введены последовательно соединенные дешифратор и дополнительный элемент И, а также элемент ИЛИ, при этом элемент ИЛИ включен между первым дополнительным выходом блока синхронизадии и дополнительным стоповым входом стартстопного триггера , вход дешифратора и выход дЬполнительного элемента Н подключены соответственно к второму дополнительному выходу блока синхронизации и второму входу элемента ИЛИ, а второй вход дополнительного элемента И подключен к выходу многовходрвого блока совпадения. 2. Демодулятор по п,I, о т л ичающийся тем, что блок синхронизации содержит последовательно соединенные счетчик импульсов и пер-вый дешифратор, а также второй дешифратор, вход которого подключен к выходу счетчика импульсов, причем с S счетный и обнуляющий входы счетчика (Л импульсов являются соответственно первым и вторым входами блока синхронизации, а выходы первого и второго дешифраторов и выход счетчика импульсов являются соответственно выходом, первым дополнительным выходом и вторым дополнительным выходом блока синхронизации.

90

сы;

/ V

/ k

CM

со Or

/ k / V V

to

/ V / k / s

i

o

00

/ k

Авторы

Даты

1985-05-30—Публикация

1983-07-08—Подача