теля подключены соответственно к четвертому источнику напряжения и к третьему источнику напряжения, коллекторы пятого и шестого транзисторов первого формирователя уровней подключены к точкам соединения анодов первого и второго диодного мостов, точки соединения катодов которых подключены соответственно к коллекторам пятого и шестого транзисторов второго формирователя уровней, первые точки соединения анод-катод первого и

второго диодного мостов ПОДКЛК1ЧеР1Ы

к уровню логического нуля и соответственно к уровню логической единицы, вторые точки соединения анодкатод первого и второго диодного мостов соединены между собой и подключены к выходу ус-гройства формирования эталонных цифровых сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАТЕЛЬ БИПОЛЯРНЫХ ИМПУЛЬСОВ ЭТАЛОННОГО ТОКА | 1991 |

|

RU2065663C1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU822295A1 |

| Импульсный стабилизатор напряжения постоянного тока | 1981 |

|

SU983679A1 |

| Устройство формирования эталонных цифровых сигналов | 1982 |

|

SU1095372A1 |

| Переключатель переменного тока | 1986 |

|

SU1354410A1 |

| Формирователь треугольно-трапецеидального напряжения | 1984 |

|

SU1231586A1 |

| СХЕМА КОНТРОЛЯ | 1997 |

|

RU2153765C2 |

| Устройство для управления двухфазным асинхронным электродвигателем | 1990 |

|

SU1777225A1 |

| Способ поиска дефектов в цифровых блоках и устройство для его осуществления | 1985 |

|

SU1260884A1 |

| СПОСОБ УПРАВЛЕНИЯ МАГНИТНО-ТРАНЗИСТОРНЫМ КЛЮЧОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1989 |

|

RU2006180C1 |

УСТРОЙСТВО ФОРМИРОВАНИЯ ЭТАЛОННЫХ ЦИФРОВЫХ СИГНАЛОВ, содержащее последовательно соединенные первьй переключатель тока и первый формирователь уровня, содержащие соответственно первьш и второй источники напряжения, и последовательно соединенные и выполне шые на транзисторах противоположной нолярности второй переключатель тока и второй формирователь уровня, содержащие соответственно третий и четвертый источники напряжений,.первый и второй переключатели тока вьтолнены на первом, втором, третьем и четвертом транзисторах, первый и второй формирователи уровней выполнены на пятом и шестом транзисторах соответственно р-п-р-типа и 1-р-П-типа, эмиттеры пятого транзистора соответственно первого и второго формирователей уровня подсоединены через первый резистор соответственно к второму и четвертому источникам напряжения, третий и четвертьй транзисторы соответственно первого и второго переключателей токов выполнены по схеме с объединенньии эмиттерами и в цепи их коллекторов .включены второй и третий резисторы, база и эмиттер второго транзистора h-p-n- и р-п-р-типа соответственно первого и второго переключателей токов подключены к первым выводам соответственно четвертого и пятого резисторов, базы первых транзисторов первого и второго переключателей токов подключены к первым входным шинам устройства формирования эталонных цифровых сигналов, о т л ичающееся тем, что, с целью расЕйирения функциональных возможностей путем обеспечения работы от i источников сигнала противоположных полярностей, в него введены первый (Л и второй диодные мосты, последовательно соединенные шестой и седьмой резисторы первого и второго переключателей тока, подключенные между эмиттером первого транзистора и вторыми входньп 1и шинами устройства формирования эталонных цифровых сигналов, причем первый транзистор о первого переключателя тока вьтолнен 4 на транзисторе р-п-р-типа, а третийи четвертый транзисторы первого СО переключателя тока выполнены п-р-Птипа, формирователи уровня выполнены по схеме переключателей тока с объединенными эмиттерами, вторые выводы второго и третьего резисторов и соответственно четвертого и пятогорезисторов первого переключателя тока подк.гаочены соответственно к второму источнику напряжения и к первому источнику напряжения, вторые выводы второго и третьего резисторов и соответственно четвертого и пятого резисторов второго переключа

1

Изобретение может быть использовано в радиоэлектронной аппаратуре различного назначения, в частности в многоканальной аппаратуре контроля и измерения параметров цифровых схем для формирования эталонных цифровых сигналов с заданными уровнями и длительностью фронтов сигналов .

Цель изобретения - расширение функциональных возможностей устройства путем обеспечения работы от источников сигнала противоположных полярностей..

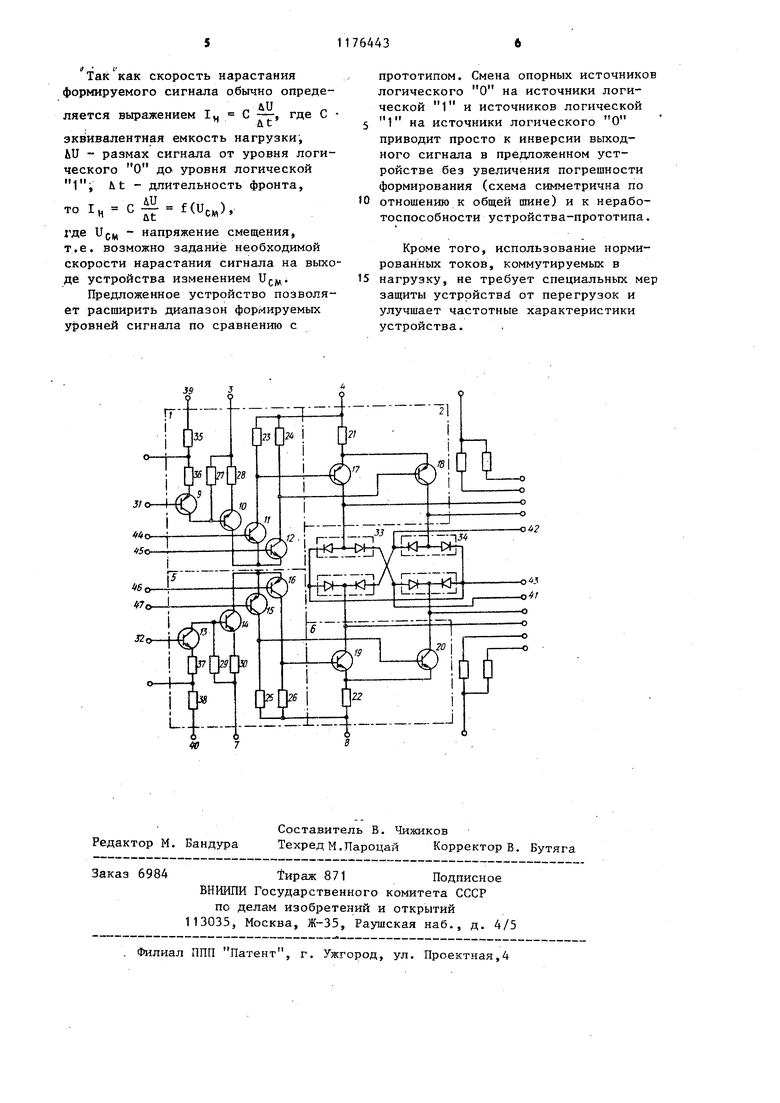

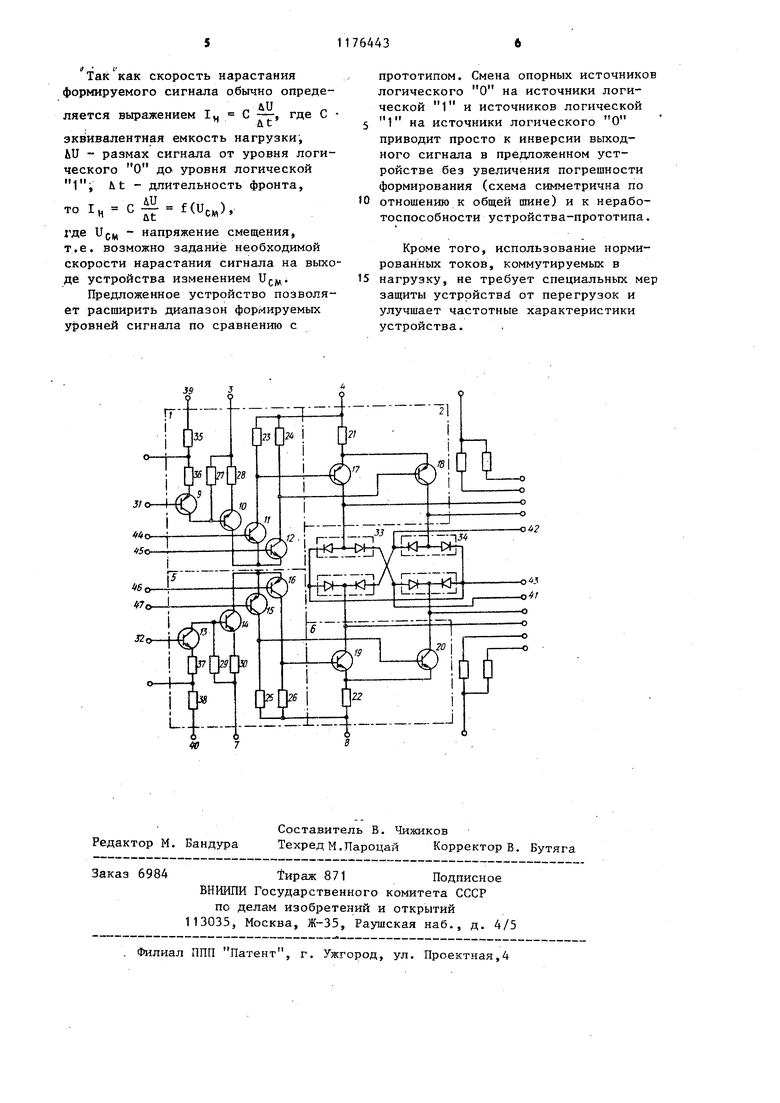

На чертеже представлена принципиальная электрическая схема устройства формирования эталонных цифровых сигналов.

Устройство формирования эталонных цифровых сигналов содержит последовательно соединенные первый переключатель 1 тока и первый формирователь 2 уровня, содержащие соответственно первый и второй источники 3, 4 напряжения, и последовательно, соединенные и выполненные на транзисторах противоположной полярности второй переключатель 5 тока и второй формирователь 6 уровня, -содержащие соответственно третий и четвертой источники 7,8 напряжений, первый переключатель 1 тока выполнен на первом, втором, третьем и четвертом транзисторах 9-12, второй переключатель 5 тока выполнен на транзисторах 13-16, первый и второй формирователи 2, 6 уровней выполнены на пятом и шестом транзисторах 17,18 соответственно р -Ъ-р-типа и соответственно

19, 20п-Р-Л-типа, эмиттеры пятого транзистора соответственно первого и второго формирователей 2, 6 уровня подсоединены через первый резистор 21 и соответственно резистор 22 к соответствующим второму и четвертому источникам 4, 8 напряжения, третий и четвертый транзисторы 11, 12 и 15, 16 соответственно

первого и второго переключателей 1 и 5 токоБ выполнены по схеме с объединенньми эмиттерами и в цепи их коллекторов включены второй и третий резисторы соответственно 23,

24 и 25, 26, база и эмиттер второго транзистора п-р-п- и р-п-р-типа соответственно первого и второго переключателей 1 и 5 токов подключены к первым выводам соответственно четвертого и пятого резисторов соответственно 27, 28,29, 30 базы первых транзисторов соответственно первого и второго переключателей 1, 5 токов являются соответственно

nepBbiM и вторым входами 31, 32, устройства формирования эталонных цифровых сигнаюв, первый и второй диодные мосты 33 и 34, последовательно соединенные шестой и седьмой

резисторы 35, 36 и 37, 38 соответственно первого и второго переключателей 1 и 5 тока, подключенные между эмиттером первого транзистора 9 и 13 и вторыми входными тинами 9, 40 устройства формирования эталонных цифровых сигналов, причем первый транзистор первого переключателя 1 тока выполнен на транзисторе р-0--р-типа, а третий и четвертый транзисторы первого перск.тючате.гш 1 .тика выполнены п :ТИ11 ч , ibopMiuxi ватели 2 и 6 урогзня выполнены по схеме переключателей тока с объеди ненными эмиттерами, вторые выводы второго и третьего резисторов 23,2 и соответственно четвертого и пято го резисторов 27,23 переключателя тока подключены к второму источнику 4 положительного напряжения и соответственно к первому источнику 3 отрицательного напряжения,вторые выводы второго и третьего резисторов 25, 26 и соответственно четвертого и пятого резисторов 29, 30 второго переключателя 5 тока подклю чены к четвертому источнику 8 отри цательного напряжения и соответственно к третьему источнику 7 положительного напряжения, коллекторы пятого и шестого транзисторов 17, 18 первого формирователя 2 уровней -подключены к точкам соединения анодов первого и второго диодного мостов 33, 34, точки соединения ка тодов которых подключены соответственно к коллекторам пятого и шестого транзисторов 19, 20 второго формирователя уровней, 6 первые точки соединения анод-катод первог и второго диодного мостов подключе ны к шине логического нуля 41 и соответственно к шине логической единицы 42, вторые точки соединения анод-катод первого и второго диодного мостов соединены между собой и подключены к выходу 43 устройства формирования эталонных цифровых сигналов, входы 44, 45, 46, 47 являются дополнительными входами устройства. Устройство работает следующим образом. При поданном питании сигнал высокого уровня (логическая 1 ТТЛ уровня) на базе транзистора 9 отключает генераторы токов на транзисторах 9-10 и 13-19, так как переходы база-эмиттер транзисторов 9 и 13 находятся в обратносмещенном состоянии. Все транзисторы устройства закрыты независимо от уровней логических сигналов на информационных входах (базах транзисторов 11, 12, 15, 16) устройства, при этом переходы диодов в мостах 33, 34 сме щены в обратном направлении и устройство находится п третьем (отключенном от нагрузки) состоянии. НачЗличие сигнала низкого уровня (логический О ТТЛ уровня) на базе транзистора 9 включает генераторы токов на транзисторах 9, 10, 13, 14 и с коллекторов транзисторов 10, 14задаются токи питания переключателей токов на транзисторах 11, 12 и 15,16, состояние устройства и полярность формируемого сигнала определяются в этом случае полярностью сигналов на базах транзисторов 11, 15, 12, 16. При высоком уровне«управляющего сигнала на базах транзисторов 11, 16 и низком уровне управляющего сигнала на базах транзисторов 12, 15транзисторы 11, 15 включены, в цепи баз транзисторов 17, 20 заданы управляющие токи, практически равные токам питания первых переключателей 1,5 токов. Транзисторы 17, 20 работают при этом как генераторы тока питания диодного моста 33. Токи, снимаемые с коллекторов транзисторов 17, 20 смещают переходы диодов моста 33 в прямом направлении, подключая источник опорного напряжения логического О к нагрузке (выходу устройства). При низком уровне управляющего сигнала на базах транзисторов 11, 16и высоком уровне управляющего сигнала на базах транзисторов 10, 12 транзисторы 11, 15 выключены, а транзисторы 12, 16 включены ив цепи баз транзисторов 17, 20 в диодный мост 33 подаются токи, посредством которых формируется на выходе устройства сигнал с заданным опорным уровнем логической 1 (аналогично формированию сигнала с уровнем логического О). Особенностью работы устройства является то, что формирование этаонного цифрового сигнала осуществляется номированным током (током заданного значения), отдаваемым в нагрузку. При зтом в момент переключения сигналов в нагрузку с иодного моста снимается весь ток 1, а при достижении заданного опорного уровня происходит переаспределение токов, протекающих через диоды моста, и уровень форируемого (Um.c ) сигнала определяется как сумма падений напряжений а диодах моста Um.c Ug, -U/,,-U

Так как скорость нарастания формируемого сигнала обычно опреде„ ли

ляется выражением I.

где С

uf

эквивалентная емкость нагрузки, MJ - размах сигнала от уровня логического О до уровня логической

М II

&t - длительность фронта,

ли

Т - г - f Гп

),

то Н л CM

at

где Up - напряжение смещения, т.е. возможно задание необходимой скорости нарастания сигнала на выходе устройства изменением U(.i

Предложенное устройство позволяет расширить диапазон формируемых уровней сигнала по сравнению с

39

J7

прототипом. Смена опорных источников логического О на источники логической 1 и источников логической 1 на источники логического О приводит просто к инверсии выходного сигнала в предложенном устройстве без увеличения погрешности формирования (схема симметрична по отношению к общей шине) и к неработоспособности устройства-прототипа.

Кроме того, использование нормированных токов, коммутируемых в нагрузку, не требует специальных мер защиты устройств от перегрузок и улучшает частотные характеристики устройства.

| Измерение параметров цифровых интегральных микросхем | |||

| Под ред | |||

| Д,Ю, Эйдукаса, М,: Радио и связь, 1982, с, 265-266, рис, 6.19 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Там же, с, 267-272, рис, 6,20 и рис, 6,21 , | |||

Авторы

Даты

1985-08-30—Публикация

1983-04-15—Подача