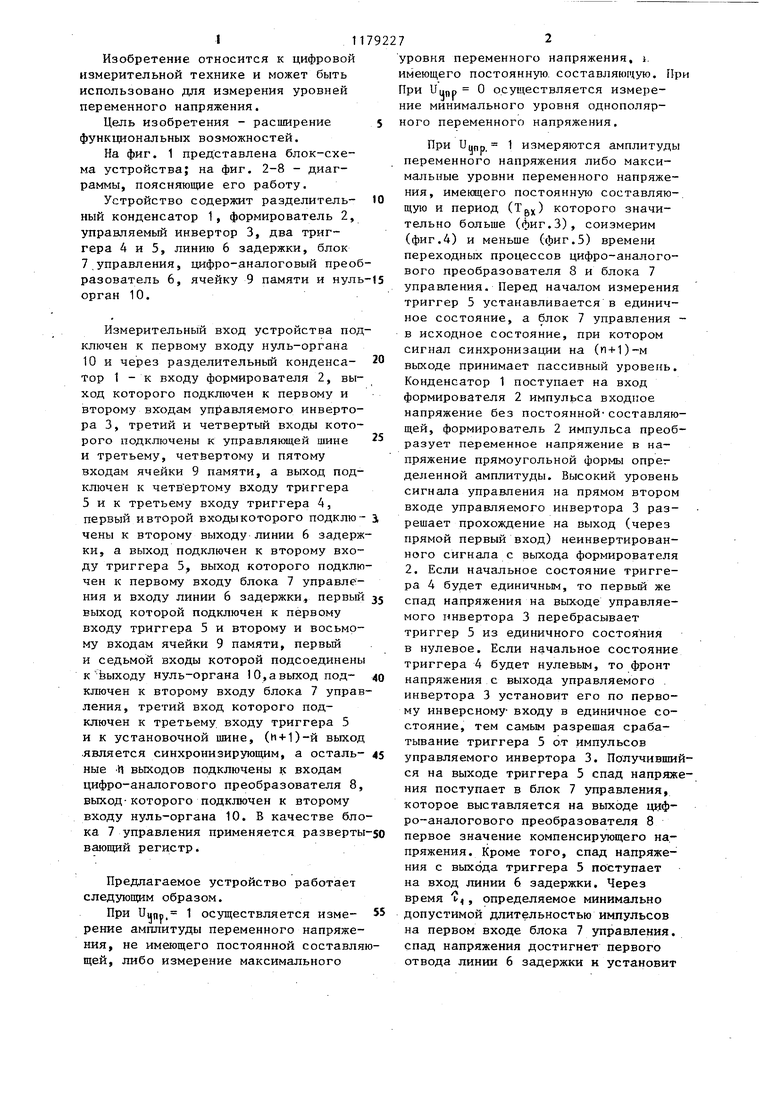

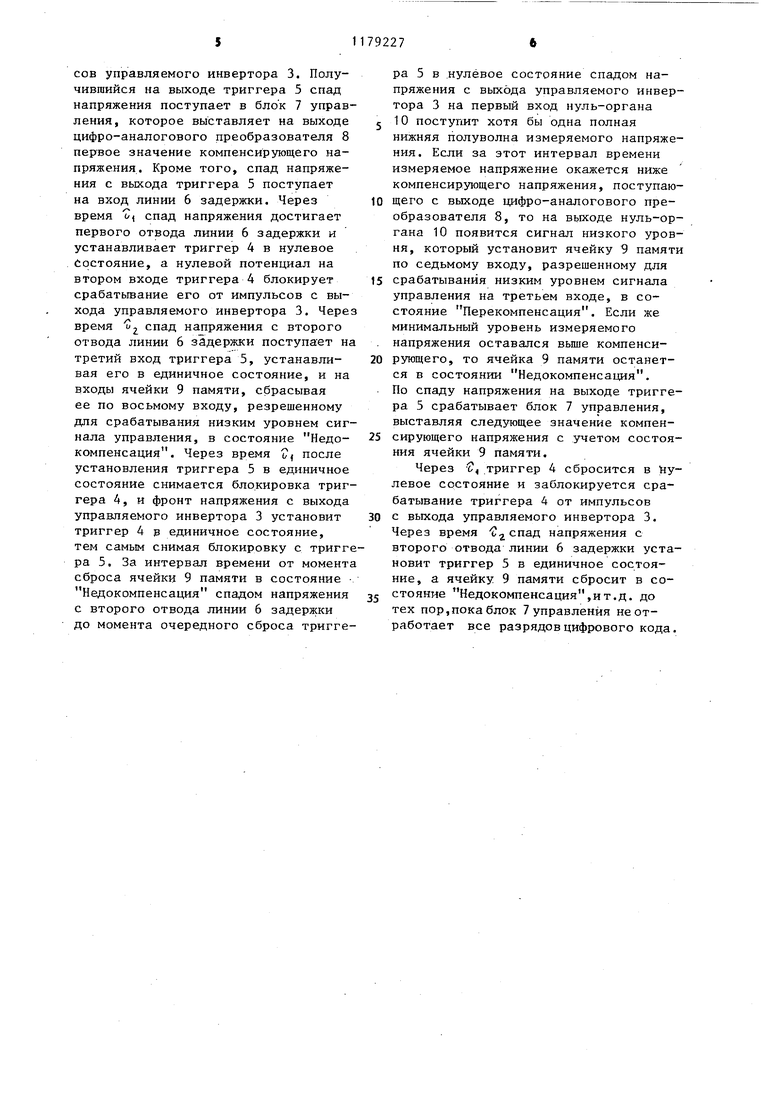

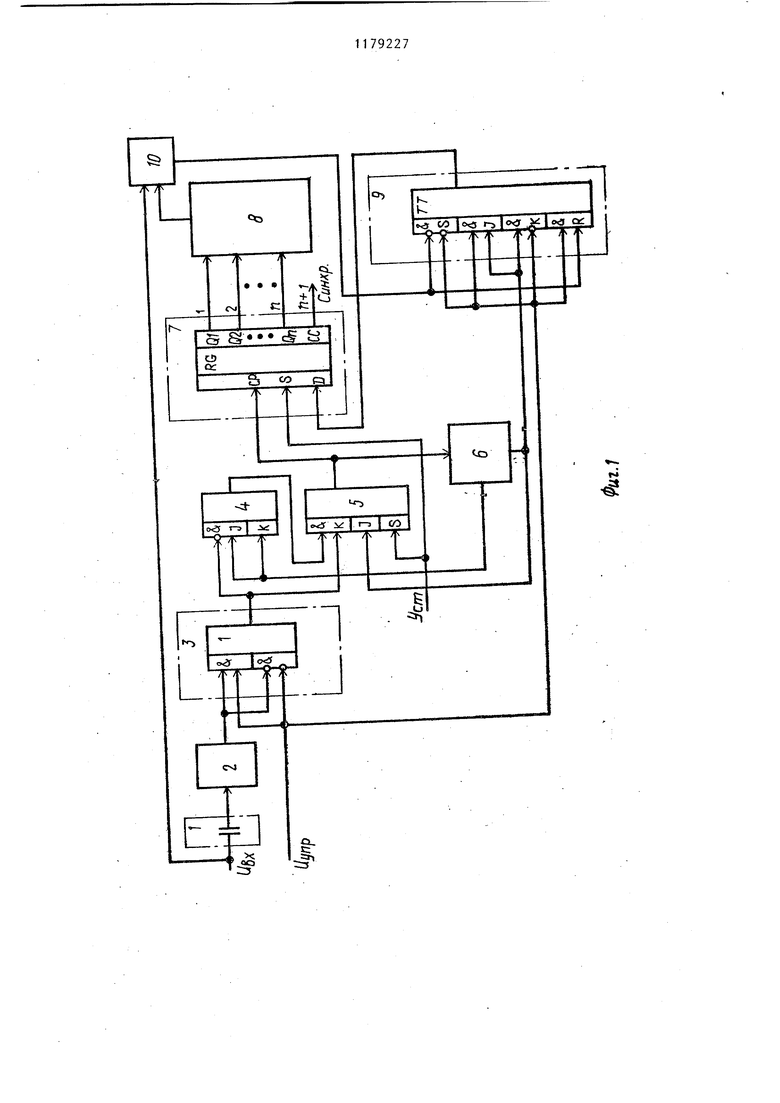

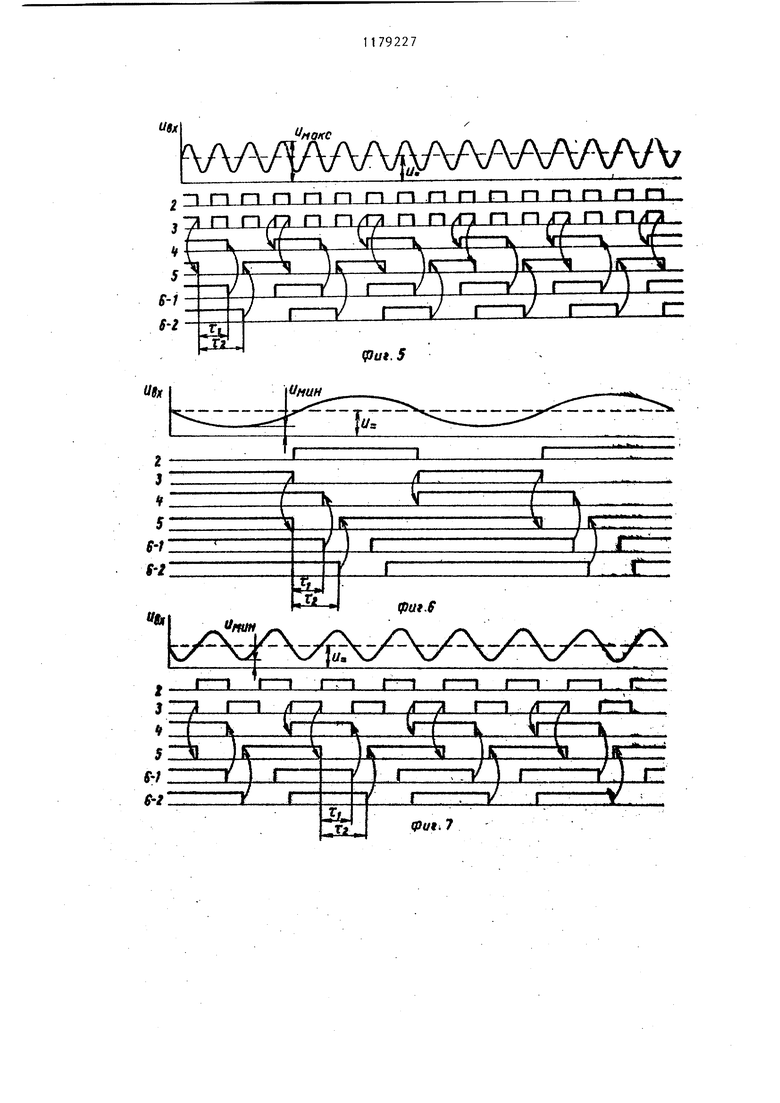

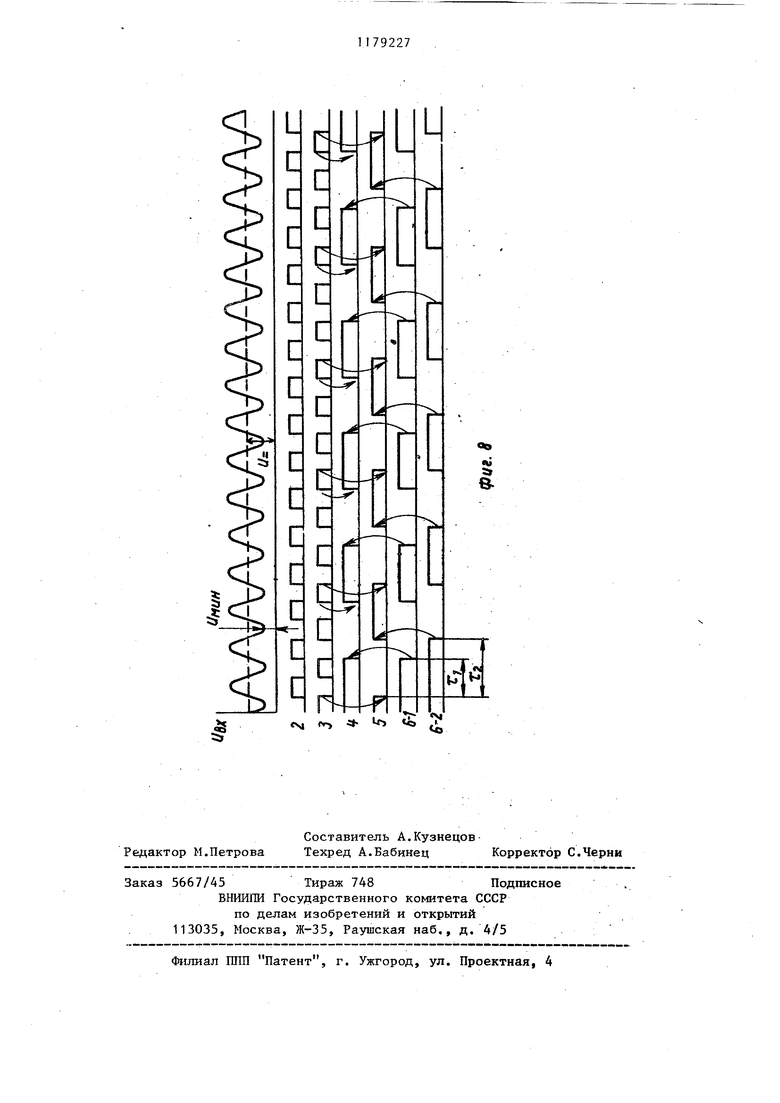

Изобретение относится к цифровой измерительной технике и может быть использовано для измерения уровней переменного напряжения. Цель изобретения - расширение функциональных возможностей. На фиг. 1 представлена блок-схема устройства; на фиг. 2-8 - диаграммы, поясняющие его работу. Устройство содержит разделительный конденсатор 1, формирователь 2, управляемый инвертор 3, два триггера 4 и 5, линию 6 задержки, блок 7 управления, цифро-аналоговый преоб разователь 6, ячейку 9 памяти и нуль орган 10. Измерительный вход устройства под ключен к первому входу нуль-органа 10 и через разделительньш конденсаТор 1 - к входу формирователя 2, выход которого подключен к первому и второму входам уп1 авляемого инвертора 3, третий и четвертый входы которого подключены к управляющей шине и третьему, четвертому и пятому входам ячейки 9 памяти, а выход подключен к четвертому входу триггера 5 и к третьему входу триггера 4, первый ивторой входыкоторого подклю чены к второму выходу линии 6 задерж ки, а выход подключен к второму входу триггера 5, выход которого подклю чен к первому входу блока 7 управле ния и входу линии 6 задержки, первый выход которой подключен к первому входу триггера 5 и второму и восьмо му входам ячейки 9 памяти, первый и седьмой входы которой подсоединен кЪыходу нуль-органа 10,а выход подключей к второму входу блока 7 упра ления, третий вход которого подключен к третьему входу триггера 5 и к установочной шине, (и+1)-й выход .является синхронизирующим, а осталь ные И выходов подключены к входам цифро-аналогового преобразователя 8 выход-которого подключен к второму входу нуль-органа 10. В качестве бл ка 7 управления применяется разверт вающий регистр. Предлагаемое устройство работает следующим образом. При Uunn. 1 осуществляется измерение амплитуды переменного напряже ния, не имеющего постоянной составл щей, либо измерение максимального ровня переменного напряжения, t, меющего постоянную, составляющую. При ри Uunp О осуществляется измереие минимального уровня однополярого переменного напряжения. При Unjip 1 измеряются амплитуды переменного напряжения либо максимальные уровни переменного напряжения, имеющего постоянную составляю-, щую и период (Tg)() которого значительно больше (фиг.З), соизмерим (фиг.4) и меньше (фиг.5) времени переходных процессов цифро-аналогового преобразователя 8 и блока 7 управления. Перед началом измерения триггер 5 устанавливается в единичное состояние, а блок 7 управления в исходное состояние, при котором сигнал синхронизации на (п+1)м выходе принимает пассивный уровень. Конденсатор 1 поступает на вход формирователя 2 импульса входное напряжение без постоянной-составляющей, формирователь 2 импульса преобразует переменное напряжение в напряжение прямоугольной формы опрег деленной амплитуды. Высокий уровень сигнала управления на прямом втором входе управляемого инвертора 3 разрешает прохождение на выход (через прямой первый вход) неинвертированного сигнала с выхода формирователя 2. Если начальное состояние триггера 4 будет единичным, то первый же спад напряжения на вькоде управляемого инвертора 3 перебрасывает триггер 5 из единичного состояния в нулевое. Если начальное состояние триггера 4 будет нулевым, то фронт напряжения с выхода управляемого . инвертора 3 установит его по первому инверсному входу в единичное состояние, тем самым разрешая срабатывание триггера 5 от импульсов управляемого инвертора 3. Получившийся на выходе триггера 5 спад напряжения поступает в блок 7 управления, которое выставляется на выходе цифро-аналогового преобразователя 8 первое значение компенсирующего напряжения. Кроме того, спад напряжения с выхода триггера 5 поступает на вход линии 6 задержки. Через время / , определяемое минимально допустимой длительностью импульсов на первом входе блока 7 управления, спад напряжения достигнет первого отвода линии 6 задержки к установит

3

триггер 4 в нулевое состояние, а нулевой потенцил на втором входе триггера 4 блокирует срабатывание его от импульсов с выхода управляемого инвертора 3. Через время о , равное или большее времени переходных процессов блока 7 управления и цифро-аналогового преобразователя 8, спад напряжения с второго отвода линии 6 задержки поступает на третий вход триггера 5, устанавливая его в единичное состояние, и на входы ячейки 9 памяти, устанавливая ее по четвертому входу, разрешенном для срабатывания высоким уровнем синала управления, в состояние ПереКомпенсация. Через время , после установления триггера 5 в единичное состояние снимется блокировка триггра 4, и фронт напряжения с выхода управляемого инвертора 3 установит триггер 4 в единичное состояние, те самь1м снимая блокировку с триггера 5. За интервал времени от момента установки ячейки 9 памяти в состояние Перекомпенсация спадом напряжения со второго отвода линии 6 задержки до момента очередного сброса триггера 5 в нулевое состояние спадом напряжения с выхода управляемог инвертора 3 на первый вход нуль-оргна 10 поступит хотя бы одна полная верхняя полуволна измеряемого напряжения. Если за этот интервал времени измеряемое напряжение превысит компенсирующее напряжение, поступающее с выхода цифро-аналогового преоразователя 8, то на выходе нуль-органа 10 появится сигнал высокого уровня который сбросит ячейку 9 памяти по восьмому входу, разрешенному для срабатывания высоким уровнем сигнала угравления на седьмом входе в состояние Не окомпенсация. Если же максимальный уровень измеряемого напряжения остается ниже компенсирующего, то ячейка 9 памяти останется в состоянии Перекомпенсация. По спаду напряжения на выходе триггера 5 срабатывает блок 7 управления, выставляя следующее значение компенсирующего напряжения с учетом состояния ячейки 9 памяти.

Через о триггер 4 сбросится в нулевое состояние и заблокируется сра- батывание триггера 4 от импульсов с выхода управляемого инвертора 3. Через время Г спад напряжения с

792274

второго отвода линии 6 задержки установит триггер 5 в единичное состояние, а ячейку 9 памяти - в состояние Перекомпенсация и т.д. е до тех пор, пока устройство 7 не отработает все и разрядов цифрового кода. После отработки п-го разряда цифрового кода на (П-нО-м выходе устройства 7 управления появляется

JO активный уровень, являющийся признаком конца измерения, а само устройство 7 управления блокируется до следующей начальной установки.

Таким образом, при Т о2 изменение компенсирующего напряжения производится с каждым периодом входного напряжения (фиг.4), при изменение компенсирующего напряжения производится каждый второй период

20 входного напряжения (фиг.4) и при Tg «о изменение компенсирующего напряжения производится через не сколько периодов входного напряжения (фиг.5) в зависимости от того, насколько 0 больше Тц. При этом длительность импульсов, поступающих с выхода триггера 5 на вход блока 7 управления всегда будет больше ( а период их следования не может быть

30 меньше о -i-o,.

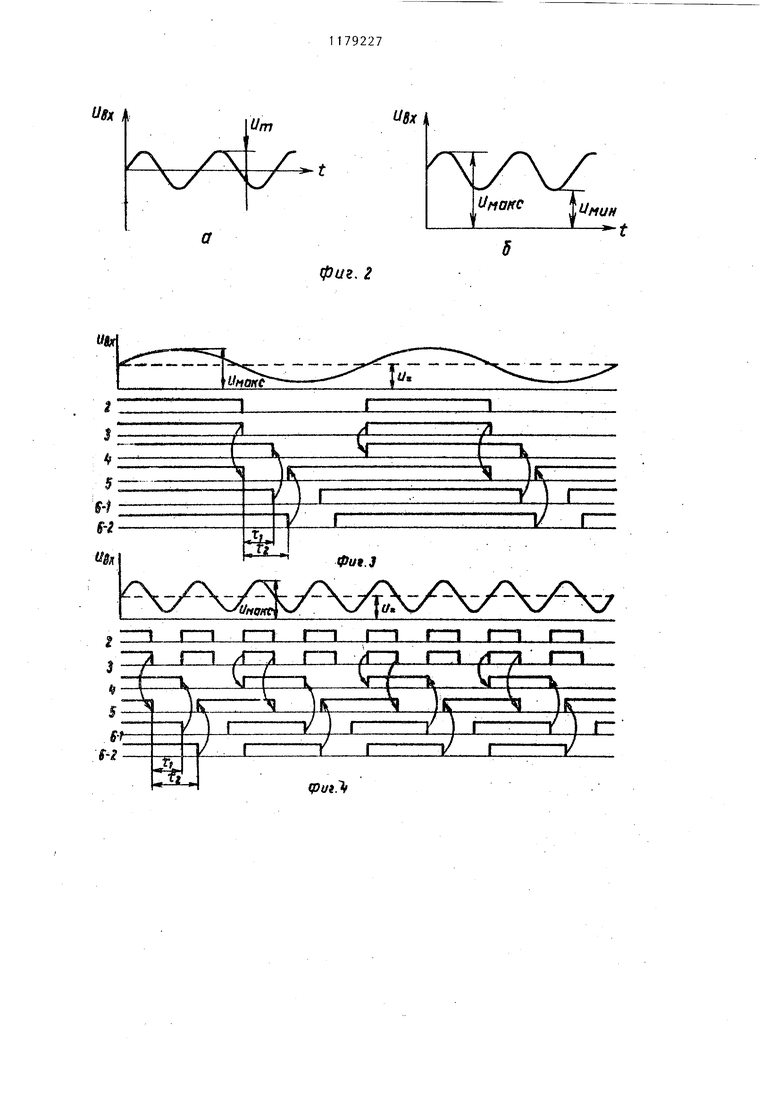

При Uunp О измеряются минимальные значения однополярного переменного напряжения, период (Т ) которого значительно больше (фиг,6),

5 соизмерим (фиг,7) и меньше (фиг,8) времени переходных процессов цифроаналогового преобразователя 8 и блока 7 управления. Перед началом измерения, как и для Uij(,p 1, производит0 ся начальная установка триггера 5

и блока 7 управления. Низкий уровень сигнала управления на инверсном четвертом входе управляемого инвертора 3 разрешает прохождение на выход

5 (через инверсный третий вход) инвертированного сигнала с выхода фор-мирователя 2, Если начальное состояние триггера 4 будет единичным, то первый же спад напряжения на

0 выходе управляемого инвертора 3 перебрасьтает триггер 5 из единичного состояния в нулевое. Если начальное состояние триггера 4 будет нулевым, то фронт напряжения с выхода управляемого инвертора 3 установит его по первому инверсному входу в единичное состояние, тем самым разрешая срабатывание триггера 5 от импульсов управляемого инвертора 3. Получившийся на выходе триггера 5 спад напряжения поступает в блок 7 управления, которое выставляет на выходе цифро-аналогового преобразователя 8 первое значение компенсирующего напряжения. Кроме того, спад напряжения с выхода триггера 5 поступает на вход линии 6 задержки. Через время o спад напряжения достигает первого отвода линии 6 задержки и устанавливает триггер 4 в нулевое Состояние, а нулевой потенциал на втором входе триггера 4 блокирует срабатывание его от импульсов с выхода управляемого инвертора 3. Через время (2 спад напряжения с второго отвода линии 6 задержки поступает на третий вход триггера 5, устанавливая его в единичное состояние, и на входы ячейки 9 памяти, сбрасывая ее по восьмому входу, резрешенному для срабатывания низким уровнем сигнала управления, в состояние Недокомпенсация. Через время (7, после установления триггера 5 в единичное состояние снимается блокировка триггера 4, и фронт напряжения с выхода управляемого инвертора 3 установит триггер 4 в единичное состояние, тем самым снимая блокировку с триггера 5. За интервал времени от момента сброса ячейки 9 памяти в состояние Недокомпенсация спадом напряжения с второго отвода линии 6 задержки до момента очередного сброса триггера 5 в нулевое состояние спадом напряжения с выхода управляемого инвертора 3 на первый вход нуль-органа

с 10 поступит хотя бы одна полная

нижняя полуволна измеряемого напряжения. Если за этот интервал времени измеряемое напряжение окажется ниже компенсирующего напряжения, поступающего с выходе цифро-аналогового преобразователя 8, то на выходе нуль-органа 10 появится сигнал низкого уровня, который установит ячейку 9 памяти по седьмому входу, разрешенному для

5 срабатывания низким уровнем сигнала управления на третьем входе, в состояние Перекомпенсация. Если же минимальный уровень измеряемого . напряжения оставался выше компенси0 ругощего, то ячейка 9 памяти останется в состоянии Недокомпенсация, По спаду напряжения на выходе триггера 5 срабатывает блок 7 управления, выставляя следующее значение компенсирующего напряжения с учетом состояния ячейки 9 памяти.

Через Ci триггер 4 сбросится в нулевое состояние и заблокируется срабатывание триггера 4 от импульсов

0 с выхода управляемого инвертора 3. Через время o-j спад напряжения с второго отвода линии 6 задержки установит триггер 5 в единичное состояние, а ячейку 9 памяти сбросит в состояние Недокомпенсация, и т.д. до тех пор,пока блок 7 управления не отработает все разрядов цифрового кода.

U8X

Urn

UBX

С7

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель экстремумов переменного напряжения | 1985 |

|

SU1290186A1 |

| Цифровой измеритель амплитуды переменного напряжения | 1981 |

|

SU970676A1 |

| Цифровой измеритель амплитуды переменного напряжения | 1982 |

|

SU1027816A1 |

| Устройство для определения параметров экстремумов | 1986 |

|

SU1388812A1 |

| Преобразователь напряжения в код | 1979 |

|

SU851767A1 |

| Устройство для дискретной записи и воспроизведения функций | 1981 |

|

SU982034A1 |

| Устройство для автоматического копирования линии сварного соединения | 1983 |

|

SU1133060A1 |

| Цифровой прибор тензометрических весов | 1983 |

|

SU1101684A1 |

| Следящий аналого-цифровой преобразователь сигналов низкого уровня | 1988 |

|

SU1621139A1 |

| АВТОКОМПЕНСАЦИОННОЕ ИЗМЕРИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU408137A1 |

1. ЦИФРОВОЙ ИЗМЕРИТЕЛЬ АЬШЛИТУДЫ ПЕР ЕМЕННОГО НАПРЯЖЕНИЯ, содержапщй формирователь импульса, нуль-орган, первый вход которого подключен к входной шине, второй вход подключен к выходу цифро-ана ,логового преобразователя, а выход подключен к первому входу ячейки памяти, второй вход которой подключен к первому входу первого триггера и первому выходу линии задержки, второй выход которой подключен к первому и второму входам второго триггера,«выход которого подключен к второму входу первого триггера, третий вход которого подютючен к установочной шине, а выход - к входу линии задержки и к первому входу j блока управления, второй вход которого подключен к выходу ячейки памяти, а П выходов подключены к соответствующим входам цифро-аналогового преобразователя, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены разделительный кЬнденсатор и управляемый инвертор, при этом входная шина через разделительный конденсатор подключена к входу формирователя импульсов, выход которого подключен к первому и второму входам управляемого инвертора, третий и четвертый входы которого соединены с управляющей ., шиной и третьим, четвертым, пятым и шестым входами ячейки памяти, а выход - с третьим входом второго триггера и с четвертью входом первого триггера, третий вход которого (Л подключен к третьему входу блока управления, (п+О-й выход которого С соединен с шиной синхронизации, причем седьмой вход ячейки памяти подключен к первому входу, а восьмой вход - к второму входу.. 2. Измеритель поп.1, отлитл чающийся тем, что блок управления выполнен на регистре, тактовый вход которого является первым входом блока управления, йн-. формационный вход является вторым входом блока управления, установочный вход является третьим входом блока управления, выходы И разрядов являются выходами блока управления, а выход сигнала синхронизации - . (И+1)-м выходом блока управления.

фаг. 2

Фи9.3 г у сла/м:ь

jsi§:

/Г

rn

HT

iiy /VI

2

34

tpui ,-nnnnr-innnnnn .in (-1/0 П n/0 n П/П П 4V ч F Nfv 1

ra (put. 5 VVVV nnnnn n/ri n П, 1 Iy. iSZZi

6-f Si

L

С

с

С

u

:3

eu

: &

I

«V, ,v СЬ 1Л tt, g

I

.«N

| Автоматический цифровой потенциометр | 1959 |

|

SU126191A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой измеритель амплитуды переменного напряжения | 1982 |

|

SU1027816A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-09-15—Публикация

1984-01-20—Подача