Изобретение относится к импульсной технике, в частности к измерительным устройствам для задания фазового сдвига электрических сигналов

Цель изобретения - повьппение точности фазового сдвига за счет уменьшения погрешности дискретизации установки заданного фазового сдвига.

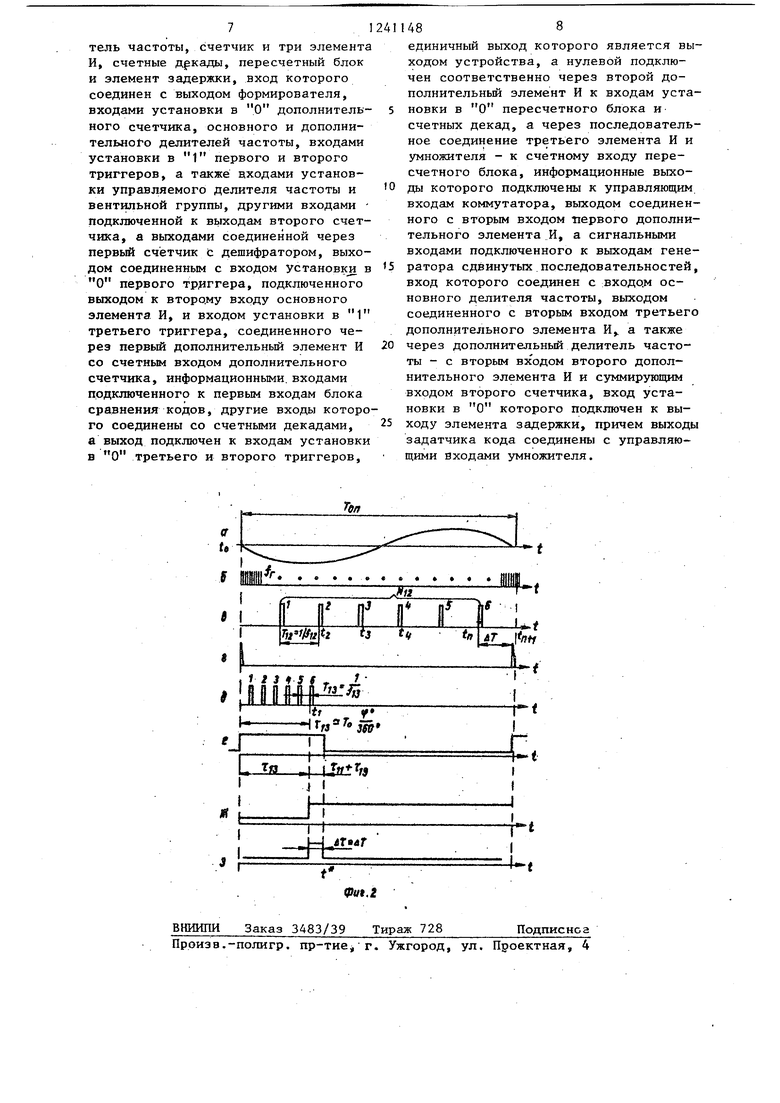

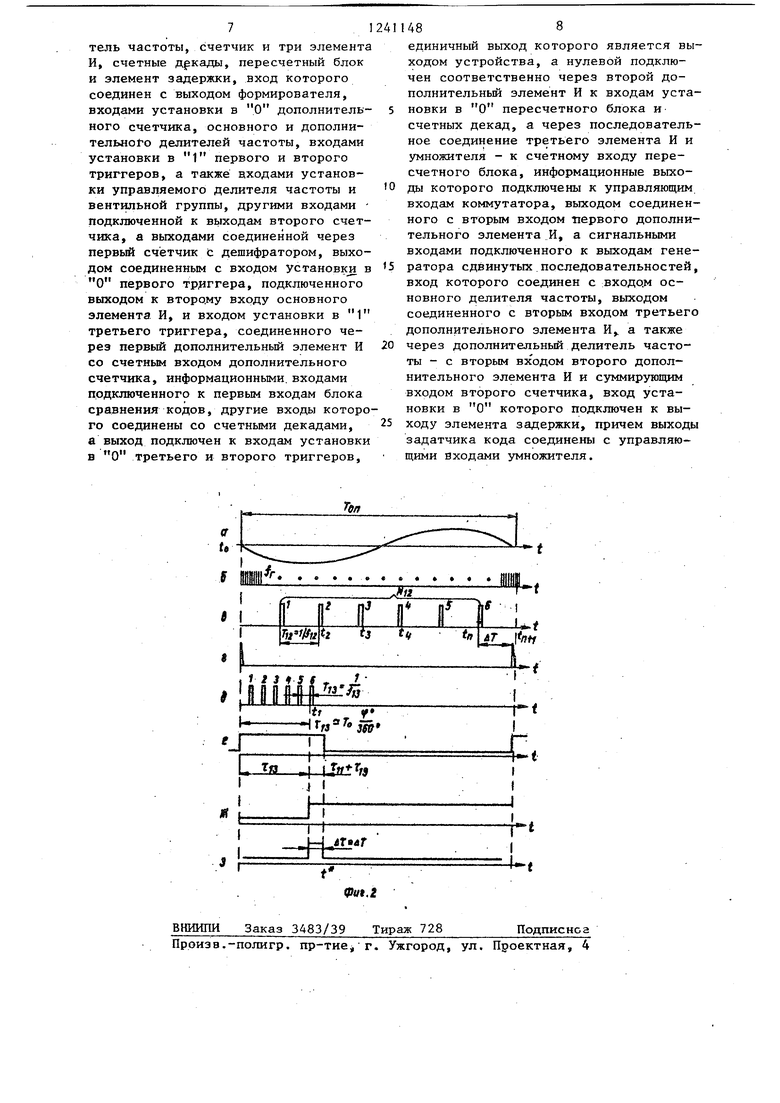

Ни фиг.1 представлена функциональ ая схема цифрового фазосдвигающего усгтройства на - временные соотношения между сигналами при работе устройства 1. ..

Цифровое фазосдвигающее устройство содержит формирователь 1 (коротких импульсов), генератор 2, элемент 3 задержки, дополнительный 4 и основной 5 делители частоты, вентильную группу 6, первый 7 и второй 8 триггеры, дополнительный счетчик 9, основной элемент И 10, генератор 11 сдвинутых последовательностей, второй 12 (суммируняций) и первый 13 (вычитающий) счетчики, дешифратор (кода нуля) 14, третий триггер 15, управляемый делитель 16 частоты, умножитель (числа импульсов) 17, за- датчик 18 кода, блок 19 сравнения кодов, счетные декады 20, пересчетный блок 21, второй 22 и третий 23 дополнительные элементы-И, коммутатор 24 и первый дополнительный элемент И 25. Формирователь 1 коротких импульсов первым входом подключен к входной шине, а вторым входом - к выходу генератора 2, при этом выход формирователя подключен к входу элемента 3 задержки, к входам установки в О делителей 4 и 5 частоты.

к входу управления вентильной группы 40 деленньй угол Ср..., поступает на первый

II л ti. Ав

6, ВХОДУ установки в 1 триггеров 7 и 8 и установки в О счетчика 9. Выход генератора 2 подключен к сигнальным входам делителя 5 частоты, основного элемента И 10 и генератора 11 сдвинутых последовательностей. Выход элемента 3 задержки подключен к входу установки в О суммирующего счетчика 12, счетный вход которого через делитель 4 частоты подключен к выходу делителя 5 частоты, а выходы разрядов через вентильную группу 6, вычитающий счетчик 13 и дешифратор 14 кода нуля - к нулевому входу тригвход формирователя 1 коротких импульсов, который при переходе опорного напряжения через нулевое значение фазы формирует на своем выходе син45 хронно с импульсами сигнала от генератора 2 (фиг. 2J) короткий импульс (фиг. 2z)i Этот короткий импульс поступает на входы установки в О делителей 4, 5 и 16 частоты, которые

50 возвр1ащаются в исходное состояние, на управляющий вход вентильной группы 6, которая срабатьшает и переносит в в 1читающий счетчик 13 код, накоплен- ньтй к этому моменту в суммирующем

гера 7 и единичному входу триггера 15, $5 счетчике 12, на вход установки в О Счетный вход вычитанщего счетчика 13 счетчика .9, который при этом уста- связан с выходом элемента И 10 через навливается в О, на единичные вхо- управляющий делитель 16 частоты, уп- ды триггеров 7 и 8, которые при этом

5

равляющие входы разрядов которого совместно с управляющими входами разрядов умножителя 17 числа импульсов подключены к выходам разрядов задат- чика 18 кода. Информационные выходы счетчика 9 подключены к первым входам блока 19 сравнения кодов, выход которого подсоединен к нулевым входам триггеров 8 и 15. Вторые входы блока 19 сравнения кодов подключены к информационным выходам счетных декад 20, счетный вход которых подключен к выходу умножителя 17 числа импульсов, а вход установки в О вместе с вхрдом установки в О пересчетного блока 21 подключен к выходу дополнительного элемента И 22, первьй вход которого подключен к выходу делителя 4 частоты, а второй вход вместе с вторым входом элемента И 23 -.к нулевому выходу триггера 8. Выходы генератора 11 сдвинутых последовательностей через коммутатор 24, управляющие входы которого подсоединены к выходам разрядов пересчетного блока 21, подключены к первому входу элемента И 25, второй вход которого соединен с выходом триггера 15, а вы- ход подключен к счетному входу счет- 0 чика 9. Второй вход элемента И 10

подключен к выходу триггера 7. Первый .вход элемёьта И 23 подключен к выходу делителя 5 частоты. Единичный выход триггера 8 является выходом фазосдви- гакицего устройства.

Устройство работает следующим образом.

Опорный сигнал (фиг. 2а), фазу которого необходимо сдвинуть на опре0

5

5

. Ав

вход формирователя 1 коротких импульсов, который при переходе опорного напряжения через нулевое значение фазы формирует на своем выходе синхронно с импульсами сигнала от генератора 2 (фиг. 2J) короткий импульс (фиг. 2z)i Этот короткий импульс поступает на входы установки в О делителей 4, 5 и 16 частоты, которые

возвр1ащаются в исходное состояние, на управляющий вход вентильной группы 6, которая срабатьшает и переносит в в 1читающий счетчик 13 код, накоплен- ньтй к этому моменту в суммирующем

3

переходят из нулевого состояния в единичное, благодаря чему на выходе триггера 7 появляется разрешакщий потенциал для элемента И 10, а на выходе триггера 8, являющемся выко- домустройстйа -высокий цотенциал, и на элемент 3 задержки. Будучи задержанным в элементе 3 задержки на время Гл , достаточное для надежной перезаписи кода из счетчика 12 в вы- читающий счетчик 13, этот короткий импульс с выхода формирователя 1 поступает на вход установки в О сум- мирукицего счетчика 12, в результате чего последний переходит в исходное нулевое состояние.

Таким образом, начиная с момента появления на выходе формирователя 1 короткого импульса, на суммирукиций вход счетчика 12 начинают поступать импульсные сигналы (фиг. 2Ь) в частотой

где fj,- частота следования импульсов на выходе генератора 2j

К., Ку - коэффициенты деления делителей 4 и 5 частоты соответственно.

а на счетный вход вычитающего счетчика 13 начинают поступать импульсные сигналы (фиг. 2а) с частотой f,, где - коэффициент деления .частоты управляемого делителя 16 35 частоты, который задается задатчиком 18 кода.

За период Тд„ входного опорного сигнала U в суммирующем счетчике 12 накапливается код числа N (Фиг. 2&),0 причем.

Ton- ft

к,, к,

Этот код числа N , из вычитакяцего счетчика 13 вычитается до нуля за время Т, (фиг. 2а, от to до t, ), причем

п

N

14 Трп- f П

К

к.-к.

16

Т,

к.

16

13 1 г И

В момент полного вычитания кода N,, из вычитающего счетчика 13 код счетчика становится.равньм нулю, в результате чего срабатывает дешифратор 14 кода нуля и его выходной сигнал поступает на нулевой вход тригге484 .

ра 7, который переходит в нулевое состояние и снимает разрешающий потенциал с элемента И 10, а также на единичный вход триггера 15, который переходит в единичное состояние и подает разрешающий потенциал на элемент И 25.

Если Kj,- Kg сделать равным 360, то интервал времени , в течение которого на выходе триггера 7 существует высокий потенциал, соответствует фа- эовому сдвигу напряжения U , причем число градусов этого фазового сдвига соответствует числу, код которого заает задатчик 18. кода, т.е.

Т - Т П 04

0

5

0

5

0

5

0

5

Знак примерного равенства в этом выражении поставлен потому, что интервал Т.- соответствует целому числу периодов импульсного сигнала на выходе управляемого делителя 16 частоты, но в длительности периода Т опорного входного напряжения укладывается не целое количество периодов импульсных сигналов с выхода делителя 4 частоты. Между поступлением на счетный вход суммирзгющего счетчика 12 последнего за импульса (t;, на фиг. 2г) и моментом его обнуления (tf,., на фиг. 2г) обычно имеется дополнительный интервал л Т (фиг. 2&), меньший периода T,,g , который необходимо учесть путем формирования некоторого дополнительного интервала

СРсдц

дол З60 суммирования его с

интервалом Т„. Сумма Т, и ЛТд наи- - более точно соответствует величине пЧ сАе/ЗбО. Для формирования интервала лТддп и его суммирования с интервалом Т предназначены элементы предлагаемого устройства.

В установившемся режиме, например,, в любой интервал Т,, начиная с момента времени tj до момента времени tp (фиг.23), в момент отработки временного сдвига в предвдущем периоде Tjjjj опорного входного напряжения (или с , на фиг. 2а) на основном (единичном) выходе триггера 8 устанавливается нулевой потенциал, а на втором его выходе появляется положительный потенциал, который поступает на элементы И 22 и 23 и открывает их. Через элемент И 23 на вход умно- .

жителя 17 числа и myльcoв поетупает импульсная последовательность с выхода делителя 5 частоты, следующая с частотой, в Kjj раза большей, чем частота сигналов на входе суммирующего счетчика 12. Каждому импульсу, поступившему на вход умножителя 1.7, на его выходе соответств ует последовательность импульсов, число которых равно числу, код которого К имеется в задатчике кода. Эти импульсы с выхода умножителя 17 поступают на вход пересчетного бАока 21, а с его выхода - на вход счетных декад 20. .

Через элемент И 22 на входы установки в О счетных декад 20 и блока 21 поступают импульсные сигналы с выхода делителя 4 частоты. Таким образом, код, записанный в счетных де- кадах 20 и блоке 21 меняется от (момент t| на фиг. ) после первого импульса на входе умножителя 17 до (K4-i)K,g.

В дальнейшем, начиная с момента времени ty, (фиг. 2В) от нуля начнет изменяться код, фиксируемый в с.четны декадах 20 и блоке. 21, после прихода последнего в интервале Т импульса на вход суюофующего счетчика 12. Од нако после поступления на вход умно- жителя 17 некоторого количества К импульсов (меньшего К), формирователь 1 коротких импульсов вырабатывает сигнал, которым триггер 8 перево- дится в единичное состояние, снимая тем самым разрешаюце напряжение с - первых входов элементов И 22 и 23. В счетных декадах 20 и блоке 21 фикси- .руется код К. Этот код сохраняется до момента перехода триггера 7 из единичного положения в нулевое, т.е. к концу отработки 1 нтервала (момент t, на фиг. 2а).

В момент отработки Т, , когда де- шифратор 14 кор,а нуля вырабатывает свой сигнал (фиг. 2), этот сигнал поступает на единичный вход триггера 15 и переводит последний в единичное состояние (фиг. 2э), при котором на элемент И 25 подается разрешающий потенциал. К этому времени коммута- . тор 24 подключает на вход элемента И 25 тот выход (шестой выход для примера tA 0,6Т) генератора 11 сдвину- тых последовательностей, номер которого соответствует числу, код кото- Doro записан в разрядах пересчетного

блока 21, Эта последовательность (для выбранного примера 2 импульса) с частотой fJ начинает поступать на счетный вход счетчика 9. Как только код счетчика 9 сравняется с кодом, зафиксированным в счетных декадах 20, срабатывает блок 19 сравнения кодов, сигнал которого переводит в нулевое состояние триггер 15 (момент t на фиг. 20), снимая разрешанщее напряжение с элемента И 25, и поступает на нулевой вход триггера 8 (фиг. 2е), переводя его в нулевое состояние и фиксируя тем самым момен времени, сдвинутый относительно начала периода на заданный YTonff. .

Относительно импульса формирователя 1 этот момент времени сдвинут на + Т„ (фиг. 2е), где ,, -длительность единичного состояния триггера 7i i,, - интервал времени, равный сдвигу выходной последовательности .коммутатора 24 относительно входной последовательности генератора 11 а f,. - временной интервал от момента поступления на счетчик 9 первого счетного импульса до момента формирования в нем кода числа, записанного в счетных декадах 20. Интервал, в течение которого открыт элемент И 25, равный сумме ;, +ц, , представляет собой интервал А (фиг. 2е) , который дополняет ,, до уточненного значения временного сдвига.

Формула изо бретения

Цифровое ,фазосдвигающее устройство, содержащее первый и второй счётчики, задатчик кода, соединенный с информационными входами управляемого делителя частоты, вход которого сое-г динен с выходом основного элемента Я BXQ; которого объединен с входом основного делителя частоты и выходом генератора импульсов, соединенного с формирователем, вход которого соединен с входной клеммой устройства, причем выход управляемого делителя частоты соединен с управляющим входом первого счетчика, отличающееся тем,-что, с целью повьше- ния точности, в него введены генератор сдвинутых последовательностей, коммутатор, умножитель, вентильная группа, дешифратор, блок сравнения кодов, триггеры, дополнительные делитель частоты, счетчик и три элемента И, счетные декады, пересчетный блок и элемент задержки, вход которого соединен с выходом формирователя, входами установки в О дополнительного счетчика, основного и дополнительного делителей частоты, входами установки в 1 первого и второго триггеров, а также входами установки управляемого делителя частоты и вентильной группы, другими входами - подключенной к выходам второго счетчика, а выходами соединенной через первый счётчик С дешифратором, выходом соединенным с входом установку в О первого триггера, подключенного выходом к второму входу основного элемента И, и входом установки в 1 третьего триггера, соединенного через первый дополнительный элемент И со счетным входом дополнительного счетчика, информационными, входами подключенного к первым входам блока сравнения кодов, другие входы которого соединены со счетными декадами, а выход подключен к входам установки в О третьего и второго триггеров.

2411488

единичный выход которого является выходом устройства, а нулевой подключен соответственно через второй дополнительный элемент И к входам уста- 5 новки в О пересчетного блока и

счетных декад, а через последовательное соединение третьего элемента И и умножителя - к счетному входу пересчетного блока, информационные выхо 0 ды которого подключены к управляющим входам коммутатора, выходом соединенного с вторым входом первого дополнительного элемента И, а сигнальными входами подключенного к выходам гене15 ратора сдвинутых последовательностей, вход которого соединен с входом основного делителя частоты, выходом соединенного с вторым входом третьего дополнительного элемента И,, а также

20 через дополнительный делитель частоты - с вторым входом второго дополнительного элемента И и суммирующим входом второго счетчика, вход установки в О которого подключен к вы25 ходу элемента задержки, причем выходы эадатчика кода соединены с управляющими входами умножителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотомер | 1982 |

|

SU1190285A1 |

| Цифровой частотомер | 1985 |

|

SU1275314A2 |

| Цифровой измеритель отношения частот | 1982 |

|

SU1177762A1 |

| Программируемый преобразователь код-фаза | 1984 |

|

SU1236389A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Цифровой измеритель отношения временных интервалов | 1981 |

|

SU1027692A2 |

| Электронно-счетный измеритель частоты следования импульсов | 1973 |

|

SU479047A1 |

| Одноканальное устройство для управленияВЕНТильНыМ пРЕОбРАзОВАТЕлЕМ | 1979 |

|

SU839007A1 |

| Цифровой измеритель частоты | 1980 |

|

SU938187A1 |

| Цифровое устройство для анализа химического состава чугуна | 1985 |

|

SU1374247A1 |

Изобретение относится к импульсной технике, в частности к измерительным устройствам для задания фазового сдвига электрических сигналов. Цель изобретения - повышение точности фазового сдвига - достигается путем уменьшения погрешности дискретизации установки заданного фазового сдвига. Устройство содержит формирователь 1 коротких импульсов, генератор 2, элемент задержки 3, дополни- тельньй 4, основной 5 и управляемый 16 делители часто ты, вентильную группу 6, триггеры 7, 8 и 15, счетчики: дополнительный 9, суммируниций 12 и вычитанщий 13, логические элементы И 10, 22, 23 и 25, генератор 11 сдвинутых последовательностей, дешифратор 14, умножитель 17, задатчик кода 18, блок 19 сравнения кодов, счетные декады 20, счетный блок 21, коммутатор 24. Работа устройства поясняется по временным диаграммам в описании изобретения. 2 ил. (Л

6/Г

1 2 3 5 ( f J.

ШГ;

| Авторское свидетельство СССР №759878, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровое фазосдвигающее устройство | 1981 |

|

SU983577A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-06-30—Публикация

1984-12-30—Подача