11

Изобретение относится к вычислительной технике и может быть использовано для моделирования цроцессрв на сетевых г рафиках,

Цель изобретения - упрощение и по- вышение быстродействия устройства.

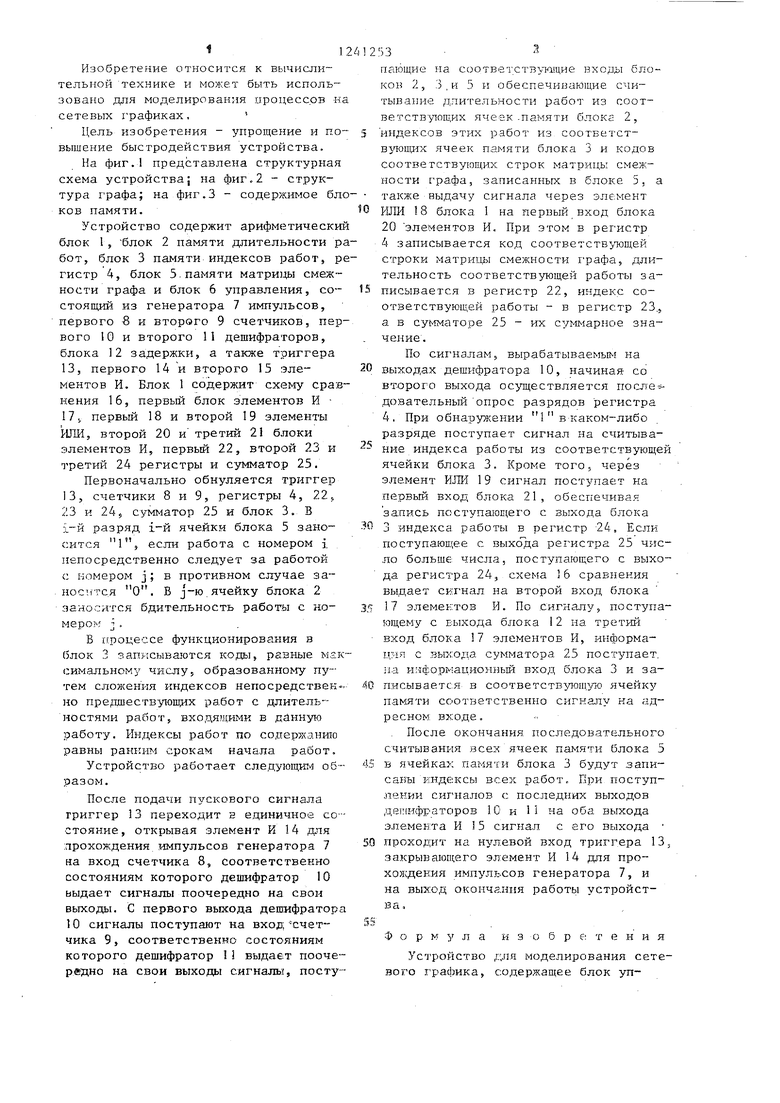

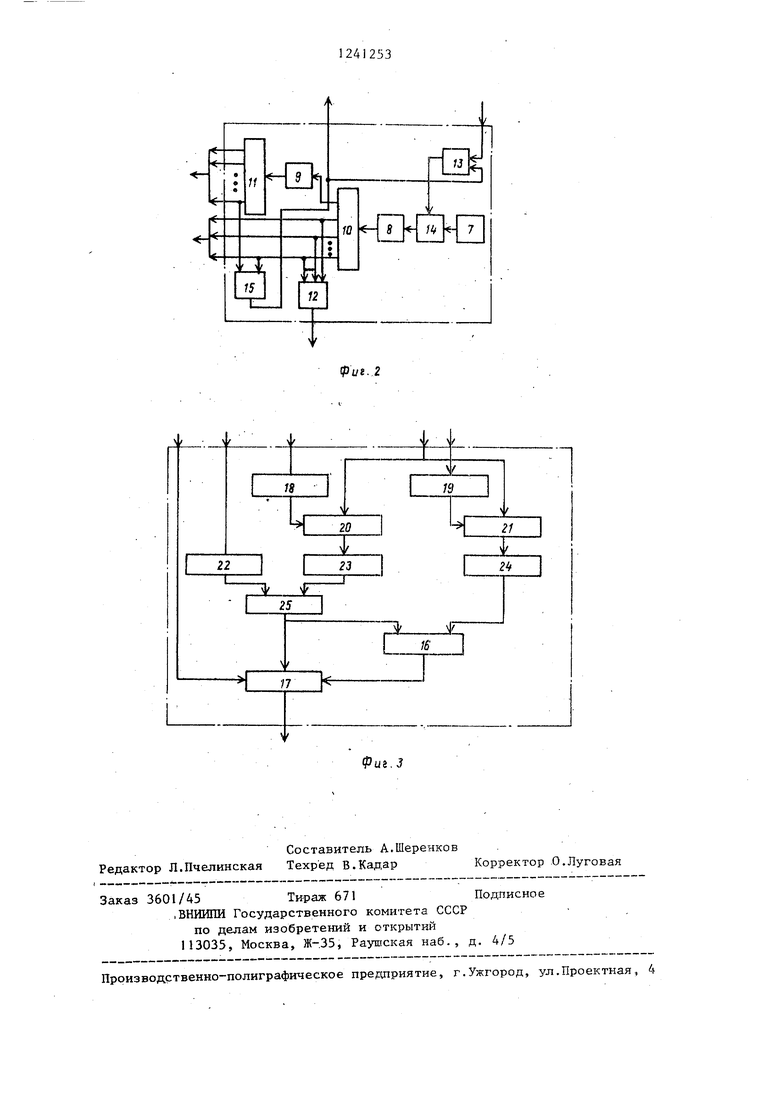

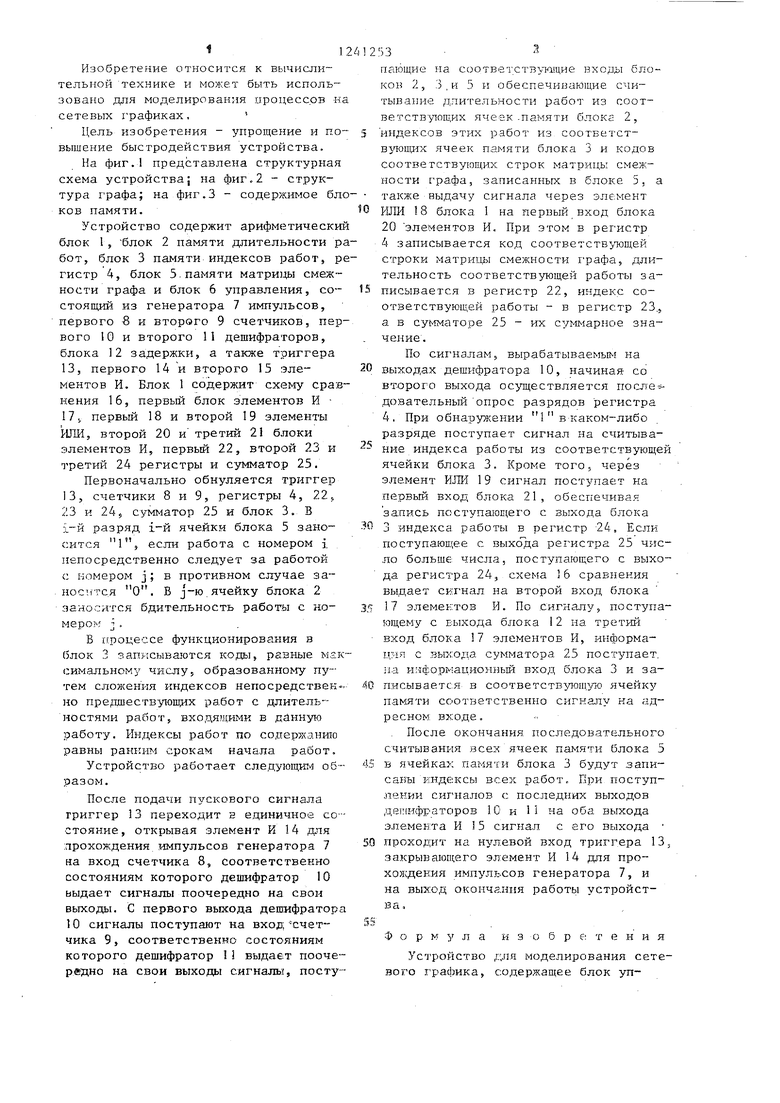

На фиг.1 представлена структурная схема устройства; на фиг,2 - структура графа; на фиг.З - содержимое бло ков памяти.

Устройство содержит арифметический блок 15 блок 2 памяти длительности работ, блок 3 памяти индексов работ, регистр 4, блок 5. памяти матри1ДЬ смежности графа и блок 6 управлепия, со- стоящий из генератора 7 импульсов, первого в и второго 9 счетчиков, первого 10 и второго 11 дешифраторов, блока 12 задержки, а также триггера 13, первого 14 и второго 15 эле- ментов И. Блок 1 содержит схему сравнения 16, первый блок элементов И 17,, первый 18 и второй 19 элементы РШИ, второй 20 и третий 21 блоки элементов И, первьш 22, второй 23 и третий 24 регистры и сумматор 25,

Первоначально обнуляется триггер 13, счетчики 8 и 9, регистры 4, 22, 23 и 24, сумматор 25 и блок 3, В i-й разряд i-й ячейки блока 5 зано- сится 1, если работа с номером i непосредственно следует за работой с номером J; в противном случае за НОС11ТСЯ О. В j-ю ячейку блока 2 заносится бдительность работы с но- мером j..

В процессе функционирования в блок 3 записываются коды, равные максимальному числу, образованному путем сложения индексов непосредствен-. но предшествующих работ с длительностями работ, входящими в данную работу. Индексы работ по содержанию равны ранит- срокам начала работ.

Устройство работает следующизу об- разом.

После подачи пускового сигнала триггер 13 переходит н единичное со-- стояние, открывая элемент И 14 для прохождения импульсов генератора 7 на вход счетчика 8, соответственно состояниям которого дешифратор 10 выдает сигналы поочередно на свон выходы. С первого выхода дешифратора 10 сигналы поступают на вход счет- чика 9, соответственно состояниям которого дешифратор выдает поочередно на свои выходы сигналы, поступз-ющие на соответствумцие входат блоков 2, 3,и 5 1 обеспечивающие считывание длительности работ из соот- ветств утощих ячеек-памяти блока 2, индексов этих работ из соответст- в пощих ячеек памяти блока 3 и кодов соответствующих строк матрицы смежности графа, записанных в блоке 5, а также выдачу сигнала через элемент Ш1И 18 блока 1 на первый вход блока 20 элементов И. При этом в регистр 4 записывается код соответств тощей строки матрицы смежности графа, длительность соответствующей работы записывается в регистр 22, индекс соответствующей работы - в регистр 23., а в суиматоре 25 - их суммарное значение.

По сигналам, вырабатываемым на выходах дешифратора 10, начинай со второго выхода осуществляется после - довательный опрос разрядов регистра 4. При обнаружении 1 в каком-либо разряде поступает сигнал на считывание индекса работы из соответствующе ячейки блока 3. Кроме того, через элемент ЯЛК 19 сигнал поступает на первый вход блока 21, обеспечивая запись nocTynaraniero с выхода блока 3 индекса работы в регистр 24, Если поступающее с выхбда регистра 25 число больше числа, поступающего с да регистра 24., схема 16 сравнения выдает сигнал на второй вход блока 17 элементов И. По сигналу, поступающему с выхода блока 2 на третий вход блов;а 17 элементов И, информа- цип с зьпсода сумматора 25 поступает, па и;-га;ор ;ационный вход блока 3 и записывается в соответств:;лош,ую ячейкз памяти соответственно сигналу на адресном; входе.

, После окончания последовательного считывания всех ячеек памяти блока 5 в ячейках памнти блока 3 будут запи- сакы индексы всех работ. При поступлении сигналов с последних выходов дешифраторов 1C и П на оба выхода элемента И 15 сигнал с его выхода проходит на нулевой вход триггера 13 закрывающего элемент И 14 для про- холсдения импульсов генератора 7, и на выход окончания работы устройства.

Формула изобретения

Устройство для моделирования сетевого графика, содержащее блок уп

3

равления, арифметический блок, блок памяти длительности работ, блок памяти индексов работ и регистр, выход которого соединен с входом считывания блока памяти индексов работ, о т личающееся тем, что, с целью упрощения и повышения быстродействия, в устройство введен блок памяти матрицы смежности графа, блок управления состоит из генератора импульсов, первого и второго счетчиков, первого и второго дешифраторов, блока задержки, триггера, первого и второго элементов И, арифметический блок состоит из схемы срав- нения, первого, второго и третьего блоков элементов И, первого и второг элементов ИЛИ, первого, второго, третьего регистров и сумматора, причем в -блоке управления единичный вход триггера является пусковым входом устройства, выход триггера под- ключен к первому, а выход генератора импульсов - к второму входам первого элемента И, выход которого соеди- ней со счетным входом первого счетчика, выход которого подключен к входу первого дешифратора, первый выход которого соединен со счетным входом второго счетчика, выход кото- рого подключен к входу второго дешифратора, выходы первого.дешифратора, начиная с второго, соединены с входами блока задержки, последние выходы первого и второго дешифраторов под1 лючены к первому и второму входам второго элемента.И соответственно, выход которого объединен с нулевым входом триггера и является выходом окончания работы устройства, в арифметическом блоке выходы первого

253 4

1и второго элементов ШШ соединены с первым входами соответственно второго и третьего блоков элементов И, выходы которых подключены к информационным входам соответственно второго и третьего регистров, выход первого регистра соединен с первым, выход второго регистра с вторым входами сумматора, выход которого подключен к первому входу первого блока элементов И и первому входу схемы сравнения, второй вход и выход которой соединены соответственно с выходом третьего регистра и вторым входом первого блока элементов И, раз- рядньш выход второго дешифратора блока управления подключен к адресным входам блока памяти матрицы смежное ти графа, блока памяти длительности работ, блока памяти индексов работ и к входу первого элемента ИЛИ ариф- метического блока, разрядный вькод первого,дешифратора блока управления соединен с входом считывания, а выход блока памяти матрицы смежности графа - с Ш1формационными«входами регистра, выход блока задержки блока управления подключен к третьему входу первого блока элементов И арифметического блока, выход регистра соединен с входом второго элемента ШШ арифметического блока, выход блока памяти длительности работ,;; подключен iK информационному входу первого регистра арифметического блока, а информационные вход и выход блока памяти индексов работ соединены соответственно с выходом первого блока элементов И и вторыми входами второго и третьего блоков элементов арифметического блока.

Изобретение относится к области вычислительной техники и может быть использовано для моделирования процессов на сетевых графиках. Цель изобретения состоит в упрощении и повышении быстродействия устройства. Устройство содержит арифметический блок 1, блок 2 памяти длительности работ, блок 3 памяти индексов работ,- регистр 4, блок 5 памяти матрицы смежности графа и блок 6 управления, состоящий из генератора импульсов, первого и второго счетчиков, первого и второгЪ дешифраторов, элемента задержки, триггера, первого и второго элементов И. Арифметический блок содержит схему сравнения, первый блок элементов И, первый и второй элементы ИЛИ, второй и третий блоки элементов И, первый, второй и третий регистры, .сумматор. Упрощение и повышение быстродействия устройства до- с игаются благодаря введению блока 5 и сокращению числа операций записи и считывания информации. 3 ил. с S 1 t JcL ГО ел САР

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СЕТЕВОГО ГРАФИКА | 0 |

|

SU279173A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования сетевого графика | 1977 |

|

SU686033A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-30—Публикация

1984-04-09—Подача