1

Изобретение относится к имйульс- ной технике,,и может быть использовано в радиоимпульсных вычислительных устройствах с амплитудным представлением информации, работаювщх в сверхвысокочастотномдиапазоне.

Цель изобретения - расширение функциональных возможностей за счет увеличения коэффициента объединения по входу и количества одновременно выполняемых логических операций.

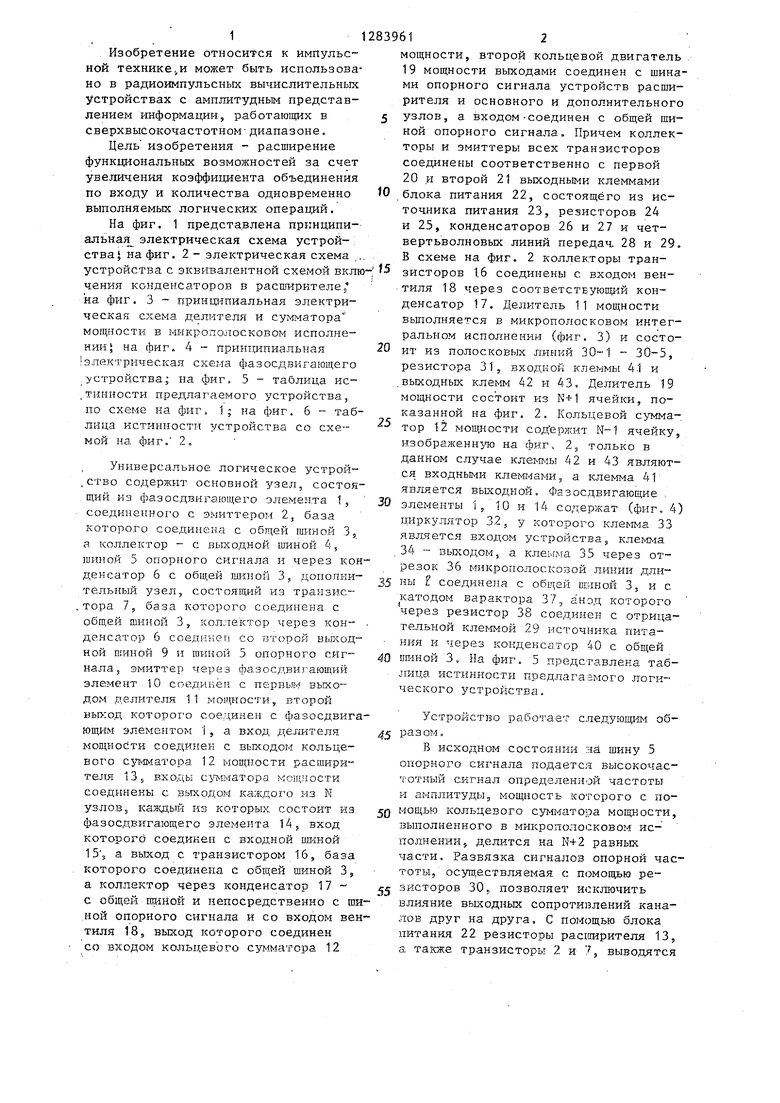

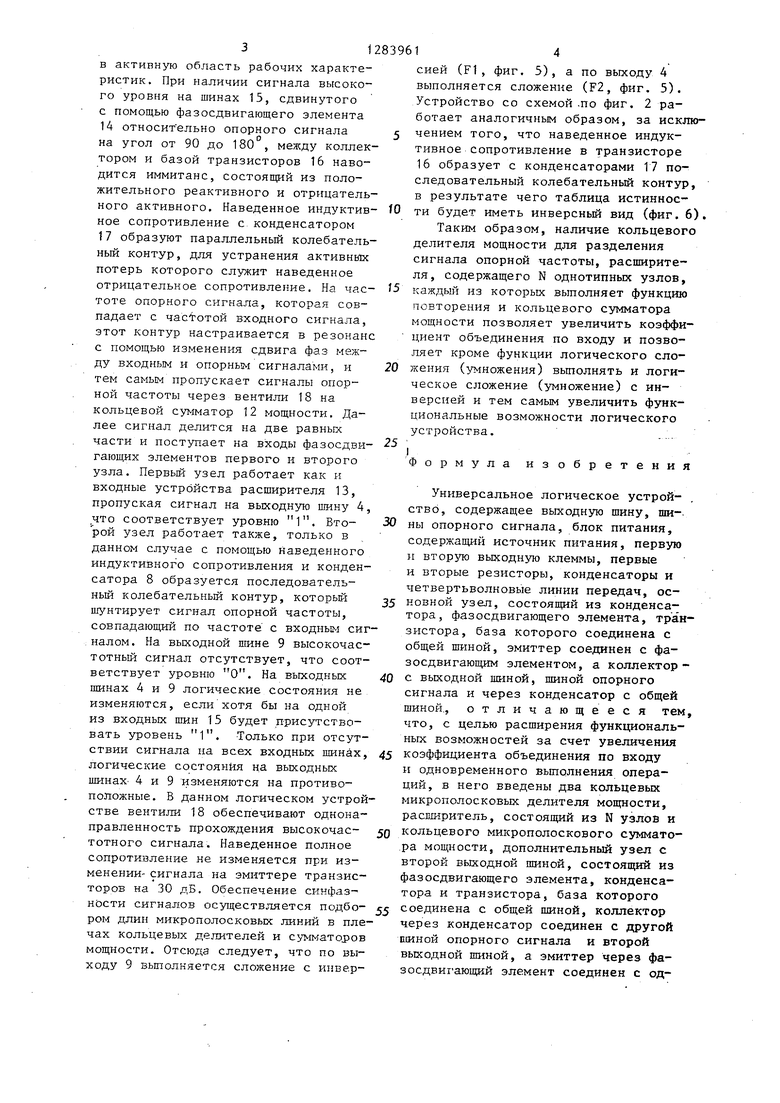

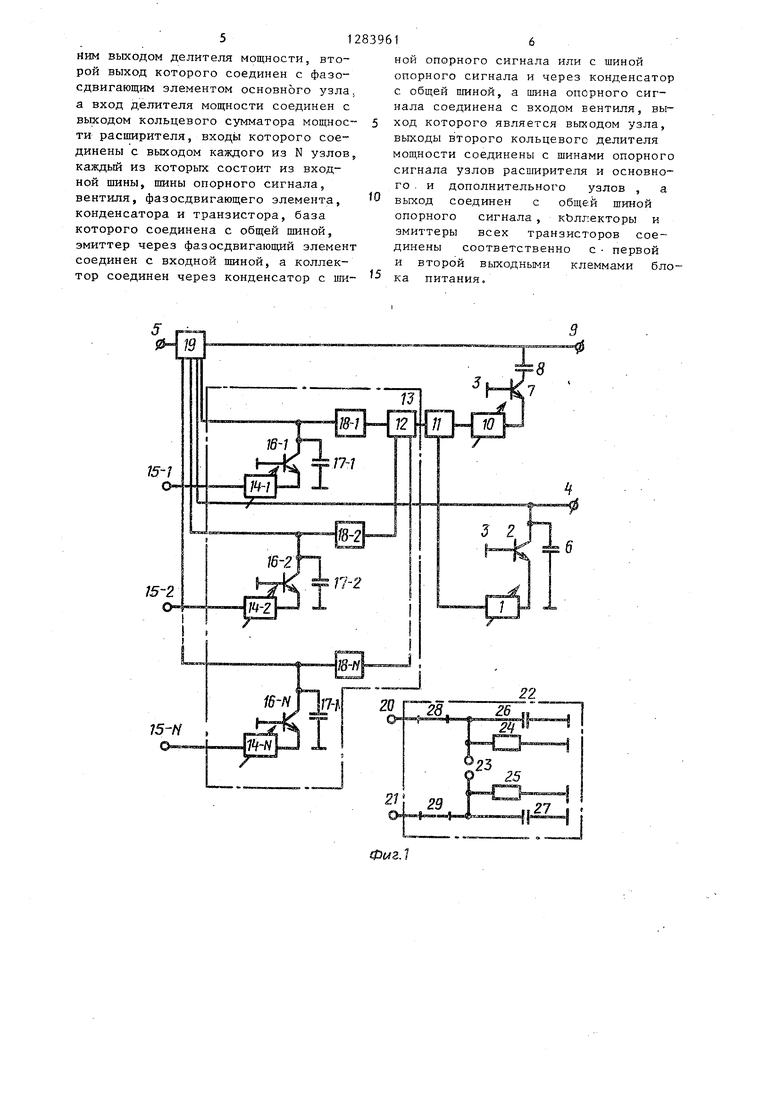

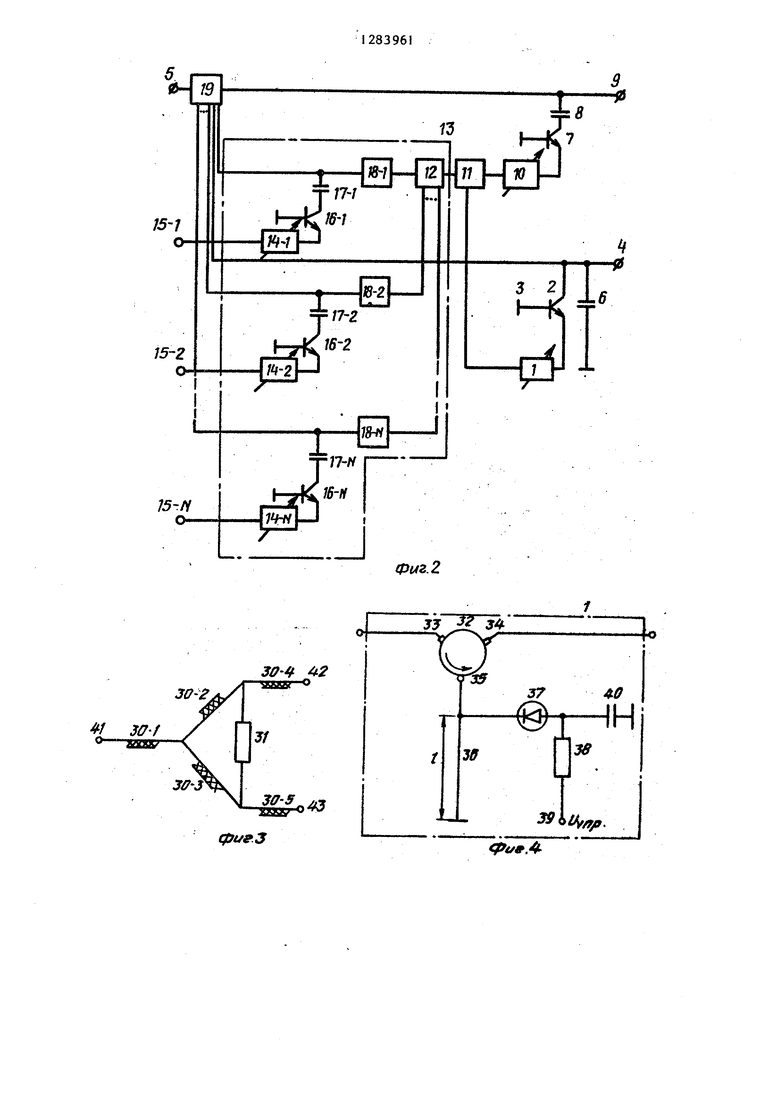

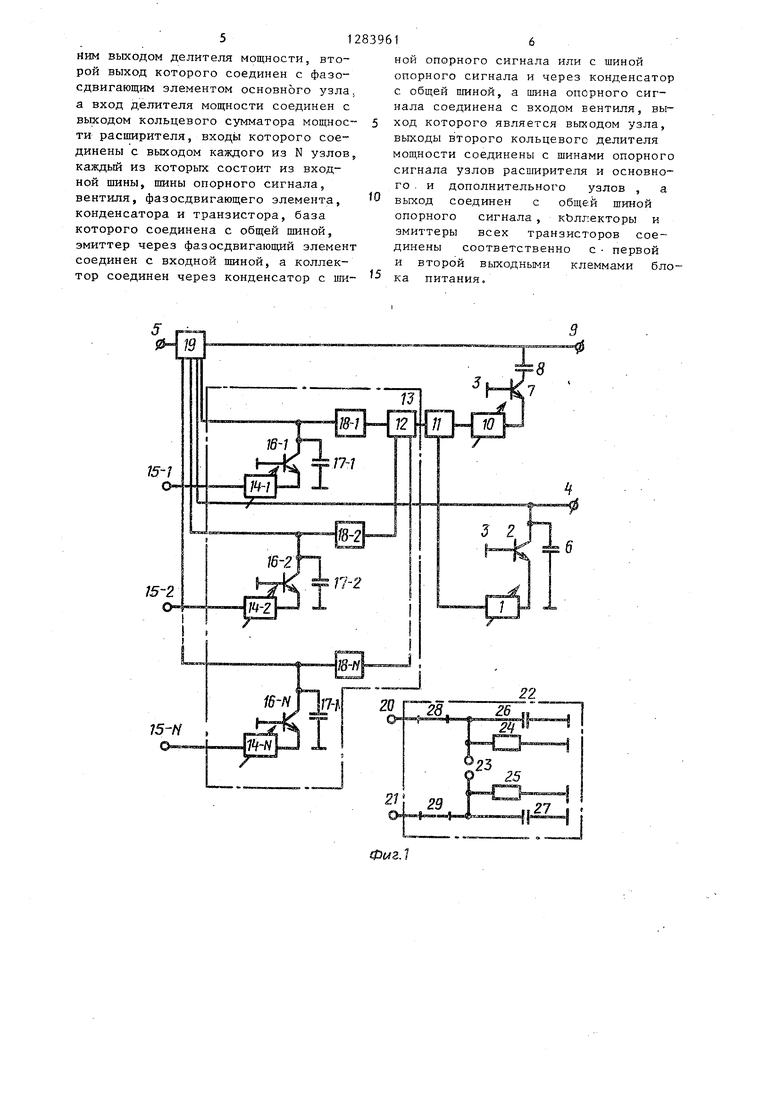

На фиг. 1 представлена принципиальная электрическая схема устройства на фиг. 2 - электрическая схема .

12839612

мощности, второй кольцевой двигатель

19мощности выходами соединен с шина ми опорного сигнала устройств расширителя и основного и дополнительного

5 узлов, а входом-соединен с общей шиной опорного сигнала. Причем коллекторы и эмиттеры всех транзисторов соединены соответственно с первой

20и второй 21 вьЕХОдньзми клеммами О блока питания 22, состоящего из источника питания 23, резисторов 24

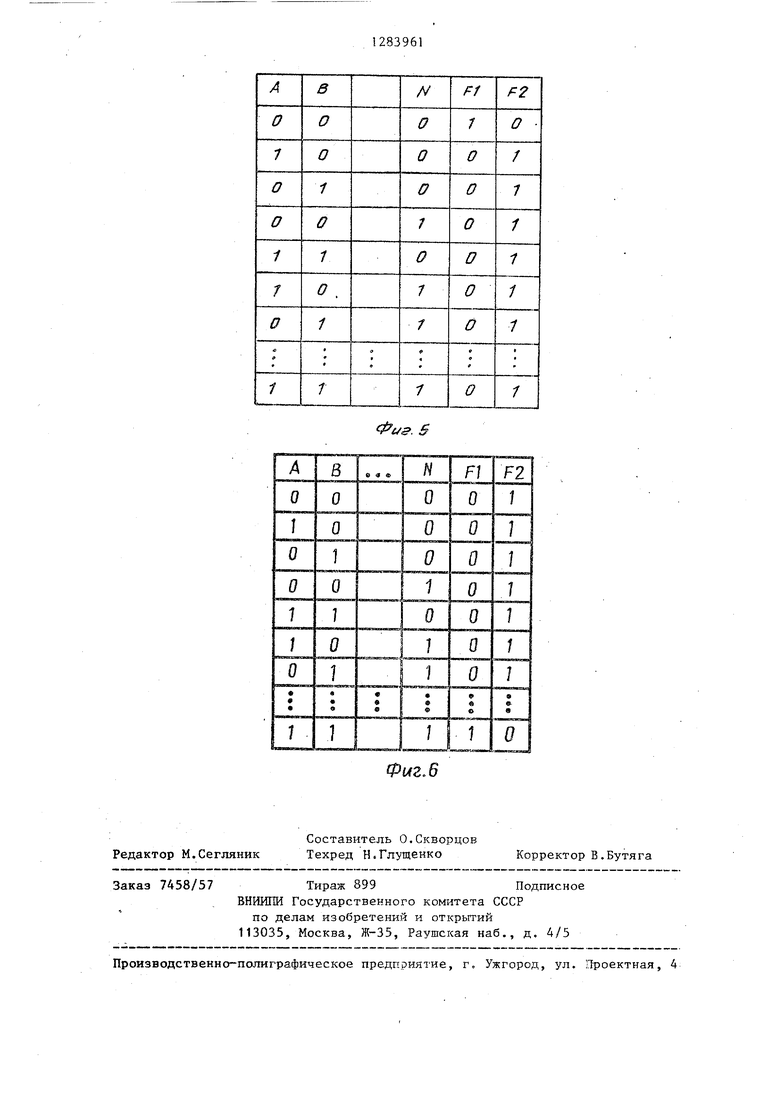

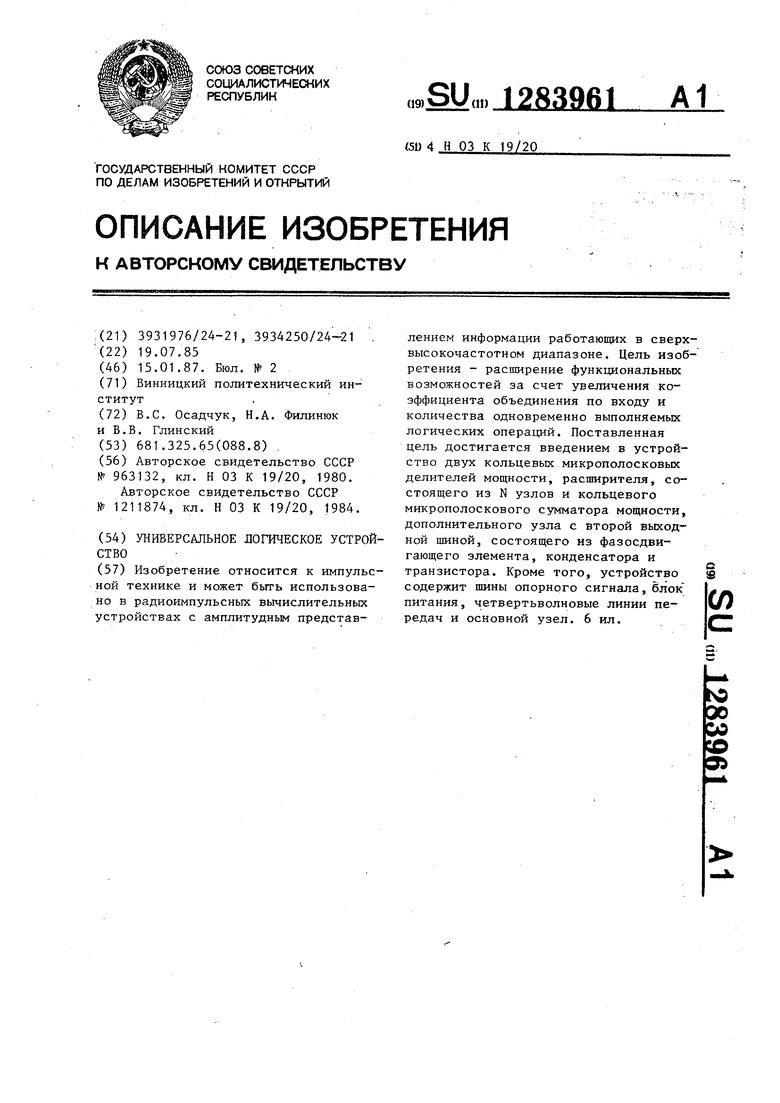

и 25, конденсаторов 26 и 27 и четвертьволновых линий передач. 28 и 29. В схеме на фиг. 2 коллекторы транустройства с эквивалентной схемой вклю- 5 зисторов 1.6 соединены с входом венчения конденсаторов в расширителе. на фиг. 3 принципиальная электрическая схема делителя и сумматора мощности в микрополосковом исполнении; на фиг 4 - принципиальная электрическая схема фазосдвигающего /устройства; на фиг, 5 - таблица ис- ,тинности предлагаемого устройства, по схеме на фиг, 1j на фиг. 6 таблица исти п1ост11 устройства со схе-- мой на фиг. 2,

Универсальное логическое устрой- ,ство содержит основной узел, состоящий из фазосдвигающего элемента 1, соединенного с эмиттером 2, база которого соединена с общей шиной 3, а коллектор - с выходной 1пиной 4, шиной 5 опорного сигнала и через конденсатор 6 с общей шиной 3, дополнительный узел, состоящий из транзистора 7, база которого соединена с общей шиной 3, коллектор через кон- . денсатор 6 соединен со второй выходной шиной 9 и шиной 5 опорного сигнала, эмиттер через фазосдвигающий элемент 10 соединён с первьи-. выходом делителя 11 моищости, второй которог о соединен с фазосдвига- ющим элементом 1, а вход делителя мощности соединен с выходом кольцевого cyiviMaTopa 12 мощности расширителя 13s входы ci,T fiviaTopa кс цности соединены с выходом каждого из N узлов, каждьш из которььч состоит из фазосдвигающего элемента 14, вход которого соединен с входной шиной 15, а выход с транзистором 16, база

которого соединена с общей шиной 3, а коллектор через конденсатор 17 с общей гои11ой и непосредственно с ши- ,ной опорного сигнала и со входом вен тиля 18, выход icoToporo соединен со входом кольцевого сумматора 12

2839612

мощности, второй кольцевой двигатель .

19мощности выходами соединен с шинами опорного сигнала устройств расширителя и основного и дополнительного

5 узлов, а входом-соединен с общей шиной опорного сигнала. Причем коллекторы и эмиттеры всех транзисторов соединены соответственно с первой

20и второй 21 вьЕХОдньзми клеммами О блока питания 22, состоящего из источника питания 23, резисторов 24

и 25, конденсаторов 26 и 27 и четвертьволновых линий передач. 28 и 29. В схеме на фиг. 2 коллекторы тран 5 зисторов 1.6 соединены с входом вентиля 18 через соответствующий конденсатор 17. Делитель 11 мощности выполняется в микрополосковом интегральном исполнении (фиг. 3) и состоит из полосковых линий 30-1 - 30-5, резистора 31, входной клеммы 41 и выходных клемм 42 и 43. Делитель 19 мощности состоит из N+1 ячейки, показанной на фиг. 2. Кольцевой о мматор 12 моЕгности содержит N-1 ячейку, изображенн то на фиг. 2, только в данном случае кле№.1ы 42 и 43 являются входными клем- ами, а клемма 41 является выходной. Фазосдвигающие .

элементы 1/10 и 14 содержат (фиг, 4) циркулятор 32, у которого клемма 33 является входом устройства, клемма 34 - выходом 5 а клег.17.а 35 через отрезок 36 мякрополоскозой линии длины I соединена с общей ЦБШОЙ 3, и с катодом варактора 37, анод которого через резистор 38 соединен с отрицательной клеммой 29 источника пита- ния и через конденсатор 40 с общей

гшной 3. На фиг. 5 представлена таблица истинности предлагаамого логического устройства.

Устройство работает следуюш;1 м образом,

В исходном состоянии на шину 5 опорного сигнала подается высокочас- 7 отный сигнал определенной частоты и амплитуды, мoщIiocть которого с помощью кольцевого сум1мгатора мощности, выполненного в микрополосковом исполнении, делится на N+2 равных части. Развязка сигналов опорной частоты, осуществляемая с помощью резисторов 30. позволяет исключить влияние выходных сопротюзлений каналов друг на друга. С помощью блока питания 22 резисторы расширителя 13, а также транзисторы 2 и 7, выводятся

в активную область рабочих характеристик. При наличии сигнала высокого уровня на шинах 15, сдвинутого с помощью фазосдвигающего элемента 14 относит ельно опорного сигнала на угол от 90 до 180 , между коллектором и базой транзисторов 16 наводится иммитанс, состоящий из положительного реактивного и отрицательного активного. Наведенное индуктивное сопротивление с,конденсатором 17 образуют параллельньш колебательный контур, для устранения активнвйс потерь которого служит наведенное отрицательное сопротивление. На частоте опорного сигнала, которая совпадает с частотой входного сигнала, этот контур настраивается в резонанс с помощью изменения сдвига фаз между входным и опорньм сигналами, и тем самым пропускает сигналы опорной частоты через вентили 18 на кольцевой сумматор 12 мощности. Далее сигнал делится на две равных части и поступает на входы фазосдви- гающих элементов первого и второго узла. Первый узел работает как и входные устройства расширителя 13, пропуская сигнал на выходную ишну 4, что соответствует уровню 1. Второй узел работает также, только в данном случае с помощью наведенного индуктивного сопротивления и конденсатора 8 образуется последовательный колебательный контур, которьм шунтирует сигнал опорной частоты, совпадающий по частоте с входным сиг ,налом. На выходной шине 9 высокочастотный сигнал отсутствует, что соответствует уровню О. На выходных шинах 4 и 9 логические состояния не изменяются, если хотя бы на одной из входных шин 15 будет присутствовать уровень 1

Только при отсутствии сигнала на всех входных шинах, логические состояния на выходных шинаХ 4 и 9 изменяются на противоположные. В данном логическом устройстве вентили 18 обеспечивают однонаправленность прохождения высокочастотного сигнала. Наведенное полное сопротивление не изменяется при изменении- сигнала на эмиттере транзисторов на 30 дБ. Обеспечение синфаз- ности сигналов осу1дествляется подбором длин микрополосковых линий в плечах кольцевых делителей и сумматоров мощности. Отсюда следует, что по выходу 9 выполняется сложение с инверсией (F1 , фиг. 5), а по выходу 4 выполняется сложение (F2, фиг. 5). Устройство со схемой .по фиг. 2 работает аналогичным образом, за исклю5 чением того, что наведенное индуктивное сопротивление в транзисторе 16 образует с конденсаторами 17 последовательный колебательный контур, в результате чего таблица истинносO ти будет иметь инверсный вид (фиг. 6).

Таким образом, наличие кольцевого делителя мощности для разделения сигнала опорной частоты, расширителя, содержащего N однотипных узлов,

5 каждьй из которых выполняет функцшо повторения и кольцевого сумматора мощности позволяет увеличить коэффи- циент объединения по входу и позволяет кроме функции логического сло- 0 жения (умножения) выполнять и логическое сложение (умножение) с инверсией и тем самым увеличить функциональные возможности логического устройства.

,

Формула изобретения

Универсальное логическое устрой- , ство, содержащее выходную шину, ши-.

0 ны опорного сигнала, блок питания, содержащий источник питания, первую и вторую выходную клеммы, первые и вторые резисторы, конденсаторы и четвертьволновые линии передач, ос5 ионной узел, состоящий из конденсатора, фазосдвигающего элемента, транзистора, база которого соединена с общей шиной, эмиттер соединен с фа- зосдвигающим элементом, а коллектор 0 с выходной шиной, шиной опорного сигнала и через конденсатор с общей шиной., отличающееся тем, что, с целью расширения функциональных возможностей за счет увеличения

5 коэффициента объединения по входу и одновременного выполнения операций, в него введены два кольцевых микрополосковых делителя мощности, распшритель, состоящий из N узлов и

0 кольцевого микрополоскового сумматора мощности, дополнительный узел с второй выходной шиной, состоящий из фазосдвигающего элемента, конденсатора и транзистора, база которого

5 соединена с общей шиной, коллектор через конденсатор соединен с другой тиной опорного сигнала и второй выходной шиной, а эмиттер через фа- зосдвигающий элемент соединен с од512

ним выходом делителя мощности, второй выход которого соединен с фазо- сдвигающим элементом основного узла, а вход делителя мощности соединен с выходом кольцевого сумматора мощное- ти расширителя, входы которого соединены с выходом каждого из N узлов, каждый из которых состоит из входной шины, шины опорного сигнала, вентиля, фазосдвигающего элемента, конденсатора и транзистора, база которого соединена с общей шиной, эмиттер через фазосдвигающий элемент соединен с входной шиной, а коллектор соединен через конденсатор с ши

16

ной опорного сигнала или с шиной опорного сигнала и через конденсатор с общей шиной, а шина оперного сигнала соединена с входом вентиля, выход которого является выходом узла, выходы второго кольцевого делителя мощности соединены с шинами опорного сигнала узлов расширителя и основного . и дополнительного узлов , а выход соединен с общей шиной спорного сигнала , кЬллекторы и эмиттеры всех транзисторов соединены соответственно с первой и второй выходными клеммами блока питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1986 |

|

SU1401597A1 |

| Логический элемент | 1986 |

|

SU1401596A1 |

| Радиочастотный логический элемент | 1984 |

|

SU1251320A1 |

| Радиочастотный логический элемент | 1984 |

|

SU1211874A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛА ВКЛЮЧЕНИЯ ПОМЕХ | 1993 |

|

RU2122281C1 |

| СВЧ-МОДУЛЬ СВЕРХРЕГЕНЕРАТИВНОГО ПРИЕМОПЕРЕДАТЧИКА РАДИОЗОНДА | 2007 |

|

RU2345379C1 |

| Радиочастотный логический элемент | 1986 |

|

SU1417185A1 |

| МИКРОПОЛОСКОВЫЙ МОЩНЫЙ БАЛАНСНЫЙ УСИЛИТЕЛЬ СВЧ | 1988 |

|

SU1840157A1 |

| Усилитель мощности | 2023 |

|

RU2796545C1 |

| ВЫСОКОРАЗРЯДНЫЙ ФАЗОВРАЩАТЕЛЬ СВЧ | 2018 |

|

RU2692480C1 |

Изобретение относится к импульсной технике и может быть использовано в радиоимпульсных вычислительных устройствах с амплитудным представлением информации работающих в сверхвысокочастотном диапазоне. Цель изобретения - рас пирение функциональных возможностей за счет увеличения коэффициента объединения по входу и количества одновременно выполняемых логических операций. Поставленная цель достигается введением в устройство двух кольцевых микрополосковых делителей мощности, расширителя, состоящего из N узлов и кольцевого микрополоскового сумматора мощности, дополнительного узла с второй выходной шиной, состоящего из фазосдви- гающего элемента, конденсатора и транзистора. Кроме того, устройство содержит шины опорного сигнала, блок питания, четвертьволновые линии передач и основной узел. 6 ил. с сл

5- i

211 29

Фиг. 2

JJ

Jff3O 2 о

фиг.З

Редактор М.Сегляник

Составитель 0.Скворцов Техред Н.Глущенко

Заказ 7458/57Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. З роектная, 4

Фи.б

Фмг.5

Корректор В.Бутяга

| Радиочастотный логический элемент | 1980 |

|

SU963132A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Радиочастотный логический элемент | 1984 |

|

SU1211874A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-15—Публикация

1985-07-19—Подача