112

Изобретение относится к электроизмерительной технике и может быть использовано дху измерения коэффициента гармоник усилителей мощности, в частности, в интегральном исполнении.

Цель изобретения - повьшение точности и достоверности измерения коэффициента тармоник за счет учета влияния напряжения шумов фона сети, более полной компенсации составляющей первой гармоники в резулъ - тирующем напряжении и исключения ложного забракования интегральных микросхем из-за саморазогрева корпуса при нарушении контакта корпуса с теплоотводом.

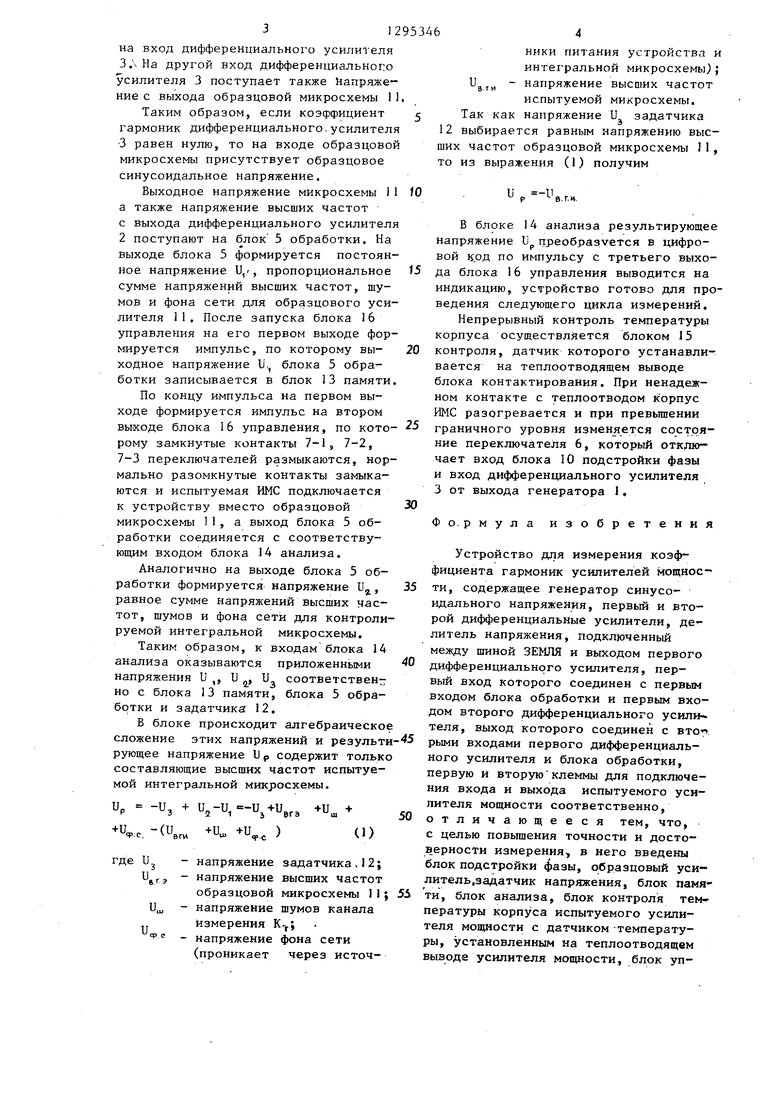

На чертеже представлена структурная схема устройства.

Устройство содержит генератор. 1 синусоидального напряжения, второй 2 и первый 3 дифференциальные усилители, резистивный делитель 4, блок 5 обработки, переключатель 6, блок 7 переключателей с контактами 7-1 - 7-3, клеммы 8 и 9 для подключения испытуемого усилителя мощности , которым явля.ется интегральная микросхема блок 10 подстройки фазы, образ-

цовый усилитель i1, задатчик 12 нап- ряжения, блок 13 памяти, блок 14 анализа, блок 15 контроля температуры корпуса интегральной микросхемы, блок 16 управления.

Выход генератора 1 через переключатель 6 соединен с первым входом блока 10 подстройки фазы и третьим входом дифференциального усилителя 3, первый вход которого соединен с первым входом дифференциального уси лителя 2, первым входом блока 5 обработки и вторым входом блока 10 подстройки фазы, выход дифференци- ального усилителя 2 подключен к второму входу блока 5 обработки, второму входу дифференциального усилителя 3, выход блока 10 подстройки фазы соединен с вторым входом дифференциального усилителя 2. Выход дифференциального усилителя 3 подключен к одному выводу делителя 4, второй вывод которого соединен с шиной ЗЕМЛЯ, а выход через блок 7 переключателей (контакты 7-1) - с входом образцового усилителя 11-. Выход блока 5 обработки через блок переключателей (контакты 7-3) соединен с входом блока 13 памяти и первым входом

о

.

5

0

5

5

0

5

0

55

блока 14 анализа, второй и третий входы блока 14 соединены соответственно с выходами блока 13 памяти и задатчиком 2 напряжения. Блок 15 контроля температуры соединен с уп- равляющим входом переключателя 6, а первый, второй и третий выходы блока 16 управления соединены с управляющими входами блока 3 памяти, блока 7 переключателей и блока 14 анализа.

К клеммам 8 и 9 подключается испытуемая микросхема. Клеммы 8 и 9 являются контактами блока контактирования (не показан)

Устройство работает, в два этапа.

На первом этапе определяют и запоминают в блоке 3 памяти напряжение, равное сумме напряжений.высших частот (гармоник) образцовой микросхемы, шумов и фона сети, на втором этапе - коэффициент гармоник испы г- туемой микросхемы.

К клеммам 8 и 9 подключают испытуемую интегральную микросхему, подают питающие напряжения на устройство и интегральную микросхему, на выходе задатчика 12 устанавливают напряжение, пропорциональное К об-п. разцовой микросхемы 11, и запускают блок 16 управления.

На выходе генератора 1 появляется синусоидальное напряжение, которое через нормально-: замкнутые контакты переключателя поступает на первые входы первого дифференциального усилителя 3 и блока 10 подстройки фазы. С выхода дифференциального усилителя 3 через делитель 4 и нормально замкнутые контакты 7-1 переключа.теля - напряжение подается на вход образцовой микросхемы 11. С выхода микросхемы 1I через нормально замкнутые контакты 7-2 переключателя напряжение поступает на первые входы первого и второго дифференциальных усилителей -2 и 3 и блока 5 обработки. В результате к прямому и обратному входам дифференциального усилителя 2 прикладываются с выходной образцовой микро- схемь П и блока 10 подстройки фазы напряжения, амплитуды первых гармоник которых равны, а фазы совпадают.

Составляюпдае высших частот, вьще- ленные при вычитании сигналов дифференциальным усилителем 2 поступают на входы блока 5 обработки и

312

на вход дифференциального усилителя 3.На другой вход дифференциального усилителя 3 постуцает также Напряжение с выхода образцовой микросхемы 11

Таким образом, если коэффициент гармоник дифференциального.усилителя 3 равен нулю, то на входе образцовой микросхемы присутствует образцовое синусоидальное напряжение.

Выходное напряжение микросхемы 11 а также напряжение высших частот с выхода дифференциального усилителя 2 поступают на блок 5 обработки. На выходе блока 5 формируется постоянное напряжение U,, пропорциональное сумме напряжений высших частот, шумов и фона сети для образцового усилителя 11. После запуска блока 16 управления на его первом выходе формируется импульс, по которому вы- ходное напряжение U, блока 5 обработки записывается в блок 13 памяти.

По концу импульса на первом выходе формируется импульс на втором

выходе блока 16 управления, по кото- рому замкнутые контакты 7-1, 7-2, 7-3 переключателей размыкаются, нормально разомкнутые контакты замыкаются и испытуемая ИМС подключается к устройству вместо образцовой

микросхемы 1I, а выход блока 5 обработки соединяется с соответствующим входом блока 14 анализа.

Аналогично на выходе блока 5 обработки формируется напряжение U, равное сумме напряжений высших частот, шумов и фона сети для контролируемой интегральной микросхемы.

Таким образом, к входам блока 14 анализа оказываются приложенными напряжения U ,, V , U соответственно с блока 13 памяти, блока 5 обработки и задатчика 12.

В блоке происходит алгебраическое сложение этих напряжений и результи рующее напряжение II р содержит только составляющие высших частот испытуемой интегральной микросхемы.

-и, -(и.

.,,, +и +

+иш ,.е )(О

де и.

и

г

напряжение задатчика,12; напряжение высших частот образцовой микросхемы 11; 5i напряжение шумов канала измерения К-,.; напряжение фона сети (проникает через источТак как

НИКИ питания устройства и интегральной микросхемы ; напряжение высших частот испытуемой микросхемы, напряжение U задатчика

12 выбирается равным напряжению высших частот образцовой микросхемы I1, то из выражения (1) получим

и

-и

в. г..

В блоке 14 анализа результирующее напряжение U преобразуется в цифровой код по импульсу с третьего выхода блока 16 управления выводится на индикацию, устройство готово для проведения следующего цикла измерений.

Непрерывный контроль температуры корпуса осуществляется блоком 15 контроля, датчик которого устанавливается на теплоотводящем выводе блока контактирования. При ненадежном контакте с теплоотводом к орпус ИМС разогревается и при превьшгенни граничного уровня изменяется состояние переключателя 6, который отключает вход блока 10 подстройки фазы и вход дифференциального усилителя 3 от выхода генератора 1.

-5

30

5

0

i

Фо.рмула изобретения

Устройство для измерения коэффициента гармоник усилителей мощности, содержащее генератор синусоидального напряжения, первый и второй дифференциальные усилители, дв литель напряжения, подключенный между шиной ЗЕМЛЯ и выходом первого дифференциального усилителя, первый вход которого соединен с первым входом блока обработки и первым входом второго дифференциального усили теля, выход которого соединен с втоп рыми входами первого дифференциального усилителя и блока обработки, первую и вторую клеммы для подключения входа и выхода испытуемого усилителя мощности соответственно, отличающееся тем, что, с целью повышения точности и досто верности измерения, в него введены блок подстройки фазы, образцовый уси- литель.задатчик иапряжения, блок памя ти, блок анализа, блок контроля температуры корпуса испытуемого усилителя мощности с датчиком -температуры, установленным на теплоотводящем выводе усилителя мощности, блок уп512

равления, переключатель, блок переключателей, при этом выход генератора синусоидального напряжения через нормально замкнутые замыкающий и переключающий контакты переключателя размыкающий контакт, управляющий вход которого соединен соответственно с шиной ЗЕМЛЯ с выходом блока контроля температуры, подключен к третьему входу первого дифференциаль- него усилителя и к первому входу блока подстройки фазы, второй вход которого соединен с первым входом блока обработки, а выход подключен к второму входу второго дифференци- ального усилителя, выход делителя через последовательно включенные первую группу нормально зам кнутых контактов блока переключателей, образцовый усилитель, вторую группу нормально замкнутых контактов бло66

ка переключателей подключен к первому входу первого дифференциальног о усилителя, а первая и вторая группы нормально разомкнутых контактов блока переключателей соединены соответственно с первой и второй клеммами для подключения испытуемого усилителя, выход блока обработки через третью группу нормально разомкнутых и нормально замкнутых контактов блока переключателей подключен соответственно к первому входу блока анализа и входу блока памяти, выход которого соединен с вторым входом блока анализа, к третьему входу которого подключен задатчик напряжения, при этом первый второй и третий выходы блока управления подключ« Ны .соответственно к. управляющим входам блоков памяти, переключателей и анализа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения коэффициента гармоник усилителей мощности | 1978 |

|

SU879493A2 |

| Устройство для измерения коэффициента гармоник усилителей мощности | 1978 |

|

SU746320A1 |

| Устройство для измерения коэффициента гармоник | 1976 |

|

SU789851A1 |

| Универсальный калибратор тока | 1985 |

|

SU1308969A1 |

| Калибратор периодических сигналов | 1989 |

|

SU1709262A1 |

| Устройство для контроля усилителей низкой частоты | 1988 |

|

SU1594460A1 |

| Устройство для измерения электрических параметров четырехполюсника | 1978 |

|

SU767655A1 |

| Устройство для контроля регуляторагРОМКОСТи и СТЕРЕОбАлАНСА | 1979 |

|

SU853572A1 |

| Устройство для контроля качества кабелей и жгутов | 1986 |

|

SU1318943A1 |

| Преобразователь комплексных сопротивлений и проводимостей в напряжение | 1991 |

|

SU1827646A1 |

Изобретение может быть использовано для измерения коэффициента гармоник усилителей мощности, в частности, в интегральном исполнении. .Цель изобретения - повышение точности и достоверности измерения достигается за счет учета влияния напряжения шумов, фона сети, более полной компенсации составляющей первой гармоники в результирующем напряжении и исключения ложного эабра- кования интегральных схем (ИС) при нарущении контакта корпуса с тепло- отводом. Устройство содержит генератор 1 синусоидального напряжения, дифференциальные усилители 2 и 3, резистивный делитель 4, блок 5 обработки, переключатель 6, блок 7 переключателей с контактами 71-7-3 клеммы 8 и 9, блок 10 подстройки фазы, образцовый усилитель 1I, задат- чик 12 напряжения, блоки памяти 13, управления 14, контроля 15 температуры корпуса ИС, управления 16. 1 ил. (Л

| Устройство для измерения коэффициента гармоник усилителей мощности | 1978 |

|

SU746320A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения коэффициента гармоник усилителей мощности | 1978 |

|

SU879493A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-03-07—Публикация

1985-10-28—Подача