Ц

S

4/ 7Up-M т ®±в

Изобретение относится к радиотехнике и предназначено для выделения абсолютной величины видеосигнала в трактах с большим динамическим диапазоном, а Также может быть использовано в широкополосных измерительных преобразователях средневыпрямлен- ных значений с большим динамическим диапазоном.

Цель изобретения - увеличение точности и чувствительности детектора.

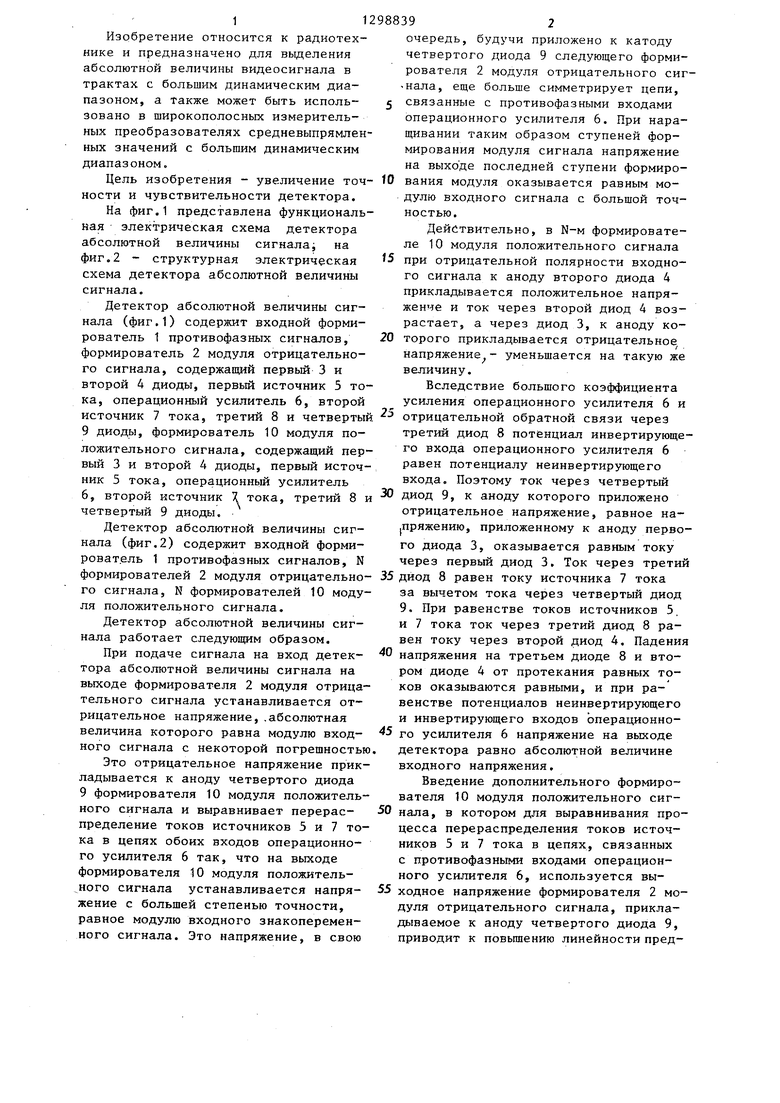

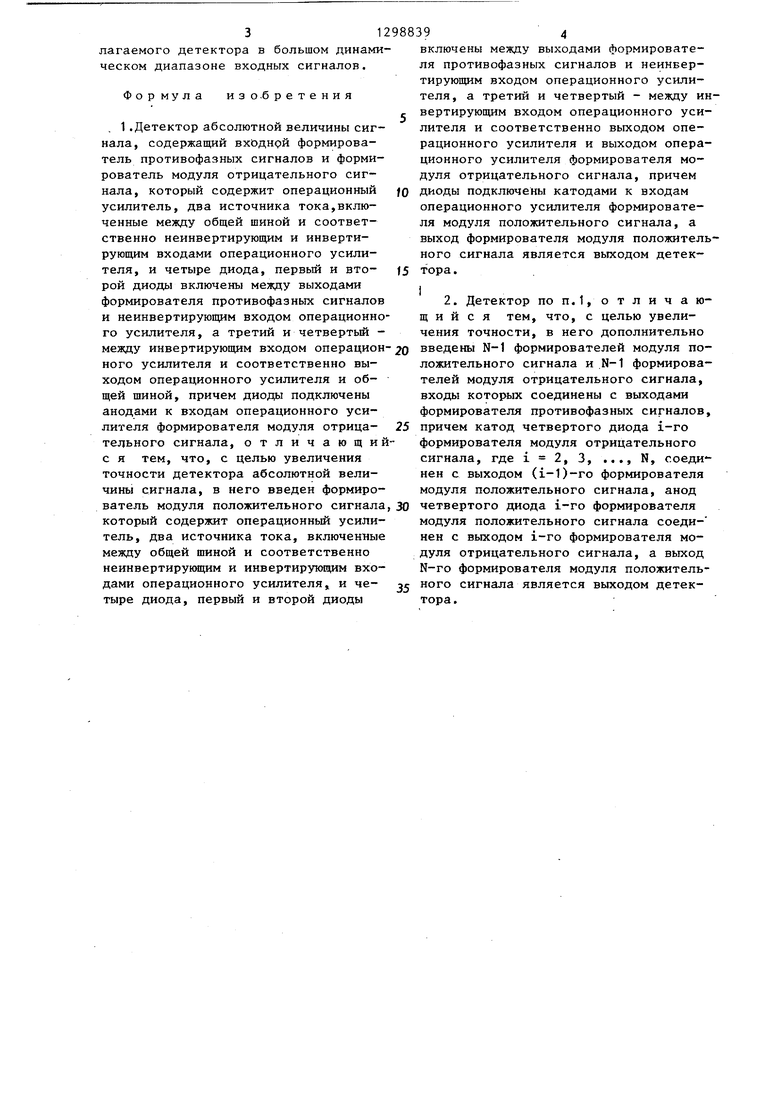

На фиг.1 представлена функциональная электрическая схема детектора абсолютной величины сигнала; на фиг.2 - структурная электрическая схема детектора абсолютной величины сигнала.

Детектор абсолютной величины сигнала (фиг,1) содержит входной формирователь 1 противофазных сигналов, формирователь 2 модуля отрицательного сигнала, содержащий первый 3 и второй 4 диоды, первый источник 5 тока, операционный усилитель 6, второй

очередь, будучи приложено к катоду четвертого диода 9 следующего форми рователя 2 модуля отрицательного си -нала, еще больше симметрирует цепи,

5 связанные с противофазными входами операционного усилителя 6. При нара щивании таким образом ступеней формирования модуля сигнала напряжение на выходе последней ступени формиро

tO вания модуля оказывается равным модулю входного сигнала с большой точ ностью.

Действительно, в N-M формировате ле 10 модуля положительного сигнала при отрицательной полярности входно го сигнала к аноду второго диода 4 прикладывается положительное напряжение и ток через второй диод 4 воз растает, а через диод 3, к аноду ко

20 торого прикладывается отрицательное напряжение - уменьшается на такую ж величину.

Вследствие большого коэффициента усиления операционного усилителя 6

f5

- -- ---f

ИСТОЧНИК 7 тока, третий 8 и четвертый отрицательной обратной связи через

9 диоды, формирователь 10 модуля положительного сигнала, содержащий первый 3 и второй 4 диоды, первый источник 5 тока, операционньрЩ усилитель

третий диод 8 потенциал инвертирующего входа операционного усилителя 6 равен потенциалу неинвертирующего входа. Поэтому ток через четвертый

6, второй источник тока, третий 8 и ДиоД 9. к аноду которого приложено четвертый 9 диоды.отрицательное напряжение, равное на.пряжению, приложенному к аноду первого диода 3, оказывается равным току

9 диоды

Детектор абсолютной величины сигнала (фиг.2) содержит входной формирователь 1 противофазных сигналов, N

40

формирователей 2 модуля отрицательно- 35 диод 8 равен току источника 7 тока го сигнала, N формирователей 10 модуля положительного сигнала.

Детектор абсолютной величины сигнала работает следующим образом.

При подаче сигнала на вход детектора абсолютной величины сигнала на выходе формирователя 2 модуля отрицательного сигнала устанавливается отрицательное напряжение,.абсолютная величина которого равна модулю входного сигнала с некоторой погрешностью.

Это отрицательное напряжение прикладывается к аноду четвертого диода 9 формирователя 10 модуля положительного сигнала и выравнивает перераспределение токов источников 5 и 7 тока в цепях обоих входов операционного усилителя 6 так, что на выходе формирователя 10 модуля положитель- ного сигнала устанавливается напряжение с большей степенью точности, равное модулю входного знакопеременного сигнала. Это напряжение, в свою

за вычетом тока через четвертый дио 9. При равенстве токов источников 5 и 7 тока ток через третий диод 8 ра вен току через второй диод 4, Паден напряжения на третьем диоде 8 и вто ром диоде 4 от протекания равных то ков оказываются равными, и при равенстве потенциалов неинвертирующег и инвертирующего входов операционно

45 го усилителя 6 напряжение на выходе детектора равно абсолютной величине входного напряжения.

Введение дополнительного формиро вателя 10 модуля положительного сиг

50 нала, в котором для выравнивания пр цесса перераспределения токов источ ников 5 и 7 тока в цепях, связанных с противофазными входами операционного усилителя 6, используется вы55 ходное напряжение формирователя 2 м дуля отрицательного сигнала, прикла дываемое к аноду четвертого диода 9 приводит к повышению линейности пре

очередь, будучи приложено к катоду четвертого диода 9 следующего формирователя 2 модуля отрицательного сиг- нала, еще больше симметрирует цепи,

связанные с противофазными входами операционного усилителя 6. При наращивании таким образом ступеней формирования модуля сигнала напряжение на выходе последней ступени формирования модуля оказывается равным модулю входного сигнала с большой точностью.

Действительно, в N-M формирователе 10 модуля положительного сигнала при отрицательной полярности входного сигнала к аноду второго диода 4 прикладывается положительное напряжение и ток через второй диод 4 возрастает, а через диод 3, к аноду которого прикладывается отрицательное напряжение - уменьшается на такую же величину.

Вследствие большого коэффициента усиления операционного усилителя 6 и

третий диод 8 потенциал инвертирующего входа операционного усилителя 6 равен потенциалу неинвертирующего входа. Поэтому ток через четвертый

через первый диод 3. Ток через третий

40

35 диод 8 равен току источника 7 тока

за вычетом тока через четвертый диод 9. При равенстве токов источников 5. и 7 тока ток через третий диод 8 равен току через второй диод 4, Падени напряжения на третьем диоде 8 и втором диоде 4 от протекания равных токов оказываются равными, и при равенстве потенциалов неинвертирующего и инвертирующего входов операционно45 го усилителя 6 напряжение на выходе детектора равно абсолютной величине входного напряжения.

Введение дополнительного формирователя 10 модуля положительного сиг50 нала, в котором для выравнивания процесса перераспределения токов источников 5 и 7 тока в цепях, связанных с противофазными входами операционного усилителя 6, используется вы55 ходное напряжение формирователя 2 модуля отрицательного сигнала, прикладываемое к аноду четвертого диода 9, приводит к повышению линейности предлатаемого детектора в большом динамическом диапазоне входных сигналов.

Формула изо.б ратания

1 .Детектор абсолютной величины сигнала, содержащий вхЬднрй формирователь противофазных сигналов и формирователь модуля отрицательного сигнала, который содержит операционный усилитель, два источника тока,включенные между общей шиной и соответственно неинвартирующим и инвертирующим входами операционного усилителя, и четыре диода, первый и вто- рой диоды включены между выходами формирователя противофазных сигналов и неинвертирующим входом операционного усилителя, а третий и четвертый между инвертирующим входом операцион-20 введены N-1 формирователей модуля положительного сигнала и .N-1 формирователей модуля отрицательного сигнала, входы которых соединены с выходами формирователя противофазных сигналов, 25 причем катод четвертого диода i-ro формирователя модуля отрицательного сигнала, где i 2, 3, ..., N, соединен с выходом (i-l)-ro формирователя модуля положительного сигнала, анод

ного усилителя и соответственно выходом операционного усилителя и общей шиной, причем диоды подключены анодами к входам операционного усилителя формирователя модуля отрицательного сигнала, отличающий- с я тем, что, с целью увеличения точности детектора абсолютной величины сигнала, в него введен формирователь модуля положительного сигнала,30 четвертого диода i-ro формирователя

который содержит операционный усилитель, два источника тока, включенные между общей шиной и соответственно неинвертирукнцим и инвертирующим входами операционного усилителя,; и четыре диода, первый и второй диоды

включены между выходами формирователя противофазных сигналов и наинвер- тирующим входом операционного усилителя, а третий и четвертый - между инвертирующим входом операционного усилителя и соответственно выходом операционного усилителя и выходом операционного усилителя формирователя модуля отрицательного сигнала, причем диоды подключены катодами к входам операционного усилителя формирователя модуля положительного сигнала, а выход формирователя модуля положительного сигнала является выходом детектора.

2. Детектор по п.1,о тл ич аю- щ и и с я тем, что, с целью увеличения точности, в него дополнительно

модуля положительного сигнала соединен с выходом i-ro формирователя модуля отрицательного сигнала, а выход N-ro формирователя модуля положительного сигнала является выходом детектора.

Заказ 895/56 Тираж 902 Подписное ВЕШИЛИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Детектор абсолютной величины входного сигнала | 1985 |

|

SU1337991A1 |

| Детектор абсолютной величины сигнала | 1982 |

|

SU1157643A1 |

| Устройство для выделения модуля | 1981 |

|

SU1019460A1 |

| ДЕТЕКТОР АБСОЛЮТНОЙ ВЕЛИЧИНЫ СИГНАЛА | 2000 |

|

RU2210855C2 |

| Формирователь модуля сигнала | 1982 |

|

SU1116526A1 |

| Устройство для дифференциальной защиты трансформатора | 1981 |

|

SU1020909A1 |

| Двухполупериодный выпрямитель | 1983 |

|

SU1184067A1 |

| Детектор абсолютной величины сигнала | 1982 |

|

SU1046905A1 |

| Реле частоты | 1980 |

|

SU983804A1 |

| Преобразователь напряжения | 1977 |

|

SU690400A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение точности и увеличение чувствительности детектора. Устр-во содержит входной формирователь (Ф) 1 противофазных сигналов, Ф 2 модуля от рицат. сигнала, содержащий диоды 3, 4, 8 и 9, источники тока (ИТ) 5 и 7 и операционный у-ль (ОУ) 6. Вновь введен Ф 10 модуля положит.сигнала, содержащий четыре диода 3, 4, 8 и 9, два ИТ 5 и 7, ОУ 6. Введение Ф 10, в к-ром для выравнивания процесса перераспределения токов ИТ 5 и 7 в цепях, связанных с противофазными входами ОУ 6, используется выходное напряжение Ф 2, прикладываемое к аноду диода 9, приводит к повышению линейности в большом динамич. диапазоне входных сигналов. В устр-во также дополнительно введено (N-1) Ф модуля положит.сигнала и (N-1) Ф модуля от- рицат.сигнала. 1 з.п. ф-лы, 2 ил. а € (Л 3 -ИВы№д -ff йf 7. -1

| Детектор абсолютной величины сигнала | 1982 |

|

SU1046905A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Детектор абсолютной величины сигнала | 1982 |

|

SU1157643A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-23—Публикация

1985-06-11—Подача