1

Изобретение относнтся к электротехнике, и может быть использовано устройствах электропитания аптшрат ры связи, автоматики и вычислительной техники.

Цель изобретения - .повышение надежности работы стабилизированного источника иостоянног о напряжения.

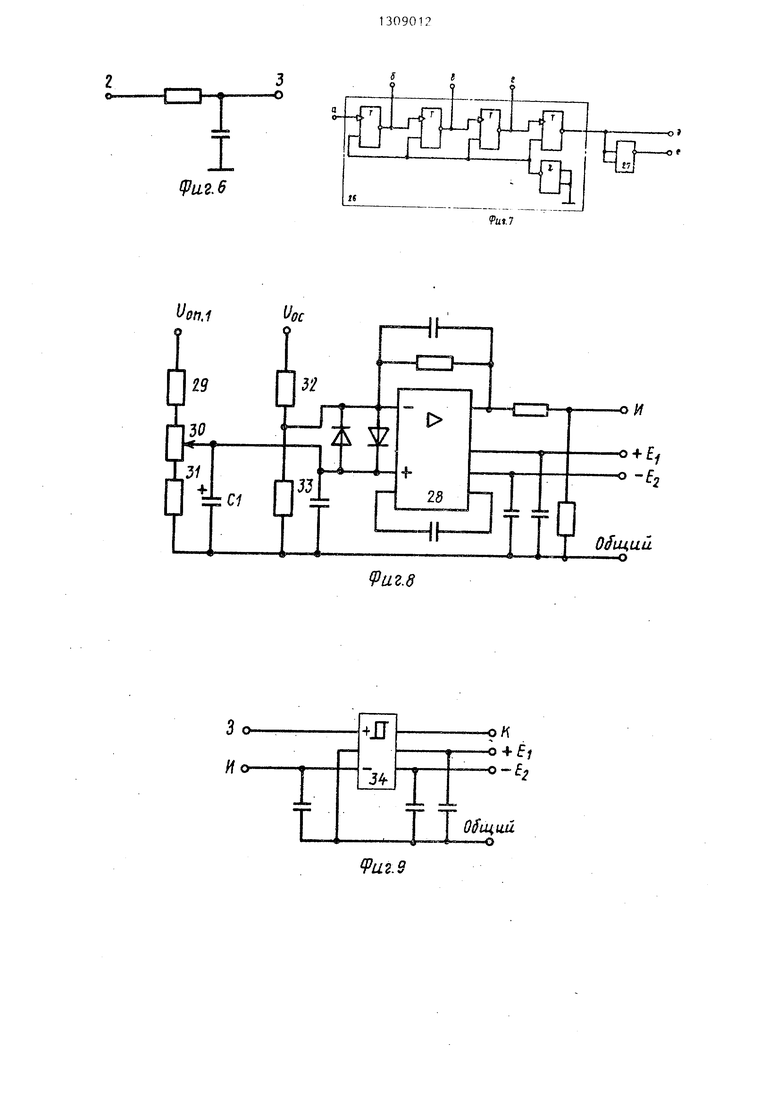

На фиг. 1 представлена фyнкцi o- нальная схема стабилизированного иточника постоянного напряжения; на фиг. 2-4 - эпюры напряжений в харатерных точках cxpMiii; на фиг, 5 - электрическая схема задающего гене paTopaj на фиг. 6 - схема генератора пилообразного напряжения; на фи

7- схема- делителя частоты; на фиг

8- схема цепи обратной связи; на фиг. 9 - схема компаратора,- на фиг 10 - схема селекторов; на фиг. 11 схема усилителя мопности; на фиг,12 схема выпрямителя; на фиг. 13 - сх

ма фильтра-, на фиг. 14 - схема нуль- органа; на фиг. 15 - схема К5 три1 ге ра; на фиг. 16 - схема блока установ ки триггера; на фиг, 17 - схема порогового блока; на фиг. 18 - схема датчика напряжения сети.

Устройство содержит задаю ций генератор 1, генератор 2 пилообразного н пряжения, делитель 3 частоты, цепь 4 обратной связи, компаратор 5, селекторы 6 и 7, усилитель 8 мощности, выпрямитель 9, фильтр 10, нагрузку 11, нуль-орган 12, RS-триггер 13,, блок 14 установки триггера, элемент ЗИ-НЕ 15, пороговый блок 16 логический элемент ИЛИ 17, датчик 18 напряжения сети.

Усилитель 8 мощности, выпрямитель 9 и фильтр 10 составляют силовую часть схемы, остальные функциональные элементы - управляющую часть.

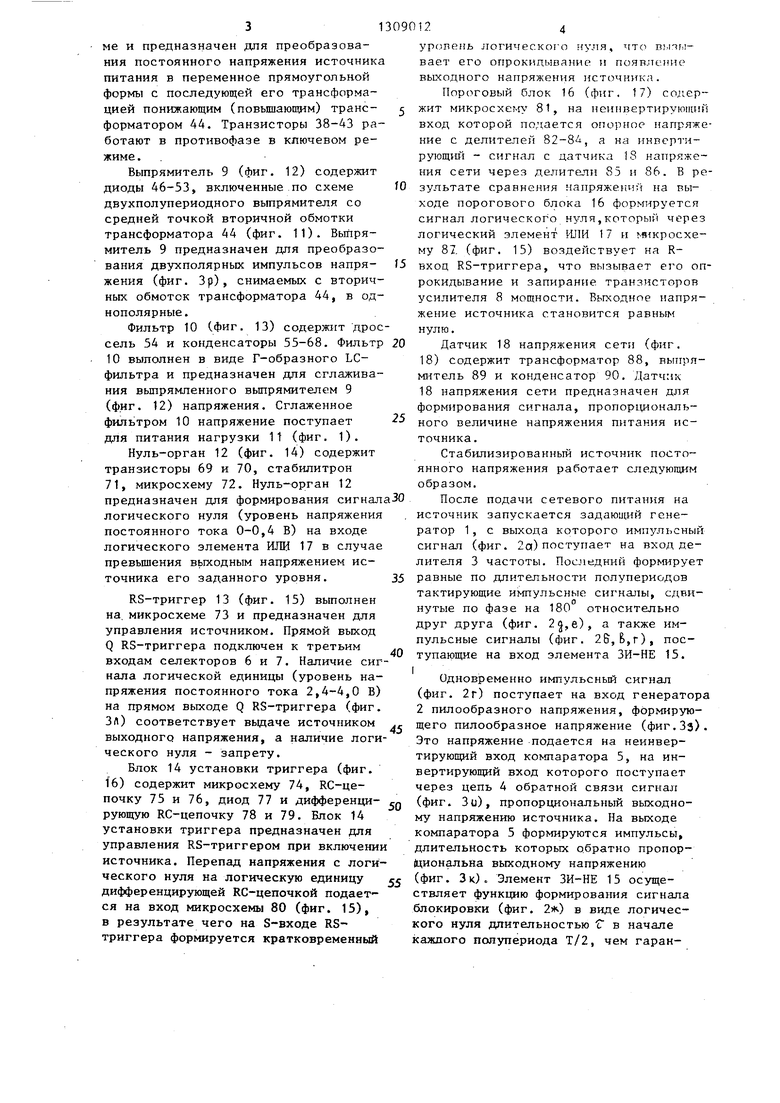

Задающий генератор 1 (фиг. 5) содержит микросхему 19, резисторы 20- 23, конденсаторы 24 и 25. Задающий генератор 1 предназначен для получения последовательности импульсов (фиг. 2а). При необходимости частоту згщающего генератора 1 можно изменять путем подбора величины емкостр конденсатора 24. Инвертор на логическом элементе и резисторе 23 уменьшает влияние делителя 3 частоты на параметры задающего генератора 1

Генератор 2 пилообразного напряжения (фиг. 6) выполнен в виде интегрирующей RC-цепочки, на вход которо

O

а также для форми- сдвинутых на 180 относитель5

0

0

-

микросхеме 34

подается последовательность импульсов (фиг. 2г), а с выхода снимается пилообразное напряжение (фиг. Зз.

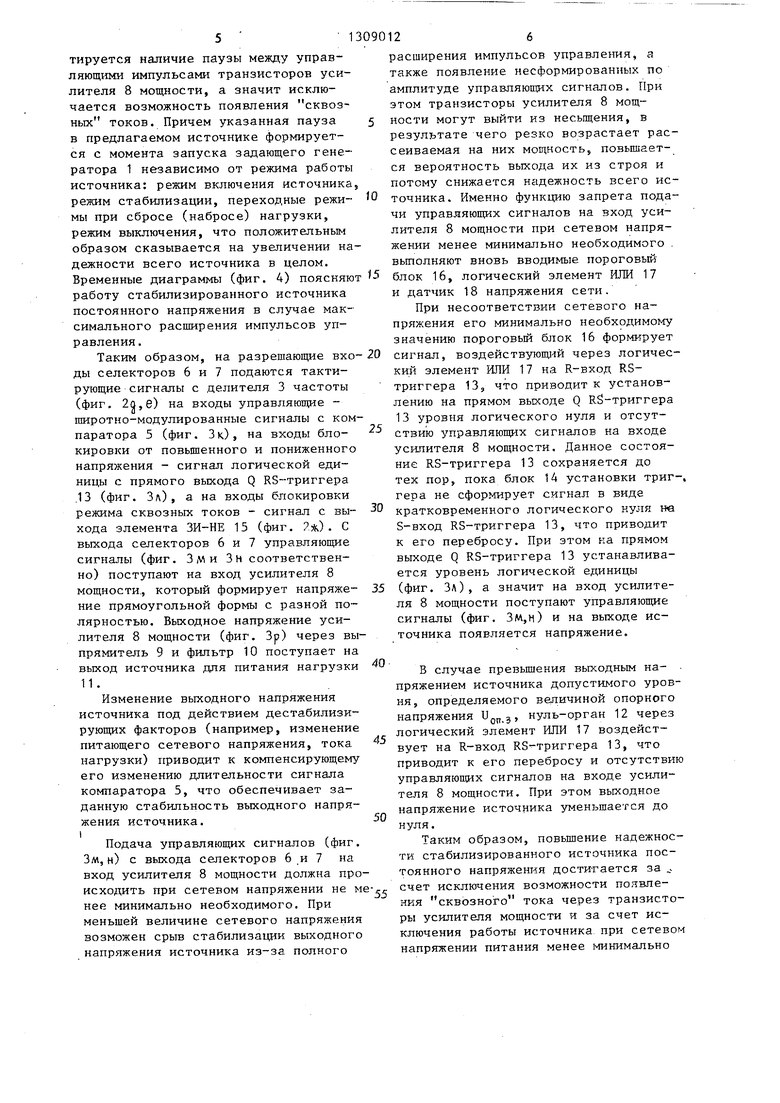

.Делитель 3 частоты (фиг. 7) содержит микросхемы 26 и 27. Делитель 3 частоты выполнен на основе двоичного счетчика и предназначен.для понижения частоты задающего генератора в 2, 4, В, 16 раз, рования

но друг друга тактируюкрх сигналов (фиг. 2а,е).

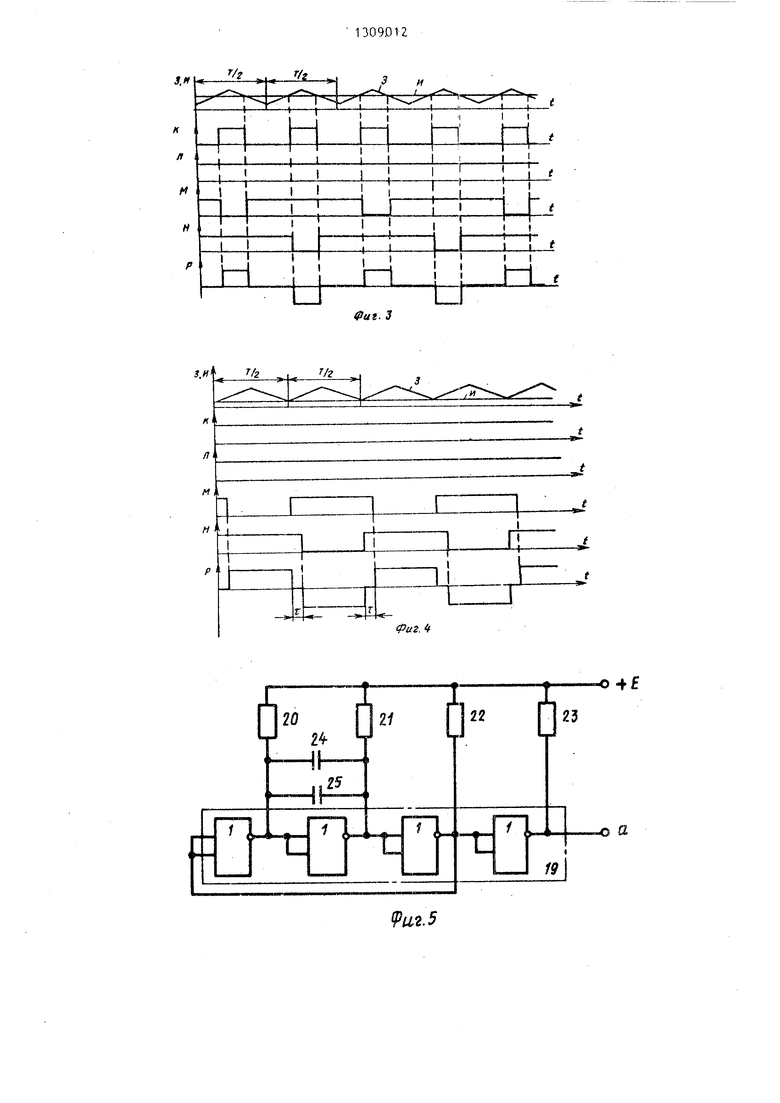

Цепь 4 обратной связи (фиг, 8) содержит операционный усилитель на микросхеме 28, на неи вертирующий вход которого подается опорное напряжение с делителей 29-31, а на инвертирующий - выходное напряжение источника с делителей 32 и 33.

В результате сравнения напряжений на выходе усилителя формируется сигнал рассогласования (фиг. 3(j) , пропорциональный изменению выходного напряжения источника. Для обеспечения плавного нарастания выходного напряжения источника при его включении часть делителя щунтирована конденсатором.

Компаратор 5 (фиг. 9) выполнен на

и предназначен для получения импульсов с изменяющейся длительностью (фиг. 3k).

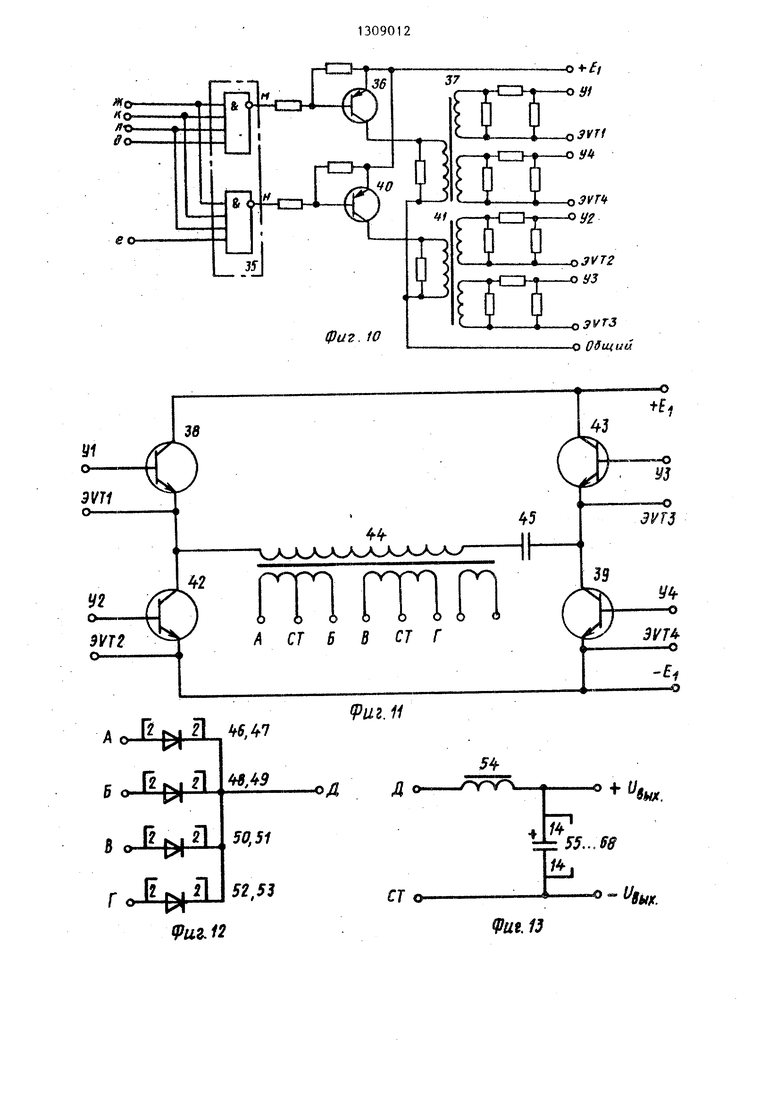

Селектор 6 (фиг. 10) содержит логический элемент 35, транзистор 36, 35 трансформатор 37. Логический элемент 35 предназначен для формирования импульсов управления (фиг. 3м), транзистор 36 - для их дальнейшего усиления, а трансформатор 37 - для гальванической развязки и трансформирования с целью получения управляющих сигналов транзисторами 38 и 39 усилителя 8 мощности (фиг. 11). Селектор

7содержит логический элемент 35,

5 транзистор 40, трансформатор 41 (фиг. 10). Логический элемент 35 предназначен для формирования импульсов управления (фиг. 3h), транзистор 40 - для их дальнейшего усиления,а трансформатор 41 - для гальванической развязки и трансформирования с целью по- пучения управляющих сигналов транзисторами 42 и 43 усилителя 8 мощности (фиг. 11).

Усилитель 8 мощности (фиг. 11) содержит транзисторы 38-43, трансформатор 44 и конденсатор 45, Усилитель

8мощности выполнен по мостовой схе50

55

3

ме и предназначен для преобразования постоянного напряжения источник питания в переменное прямоугольной формы с последующей его трансформацией понижающим (повышающим) трансформатором 44. Транзисторы 38-43 работают в противофазе в ключевом режиме .

Выпрямитель 9 (фиг. 12) содержит диоды 46-53, включенные по схеме двухполупериодного выпрямителя со средней точкой вторичной обмотки трансформатора 44 (фиг. 11). Выпрямитель 9 предназначен для преобразования двухполярных импульсов напряжения (фиг. Зр), снимаемьЕх с вторичных обмоток трансформатора 44, в од нополярные.

Фильтр 10 (фиг. 13) содержит дросель 54 и конденсаторы 55-68. Фильт 10 выполнен в виде Г-образного LC- фильтра и предназначен для сглаживания выпрямленного выпрямителем 9 (фиг. 12) напряжения. Сглаженное фильтром 10 напряжение поступает для питания нагрузки It (фиг. 1).

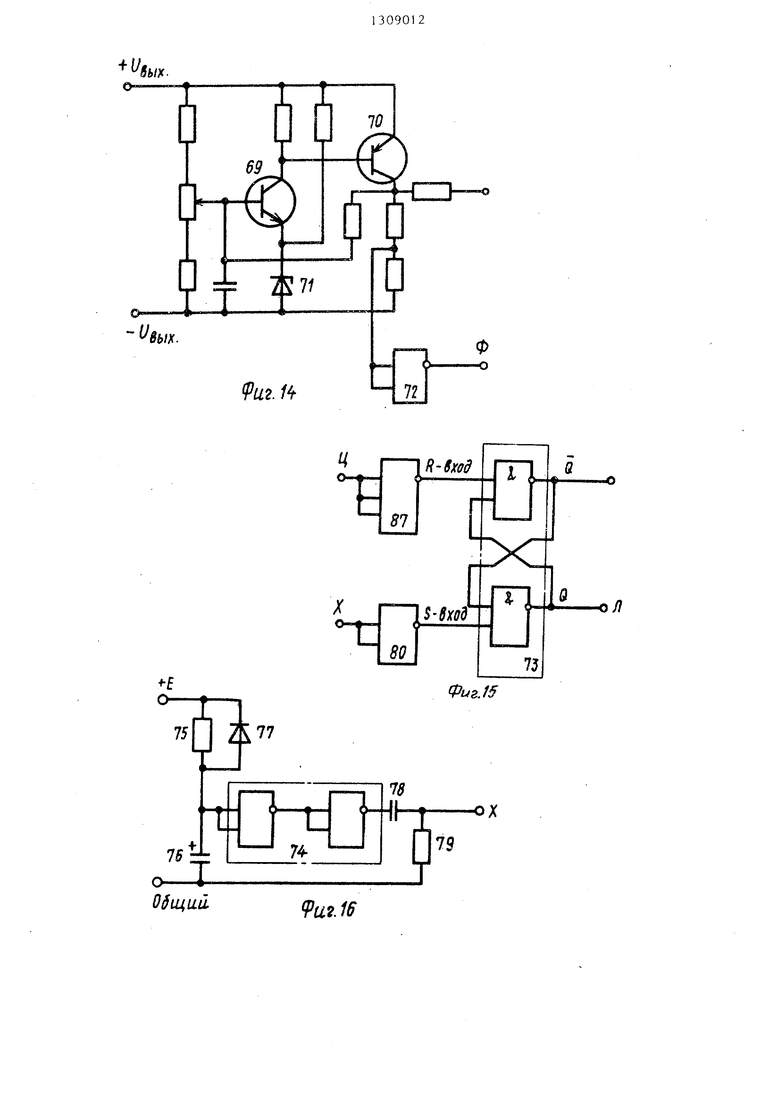

Нуль-орган 12 (фиг. 14) содержит транзисторы 69 и 70, стабилитрон 71, микросхему 72. Нуль-орган 12 предназначен для формирования сигна логического нуля (уровень напряжени постоянного тока 0-0,4 В) на входе логического элемента ИЛИ 17 в случа превышения вьгходным напряжением источника его заданного уровня.

RS-триггер 13 (фиг. 15) выполнен на. микросхеме 73 и предназначен для управления источником. Прямой выход Q RS-триггера подключен к третьим входам селекторов 6 и 7. Наличие синала логической единицы (уровень напряжения постоянного тока 2,4-4,0 В на прямом выходе Q RS-триггера (фиг Зл) соответствует выдаче источником выходного напряжения, а наличие логческого нуля - запрету.

Блок 14 установки триггера (фиг. 16) содержит микросхему 74, RC-це- почку 75 и 76, диод 77 и дифференцирующую RC-цепочку 78 и 79. Блок 14 установки триггера предназначен для управления RS-триггером при включени источника. Перепад напряжения с логического нуля на логическую единицу дифференцирующей КС-цепочкой подается на вход микросхемы 80 (фиг. 15), в результате чего на S-входе RS- триггера формируется кратковременный

fO

J5

25

20

ЗО

г

уровень логическо1-о нуля, Tci D.i-if,i- вает его опрокидывание и появление выходного напряжения источника.

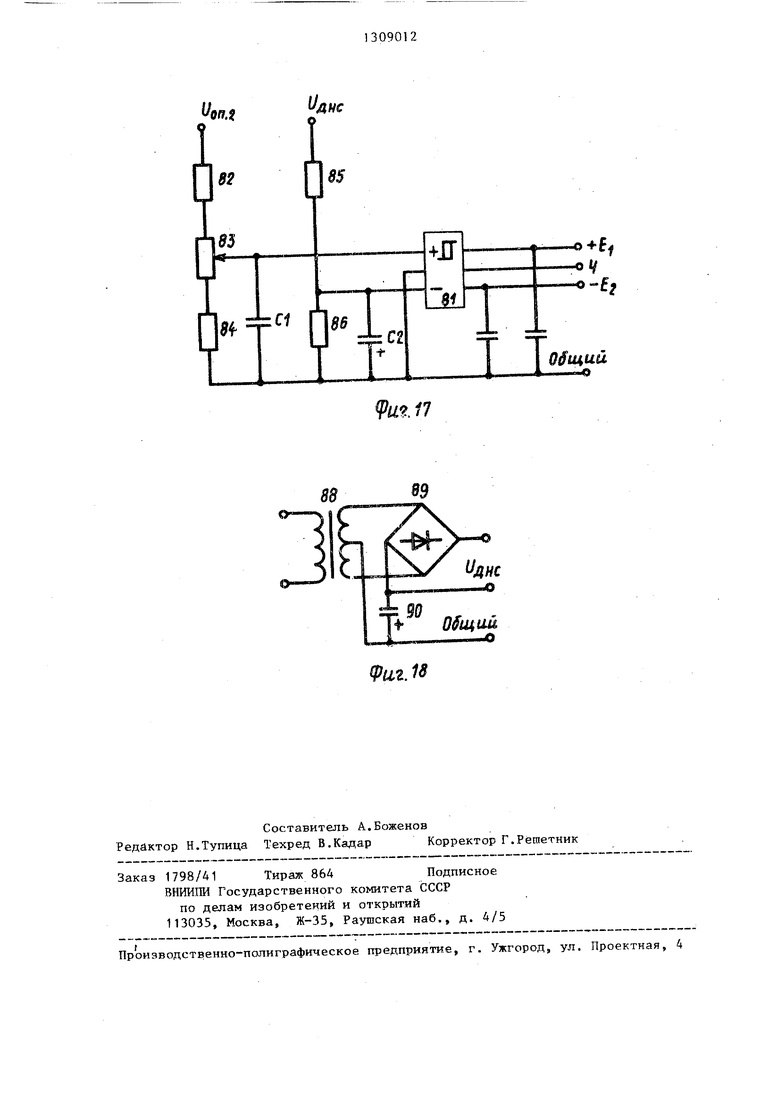

Пороговый блок 16 (фиг. 17) содержит микросхему 81, на неимвертирующий вход которой подается опорное напряжение с делителей , а на инвертирующий - сигнал с датчика 18 напряжения сети через делители 85 и 86. В результате сравнения иапряже}1ий на выходе порогового блока 16 формируется сигнал логического нуля,который через логический элемент Ш1И 17 и j-sfKpocxe- му 87. (фиг, 15) воздействует на R- вход RS-триггера, что вызывает его опрокидывание и запирание транзисторов усилителя 8 мощности. Выходное напряжение источника становится равнь(м нулю.

Датчик 18 напряжения сети (фиг. 18) содержит трансформатор 88, выпрямитель 89 и конденсатор 90. /Датчик 18 напряжения сети предназначен для формирования сигнала, пропорционального величине напряжения питания источника.

Стабилизированный источник постоянного напряжения работает следующим образом.

После подачи сетевого питания на источник запускается задающий генератор 1, с выхода которого импульсный сигнал (фиг. 2а)поступает на вход делителя 3 частоты. Последний формирует равные по длительности полупериодов тактирующие импульсные сигналы, сдвинутые по фазе на 180 относительно друг друга (фиг. 2,е), а также импульсные сигналы (фиг. 2&,6,г), пос- 40 тупающие на вход элемента ЗИ-НЕ 15. I

35

5

0

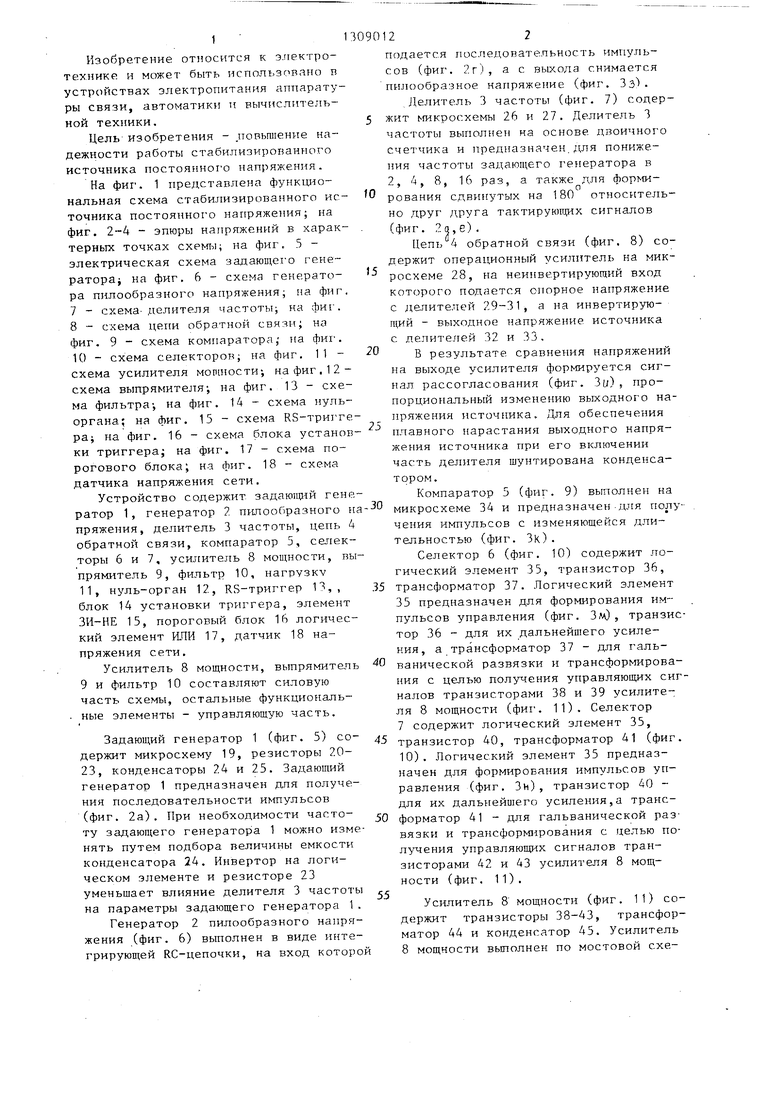

Одновременно импульсный сигнал (фиг. 2г) поступает на вход генератора 2 пилообразного напряжения, формирующего пилообразное напряжение (фиг.Зз). Это напряжение подается на неинвертирующий вход компаратора 5, на инвертирующий вход которого поступает через цепь 4 обратной связи сигнал (фиг. Зи), пропорциональный выходному напряжению источника. На вьгходе компаратора 5 формируются импульсы, длительность которых обратно пропор- (циональна выходному напряжению (фиг. Зк). Элемент ЗИ-НЕ 15 осуществляет функцию формирования сигнала блокировки (фиг. 2) в виде логического нуля длительностью Г в начале каждого полупериода Т/2, чем гаран

тируется наличие паузы между управляющими импульсами транзисторов усилителя 8 мощности, а значит исключается возможность появления сквозных токов. Причем указанная пауза в предлагаемом источнике формируется с момента запуска задающего генератора 1 независимо от режима работы источника: режим включения источника, режим стабилизации, переходные режимы при сбросе (набросе) нагрузки, режим выключения, что положительным образом сказывается на увеличении надежности всего источника в целом. Временные диаграммы (фиг. 4) поясняют работу стабилизированного источника постоянного напряжения в случае максимального расширения импульсов управления.

Таким образом, на разрешающие входы селекторов 6 и 7 подаются тактирующие сигналы с делителя 3 частоты (фиг. 2д,е) на входы управляюкцие - широтно-модулированные сигналы с ком

паратора 5 (фиг. Зк), на входы блокировки от повышенного и пониженного напряжения - сигнал логической единицы с прямого выхода Q RS-триггера .13 (фиг. 3л), а на входы блокировки режима сквозных токов - сигнал с выхода элемента ЗИ-НЕ 15 (фиг. ) . С выхода селекторов 6 и 7 управляюш;ие сигналы (фиг. 3м и Зн соответственно) поступают на вход усилителя 8 мощности,, который формирует напряжение прямоугольной формы с разной полярностью. Выходное напряжение усилителя 8 мощности (фиг. Зр) через выпрямитель 9 и фильтр 10 поступает на выход источника дня питания нагрузки 11.

Изменение выходного напряжения источника под действием дестабилизирующих факторов (например, изменение питающего сетевого напряжения, тока нагрузки) приводит к компенсирующему его изменению длительности сигнала компаратора 5, что обеспечивает заданную стабильность выходного напряжения источника. 1

Подача управляющих сигналов (фиг.

3м,н) с выхода селекторов 6 и 7 на вход усилителя 8 мощности должна происходить при сетевом напряжении не мнее минимально необходимого. При меньшей величине сетевого напряжения возможен срыв стабилизации выходного напряжения источника из-за полного

5

0

.5

0

5

0

расширения импульсов управления, а также появление несформированных по амплитуде управляюш х сигналов. При этом транзисторы усилителя 8 мощности могут выйти из несьш1ения, в результате чего резко возрастает рассеиваемая на них мощность, повьпвает- ся вероятность выхода их из строя и потому снижается надежность всего источника. Именно функцию запрета подачи управляющих сигналов на вход усилителя 8 мощности при сетевом напряжении менее минимально необходимого . вьшолняют вновь вводимые пороговый блок 16, логический элемент ИЛИ 17 и датчик 18 напряжения сети.

При несоответствии сетевого напряжения его минимально необходимому значению пороговый блок 16 формирует сигнал, вoздeйcтвyюш й через логический элемент ИЛИ 17 на R-вход RS- триггера 13, что приводит к установлению на прямом выходе Q RS-триггера 13 уровня логического нуля и отсутствию управляющих сигналов на входе усилителя 8 мощности. Данное состояние RS-триггера 13 сохраняется до тех пор, пока блок 14 установки триг-, гера не сформирует сигнал в виде кратковременного логического нуля не S-вход RS-триггера 13, что приводит к его перебросу. При этом на прямом выходе Q RS-триггера 13 устанавливается уровень логической единицы (фиг. Зл), а значит на вход усилителя 8 мощности поступают управляющие сигналы (фиг. Зм,ц) и на выходе источника появляется напряжение.

В случае превышения выходным на- пряжением источника допустимого уровня, определяемого величиной опорного

5

0

5

напряжения U

оп.э

нуль-орган 12 через

логический элемент ИЛИ 17 воздействует на R-вход RS-триггера 13, что приводит к его перебросу и отсутствию управляюших сигналов на входе усилителя 8 мощности. При этом выходное напряжение источника уменьшается до нуля.

Таким образом, повьщ1ение надежности стабилизированного источника постоянного напряжения достигается за , счет исключения возможности появления сквозного тока через транзисторы усилителя мощности и за счет исключения работы источника при сетевом напряжении питания менее IvIИHимaльнo

необходимого, что возможно, например при его включении.

Формула изобретени

1. Стабилизированный источник постоянного напряжения,содержащий задающий генератор,выход которого соединен с входом делителя частоты, первый и второй выходы которого подключены к разрешающим входам селекторов, управляющие входы которых подключены к выходу компаратора, а входы блокировки от пониженного и повышенного напряжения подключены к выходу RS- триггера, к первому входу компаратора подключен выход генератора пилообразного напряжения, выходы селекторов подключены через последовательно соединенные усилитель мощности, выпрямитель и фильтр к выводам для подключения; нагрузки, соединенным чрез цепь обратной связи с вторым входом компаратора, блок установки триггера, подключенный к S-входу RS-триггера, нуль-орган, один вход которого подключен к источнику опорного напряжения, а другой - к вывода для подключения нагрузки , отличающийся тем, что, с целью повьш1ения надежности работы источни

5

0 5

0

ка, в него введены логический элемент ЗИ-НЕ, пороговый блок, датчик напряжения сети и логический элемент ИЛИ, причем три входа элемента ЗИ-НЕ соединены соответственно с третьим, четвертым и пятым выходами делителя частоты, а выход элемента ЗИ-НЕ - с вхо- блокировки режима сквозных токов двух селекторов, вход генератора пилообразного напряжения подключен к четвертому выходу делителя частоты, выход датчика напряжения сети соединен через пороговый блок с входом логического элемента ИЛИ, другой вход которого соединен с выходом нуль-органа, а выход логического элемента ИЛИ - с R-входом RS-триггера. 2. Источник постоянного напряжения по п. 1, отличающийся тем, что делитель частоты выполнен в виде четьфех последовательно соединенных нетактируемых Т-триггеров и двух инверторов, при этом выход первого триггера подключен к первому выходу целителя частоты непосредственно, а через первый инвертор - к второму выходу делителя частоты, третий, четвертый и пятьй выходы делителя частоты подключены к выходам соответственно четвертого, второго и третьего триггеров.

J.

Т/г

Uz

Af

It

IZZ3

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный стабилизатор постоянного напряжения | 1980 |

|

SU978130A1 |

| Транзисторный конвертор | 1979 |

|

SU957379A1 |

| Стабилизированный конвертор напряжения | 1979 |

|

SU830618A2 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ В ПОСТОЯННОЕ | 1990 |

|

RU2006154C1 |

| Импульсный стабилизатор постоянного напряжения | 1987 |

|

SU1471181A1 |

| Устройство для управления стабилизирующим преобразователем постоянного напряжения | 1986 |

|

SU1534678A1 |

| Стабилизированный преобразователь постоянного напряжения | 1985 |

|

SU1293801A1 |

| ИСТОЧНИК ПИТАНИЯ С ЗАЩИТОЙ ОТ ПЕРЕГРУЗКИ | 2003 |

|

RU2256998C1 |

| Многоканальный стабилизированный преобразователь | 1981 |

|

SU993404A1 |

| РЕЗЕРВИРОВАННЫЙ ИСТОЧНИК ПИТАНИЯ ПОСТОЯННОГО НАПРЯЖЕНИЯ | 2003 |

|

RU2251777C2 |

Изобретение относится к вторичным источникам питания радиоаппаратуры. Целью изобретения является повышение надежности в работе стабилизированного источника постоянного напряжения. Поставленная цель достигается стробированием селекторов 6,7, управляющих усилителем 8 мощности в начале тактовых интервалов для предотвращения режимов сквозных токов усилителя 8, а также путем стробиро- вания сигналов управления усилителем 8 при уменьшении входного напряжения ниже заданного или при увеличении выходного напряжения выше заданного. 1 1 з.п. ф-лы, 18 шт. 00 со

.

04

22

23

U2.5

t/,

on,i

U,

ОС

19

d2

21 57

-«

IJJ

jg

Hh

fi

-оИ

, 0-52

0/U4UU. О

Я2.5

SO

Фи2. W

o9i

3VT1 О yfy

o3vrit уг

03VT2 зУЗ

3VT3 О Общий

30

О

i/J

Л mmn

СТ Б в СТ г

г/4.

Т о

иг.12

-ff «

. f/

о 4-у.

мг.

.

ЪЬ 55.. 5У

/.

сг

f/,

(Put. 13

9U2. 1

{ZU-

E

И

Фиг.15

п

г

75 Ь

9U2.16

8

179

(/оп.9

ЛНС

82

85

8S

Ff-

т

С 8S

Jli

Я

-.f,

С2

Обилий

о

Vu., 11

Составитель А.Боженов Редактор Н.Тупица Техред В.Кадар Корректор Г.Решетник

Заказ 1798/41 Тираж 864Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

т , ..

4- $Ш,Ш&

9иг. 1В

| Стабилизированный источник постоянного напряжения | 1975 |

|

SU548929A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Стабилизированный преобразовательпОСТОяННОгО НАпРяжЕНия | 1979 |

|

SU817696A2 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-05-07—Публикация

1985-12-23—Подача