1

Изобретение относится к вычислительной технике и предназначено для реализации произвольной логической функции четырех переменных.

Цель изобретения - упрощение мо- дуля.

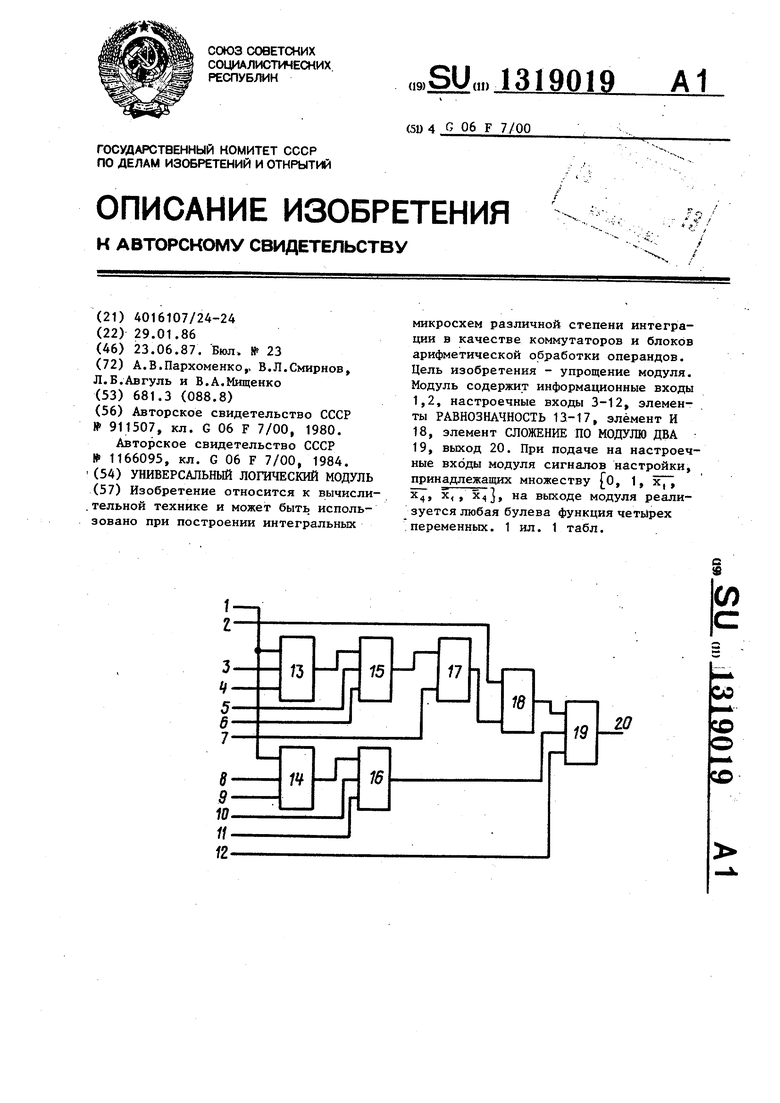

На чертеже представлена схема унверсального логического модуля.

Модуль содержит информационные входы 1-2, настроечные входы 3-12, элементы РАВНОЗНАЧНОСТЬ 13-17, элемент И 18, элемент СЛОЖЕНИЕ ПО МОДУЛЮ ДВА 19 и выход 20. Модуль работает следующим образо

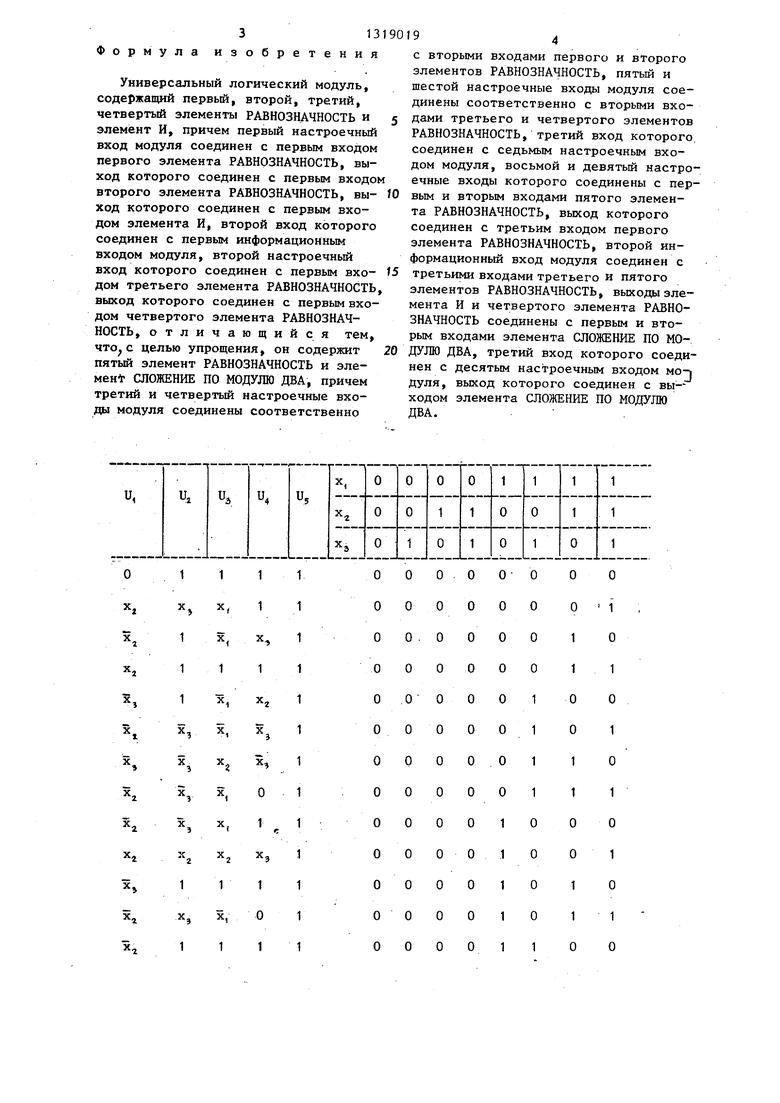

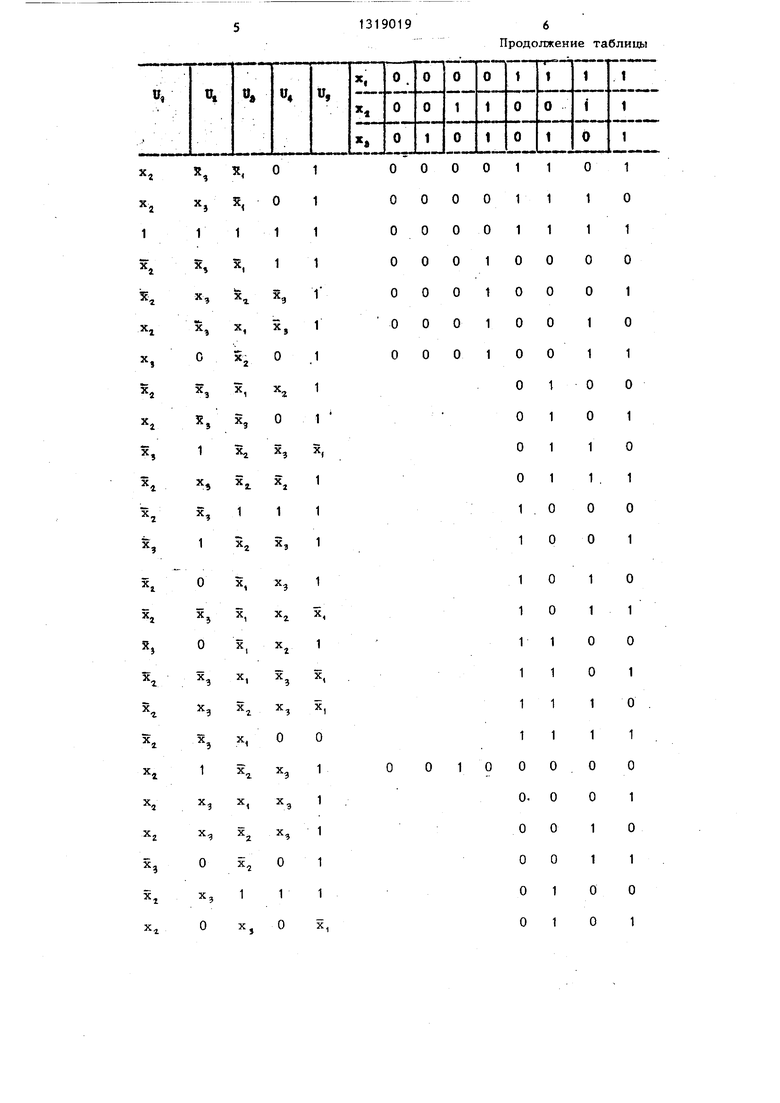

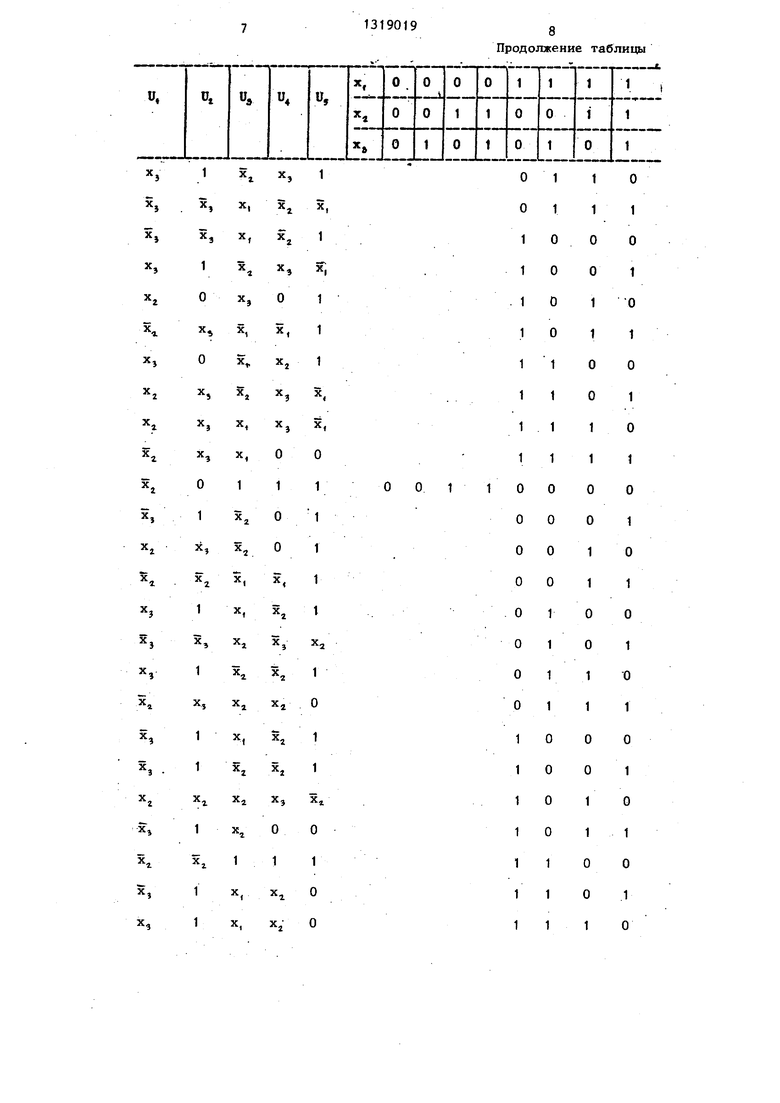

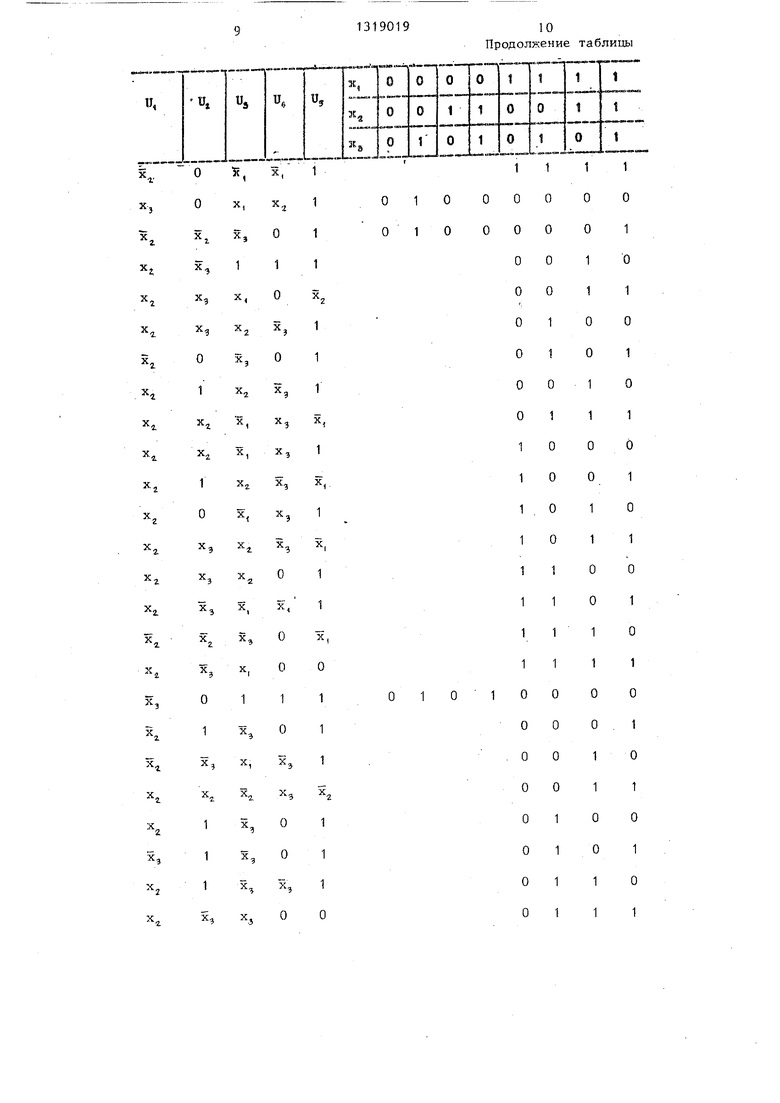

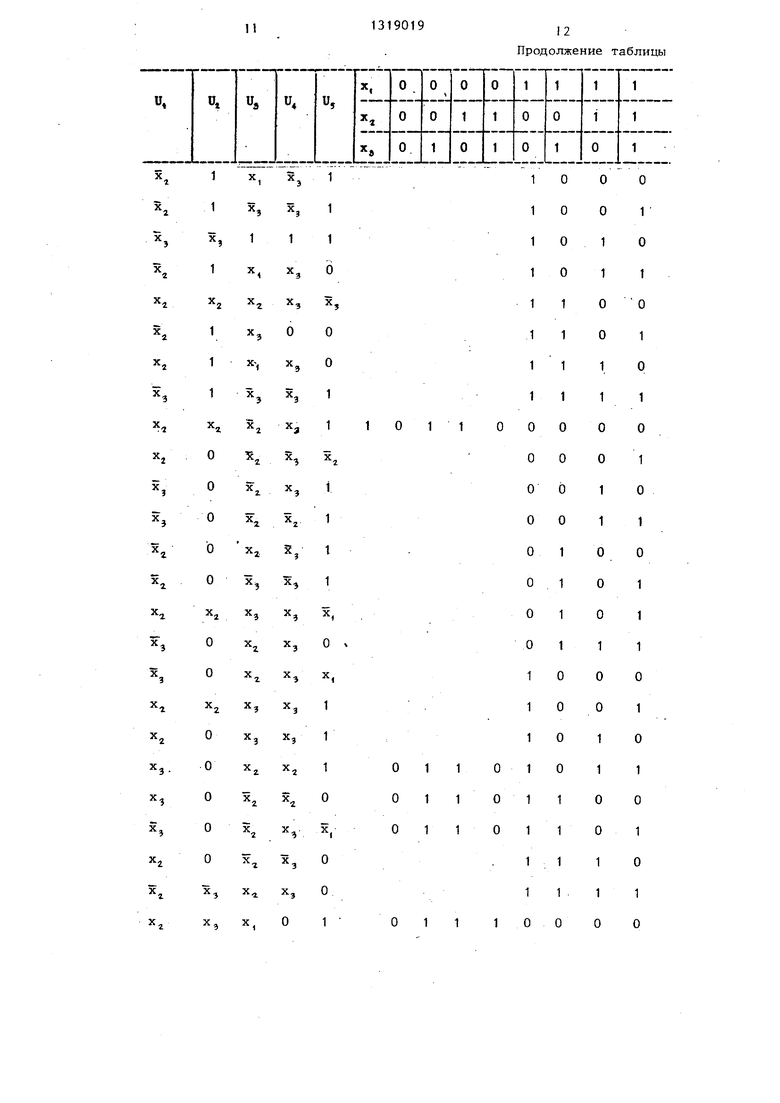

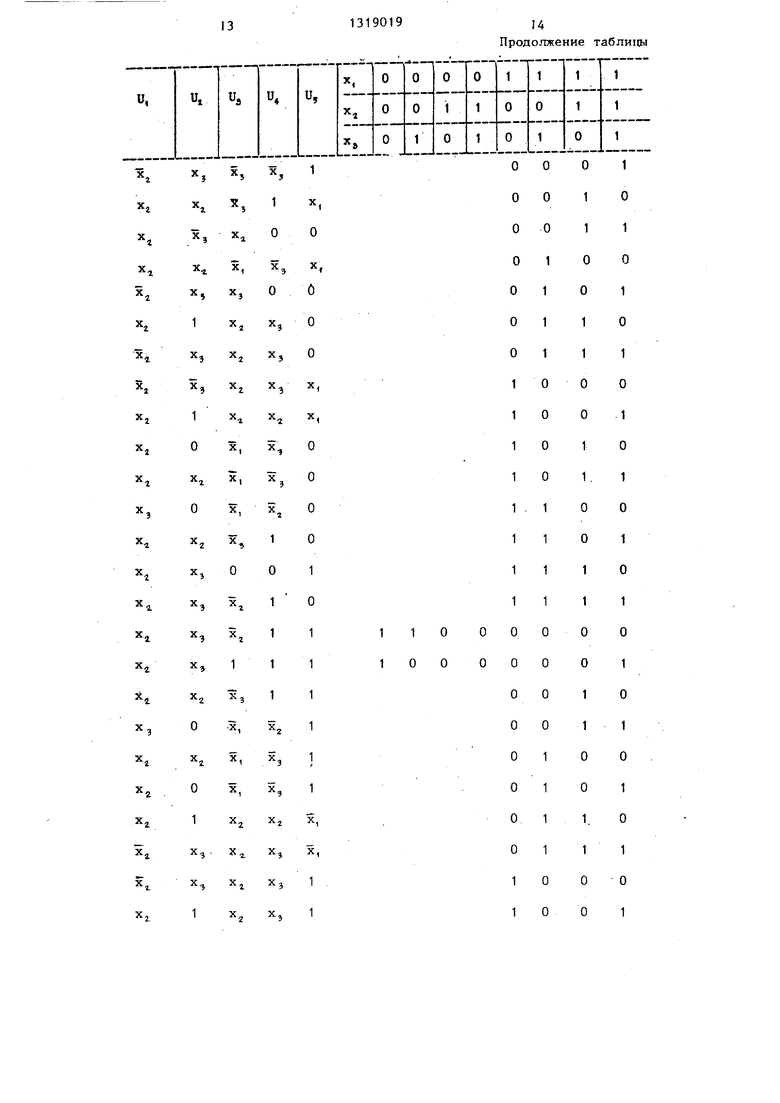

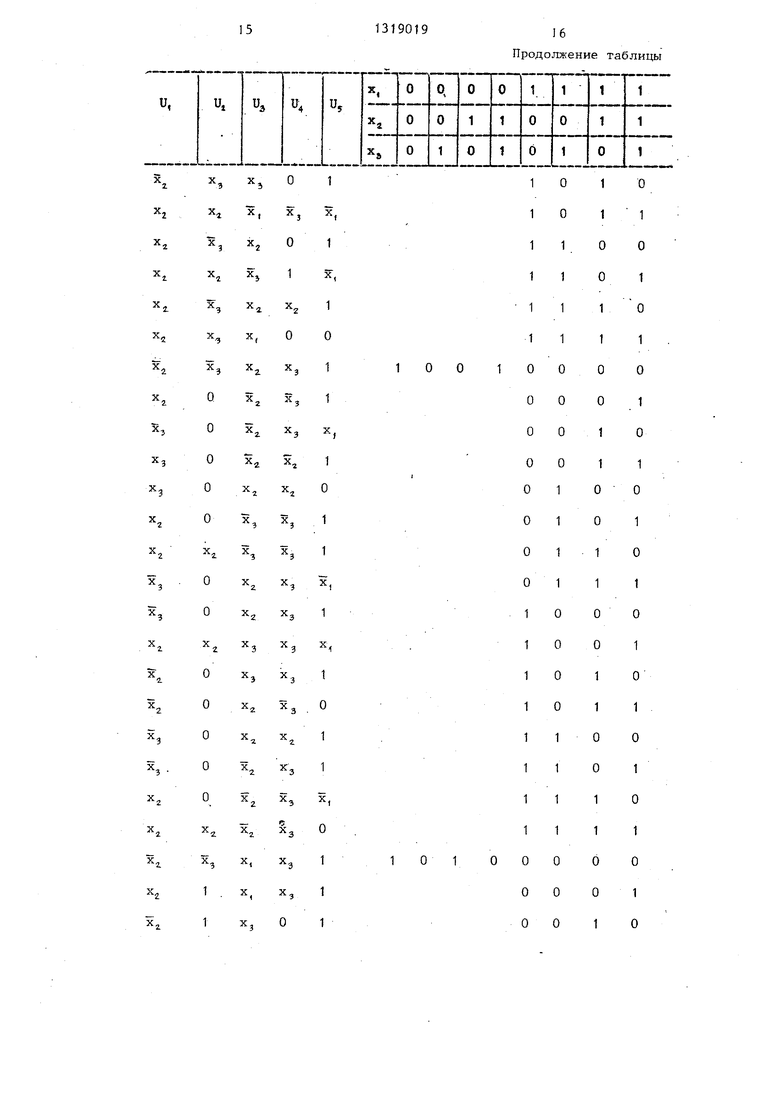

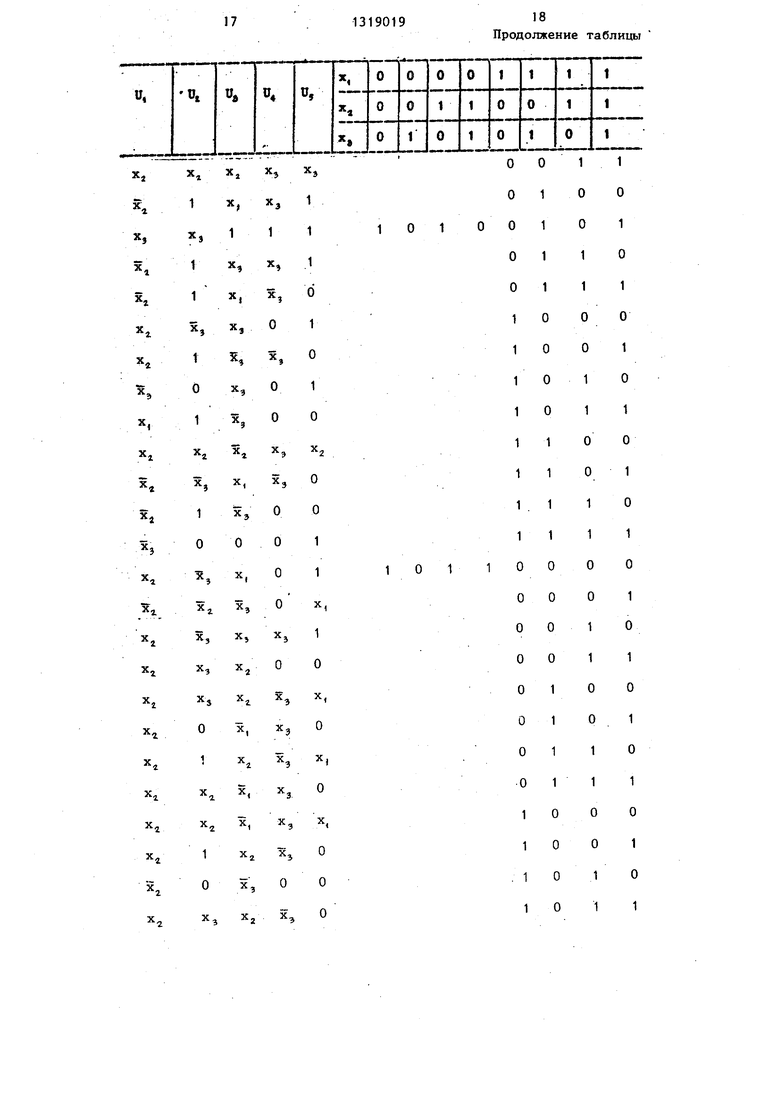

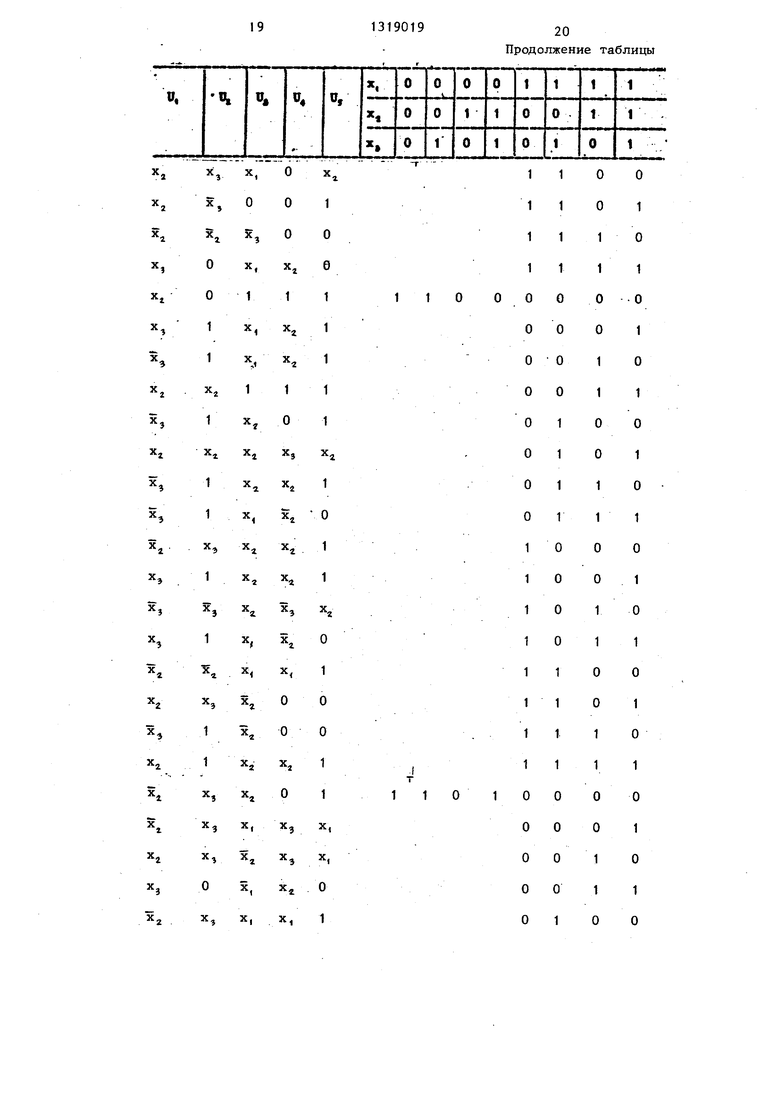

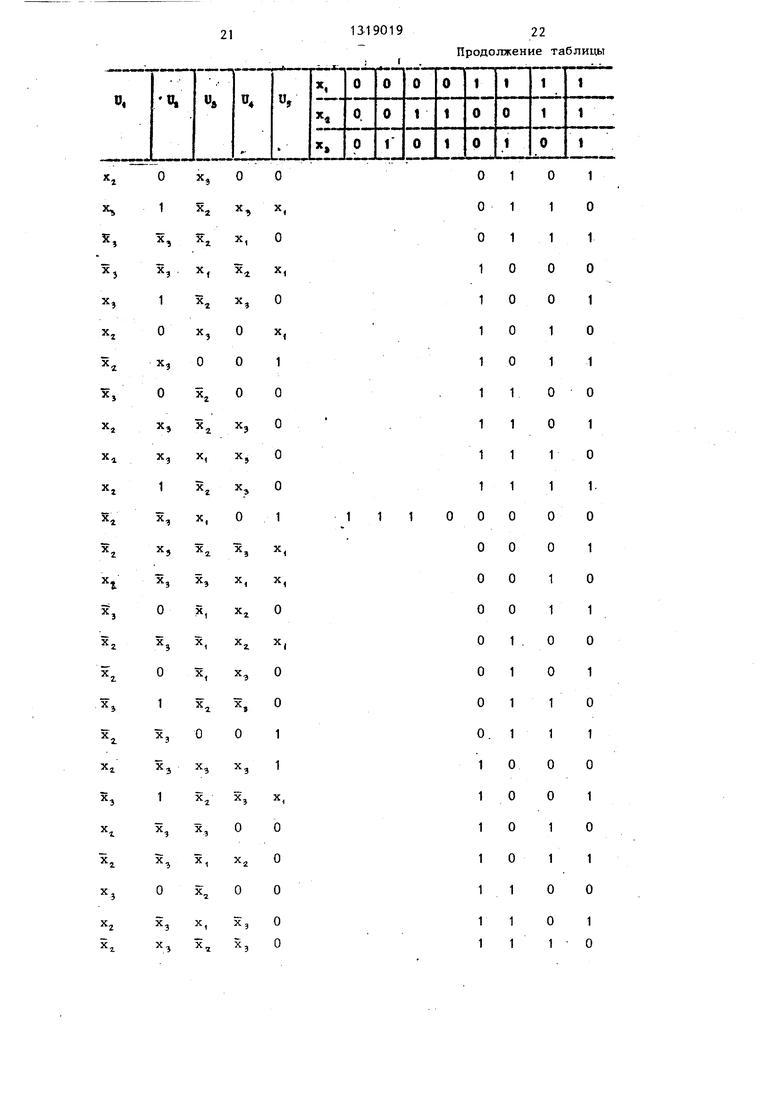

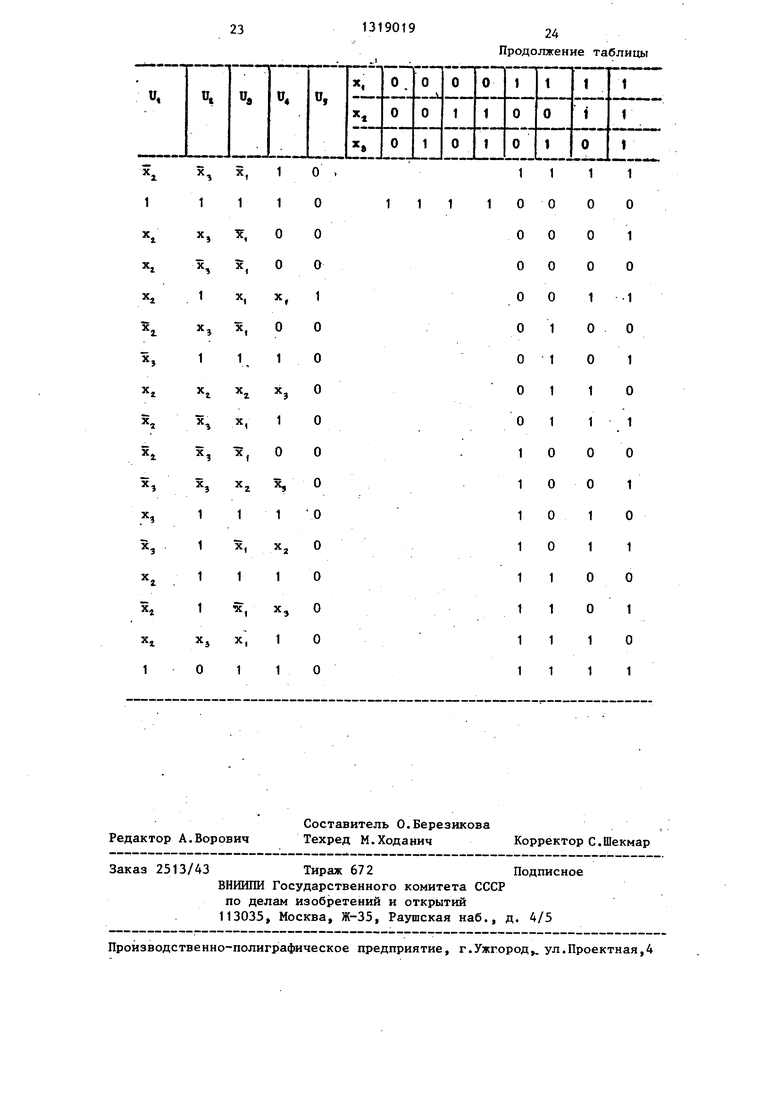

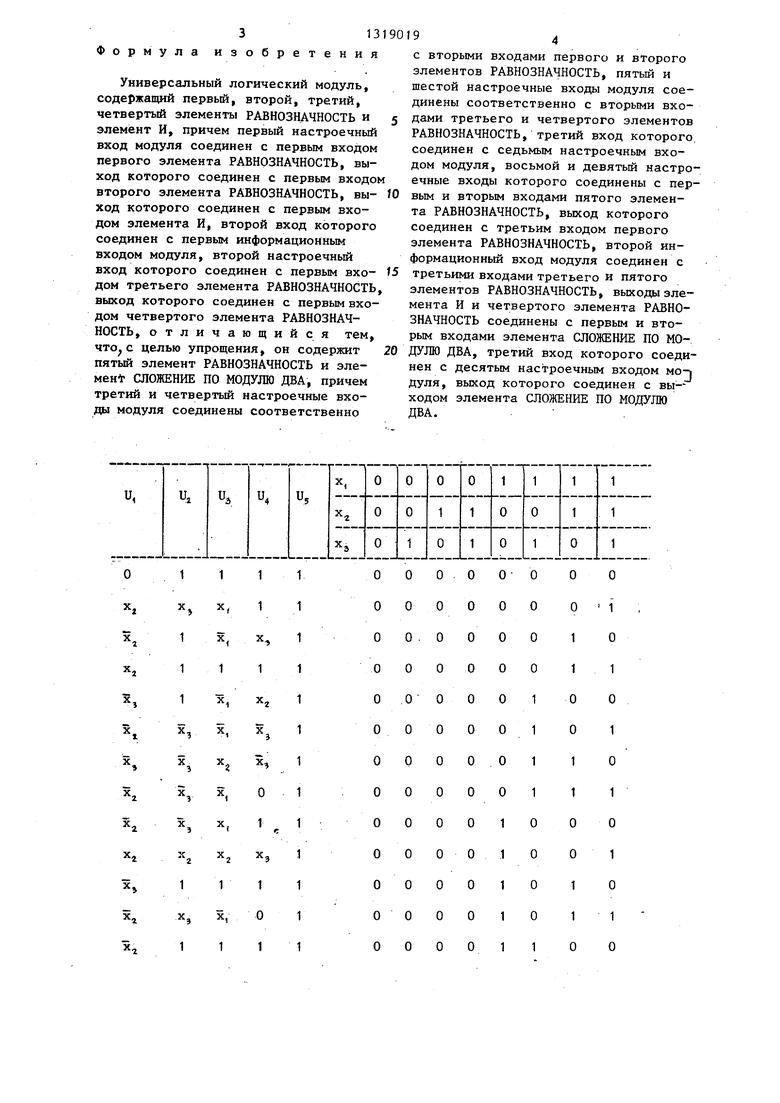

На настроечные входы 3-12 модуля подаются настроечные сигналы U, которые могут принимать значения о, 1, X,, X4, X,, X4l С выхода пятого элемента РАВНОЗНАЧНОСТЬ 17 снимается следующая логическая зависимость

f,f,u.vf,y5

,U,U,vf,U,U,, (1) где

f, x,U,U,vx,u,U,,

которая при различных значениях настроечных сигналов на настроечных .входах 3-7, приведенных в таблице, реализует любые булевы функции, зависящие от трех переменных Xj - х, f (х, ,х,0 . С выхода 20 универсалного логического модуля, учитывая, что на выходе четвертого элемента РАВНОЗНАЧНОСТЬ 16 реализуется функция f,f,UeU,vf,UgU,, где

,UeU,vx,U6U,

снимается следующая логическая зависимость :

,(f,F,vf5F,)vS,F,,

(2)

где

F.f4U,oVf.U,, .

(3)

Сравнивая выражения (1) и (3), видим, что логическая зависимость вида (3) также реализует путем подачи на настроечные входы сигналов настройки в соответствии с таблицей любые булевы функции трех переменных f (х, ,х) . .

Анализируя выражение (2), видим, что на выходе 20 универсального логического модуля реализуется любая булева функция четырех переменных f(х,,х). Покажем это. Любая булева функция в соответствии с разложением

19 . 2

Шеннона может быть представлена в виде

FMCK (Х, ,X),(x,,X,)(x,,X,).

Приравнивая правую часть выражения (2) к данному представлению функции, видим, что всегда однозначно могут быть определены функции f,, F

Fy и(Г77х;ь

(t, (х, ,x,),cf(x, ,х,)),

которые, как было показано, являются логическими функциями трех переменных.

Рассмотрим алгоритм настройки. Пусть f(х,,Х2,х,Хц) - реализуемая модулем логическая функция четырех переменных. Тогда определим некоторую логическую функцию

Uf(yi,-K,:,x)i(.y.,x,y.,-K) и представим ее в виде

tf(xi,,x, ,х,х,)х.ч(х, ,х,)®с(х, ,х,).

Причем, если

Cf(x,x,,x,x)x у, (x,,x,)vx (,).

то

tf ,(x,,x) 5,(x,,x)®y(x,x,)i . Vi(x, ,Xj) J,(x, ,х,).

По виду функций ( (x,,x.j) и ,,х) из таблицы находим настройки модуля на реализацию функций f (х, ,х). При этом функция () определяет сигналы настройки U,,..., Uj, а функция С)) (х, ,Xj) - сигналы настройки U6,..,,Uio (соответствие сигналов настройки в таблице (.Uj

и,, ,, u,U8, ,, и5,и„ ).

Пример. Определить настройки модуля на функцию f(х,,х) x,.

Очевидно, вектор ее значений (таблица истинности) имеет вид: Y, (0,0, 0,1,0,0,0,1,0,0,0,1,1,1,1,1). Следовательно, вектор значений функ- 1щи If (х,,х,,Хг,хз)(зГГ;ЗЕ7)

Yvp(0,0,0,0,0,0,1,1,0,1,0,1,0,1, . 1,1). Тогда .

YV, (0,1,0,1,0,1,0,0); Y( (1,1,1,1,1,1,0,0).

Из таблицы находим настройки модуля U,x,v и, 1; и,хз , Uj 1i Ug

х,-, u,,n .

313

Формула изобретения

Универсальный логический модуль, содержащий первый, второй, третий, четвертый элементы РАВНОЗНАЧНОСТЬ и элемент И, причем первый настроечный вход модуля соединен с первым входом первого элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с первым входом второго элемента РАВНОЗНАЧНОСТЬ, вы- ход которого соединен с первым входом элемента И, второй вход которого соединен с первым информационным входом модуля, второй настроечный вход которого соединен с первым вхо- дом третьего элемента РАВНОЗНАЧНОСТЬ выход которого соединен с первым входом четвертого элемента РАВНОЗНАЧНОСТЬ, отличающийся тем, что с целью упрощения, он содержит пятый элемент РАВНОЗНАЧНОСТЬ и элемент- СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, причем третий и четвертый настроечные входы модуля соединены соответственно

X,

х„

194

с вторыми входами первого и второго элементов РАВНОЗНАЧНОСТЬ, пятый и шестой настроечные входы модуля соединены соответственно с вторыми входами третьего и четвертого элементов РАВНОЗНАЧНОСТЬ, третий вход которого, соединен с седьмым настроечным входом модуля, восьмой и девятый настроечные входы которого соединены с первым и вторым входами пятого элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с третьим входом первого элемента РАВНОЗНАЧНОСТЬ, второй информационный вход модуля соединен с третьими входами третьего и пятого элементов РАВНОЗНАЧНОСТЬ, выходы элемента И и четвертого элемента РАВНОЗНАЧНОСТЬ соединены с первым и вто- pbw входами элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, третий вход которого соединен с десятым настроечным входом мо-| дуля, выход которого соединен с вы- ходом элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА.

о О 0.0 0-0 000000

о 0.0 о о о

000000

о .0 о о о

00 о 01

о о 00 1

00001 00010 о 001 о 0 о о 1 о 0 о о 1 о

о

о

о 1

Продолжение таблицы

и,

D,

О.

1 О

X,

X,

X

О 1

X,

х„

X,

X,

( г

Xj

г 1

X,

о О 1

11

1319019

12 Продолжение таблицы

X,

о 1

,

,

„

,

„

.

Хз X, Х X, Xj X,

Q X,

О

О О О

i О

о

2

о о о о

f.

о X,

л

Х X, X, X,

о

1

Х X,

X,

X, Х

X,

X,

Х X,

X,

Х X,

Х Х«5 X.

, 1

5f,

1 о

1 1

о 1

1

X,

X,

1 о 1

1

. о

1 1 1

Продолжение таблицы

О О

01

1О

1о

11

11

11

11

1 оо

оо

оо

оо

о1

о1

о1

01

1о 1о

1о

1о

11

11

11

11

000

оо

оо

1 1

о о 1 1 о о 1

1 о

о 1 1 о о 1 1 о о 1 1 о о 1

о 1 о 1

о 1

о 1 о

1 о

1

о 1

о 1 о 1

о 1

о 1

о 1 о

X, Х, Xj

,

1

Xj

1 1

э

1 о

1

г

1

О ,

X, Хз 1

1 1

Х X,

X,

X,

3с, X,

X,

о О

О

1 1 О 1 О 1

О О

г 2

X, Хэ О

О О

X

X, о

X, Xj 1

о О

,

Хз

О

1

X.

2

1

О

X,

х X, X,

X, х, о

X, X, X,

3 о

«3 «

X, X, о х , о О

X, X,

О 1

о 1

оо

о1

001

о1

01

1о 1

1

О

о

1о

11

11

1 .1

11

1 оо

оо

оо

оо

о1

о1

о1

о1

1о

1о

. 1о

1о

1

о

о

1

1

о

о

1

1

о

о

1

1

о

о

1

1

о

о

1

1

о

о

1

1

1

о

1

о

1

о

1

о

1

о

1

о

1

о

1

о

1

о

1

о

1

о

1

о

1

23

1

г

,

1 х«

х.

1

,

X.

X.

1

X,

1

5.

1 1 о

О

,

О

1

1

О

1

X,

О О

о о 1

о о о о о о

О

о о о о о

Редактор А.Ворович

Составитель О.Березикова Техред М.Ходанич

Заказ 2513/43Тираж 672Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Про1€зводственно-полиграфическое предприятие, г.Ужгород,, ул.Проектная,4

1 1

1 1

о о

о о

о о

о о

о

о

о

о

1

1

1

1

24 Продолжение таблицы

1 1

1

11

0о

о1

0о

11 оо

01

1о 11 оо

01

1о

11

11 00 1101 1110

1111

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1985 |

|

SU1320808A1 |

| Универсальный логический модуль | 1986 |

|

SU1319018A1 |

| Универсальный логический модуль | 1984 |

|

SU1234825A1 |

| Универсальный логический модуль | 1984 |

|

SU1251064A1 |

| Устройство для вычисления симметрических булевый функций | 1988 |

|

SU1689943A1 |

| Многофункциональный логический модуль | 1985 |

|

SU1247858A1 |

| Универсальный логический модуль | 1983 |

|

SU1148024A1 |

| Универсальный логический модуль | 1984 |

|

SU1218375A1 |

| Универсальный логический модуль | 1987 |

|

SU1536370A1 |

| Универсальный логический модуль | 1986 |

|

SU1335974A1 |

Изобретение относится к вычисли- .тельной технике и может быть использовано при построении интегральных fг3ч5678 9 10. //- f213 - г- 15 JP т ч 16 микросхем различной степени интеграции в качестве коммутаторов и блоков арифметической обработки операндов. Цель изобретения - упрощение модуля. Модуль содержит информационные входы 1,2, настроечные входы 3-12, элементы РАВНОЗНАЧНОСТЬ 13-17, элемент И 18,элемент СЛОЖЕНИЕ ПО МОДУЛЮ ДВА 19,выход 20. При подаче на настроечные входы модуля сигналов настройки, принадлежащих множеству (0, 1, х, , х, X,, х, на выходе модуля реализуется любая булева функция четырех .переменных. 1 ил. 1 табл. (Л 17 16 16 19 го САЭ СО О х

| Универсальный логический модуль | 1980 |

|

SU911507A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Универсальное логическое устройство | 1984 |

|

SU1166095A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-23—Публикация

1986-01-29—Подача