Изобретение относится к электротехнике, в частности к стабилизированным источникам питания с импульс- ньгм регулированием,- и может быть использовано для питания различной электронной и рентгеновской аппаратуры.

Цель изобретения - повышение КПД стабилизатора, его надежнйсти путем увеличения точности срабатывания защиты и получение пониженного выходного напряжения.

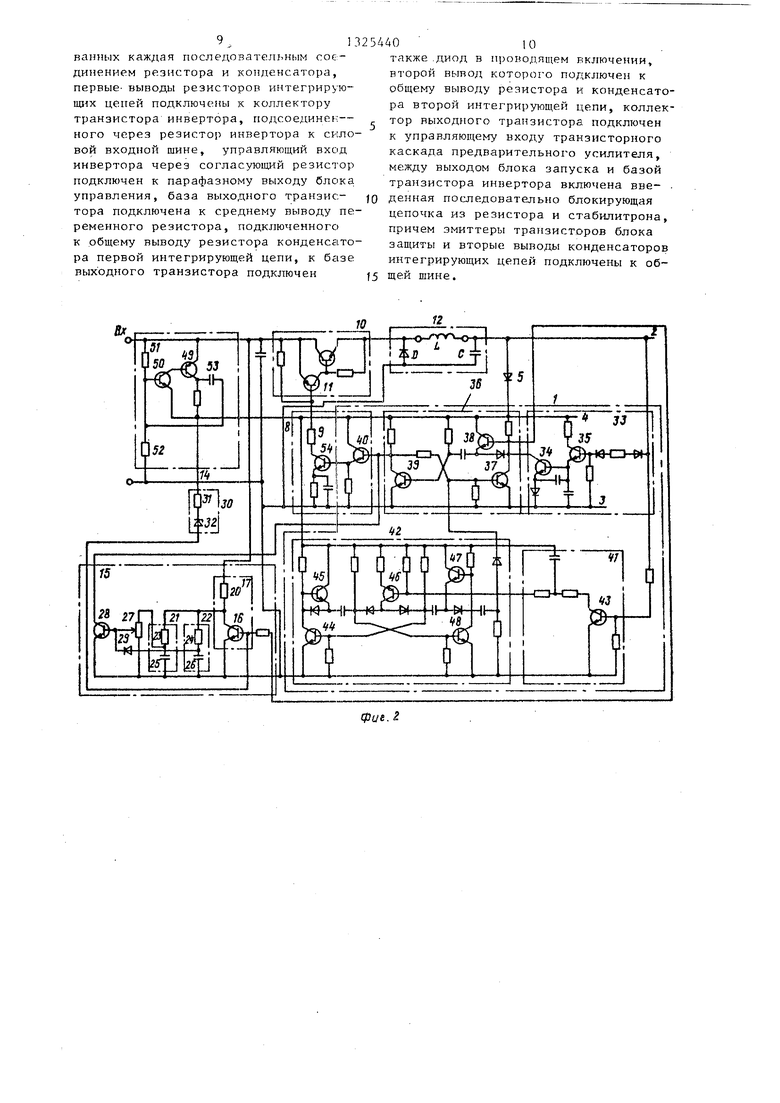

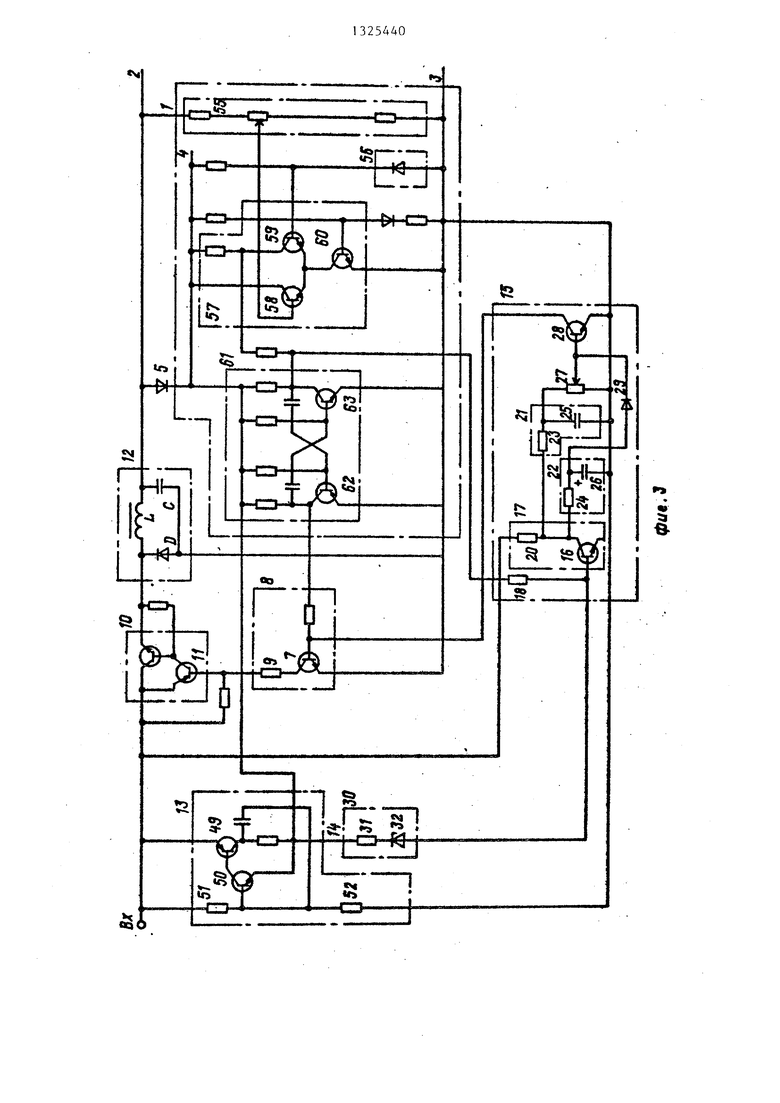

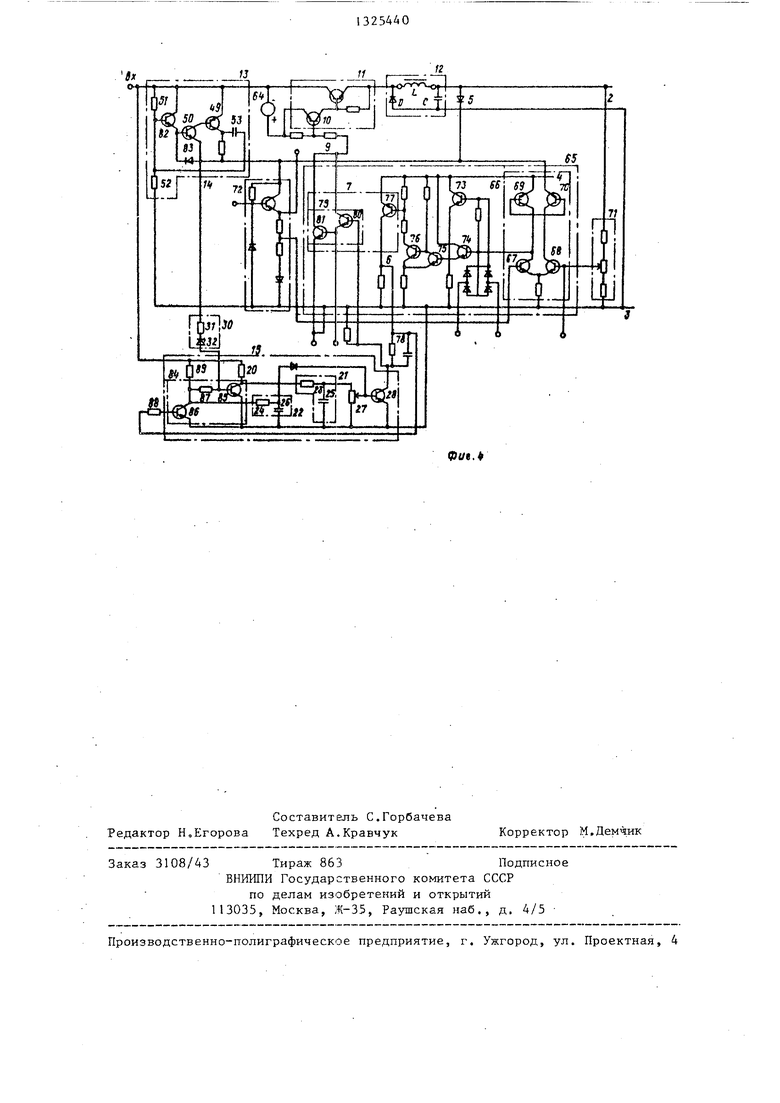

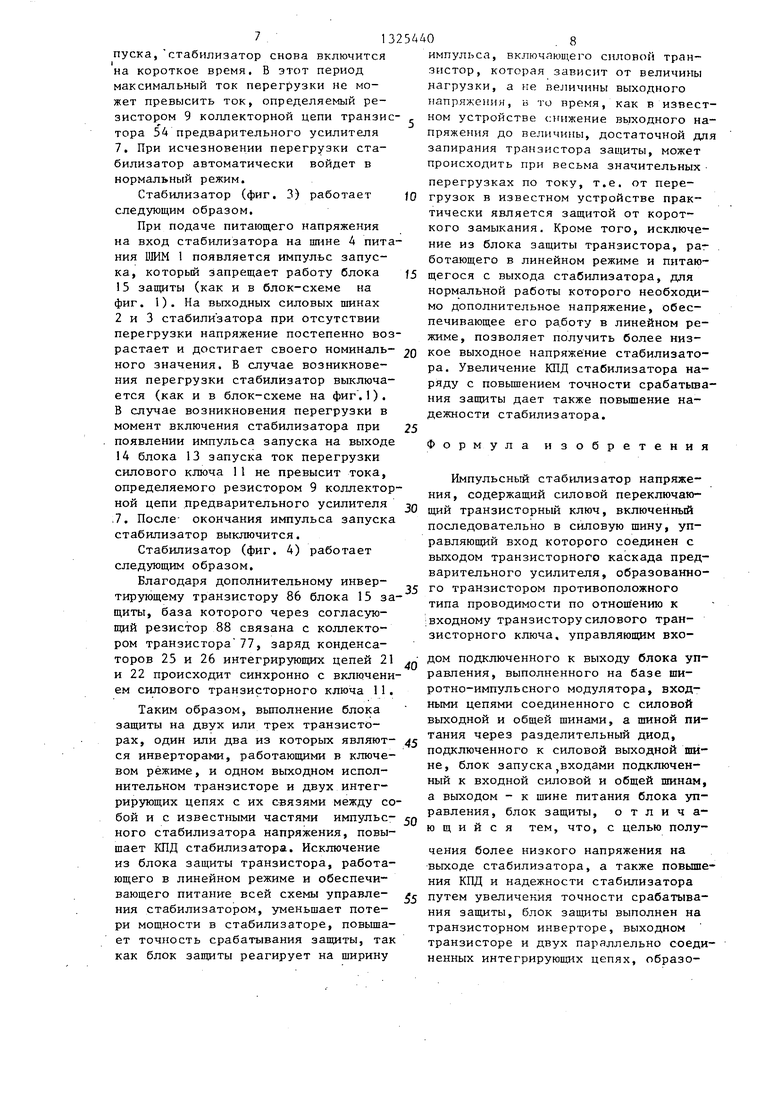

На фиг. I представлена блок-схема импульсного стабилизатора напряжения; на фиг. 2 - принципиальная схема одного из примеров практического выполнения импульсного стабилизатора на фиг. 3 и 4 - принципиальные схемы других примеров выполнения импульсного стабилизатора.

Импульсный стабилизатор (фиг, 1) содержит блок управления, выполненный на базе пшротно-импульсного модулятора (ШИМ) 1, который входными клемами подключен к силовой выходной ши не 2 и общей шине 3, а его шина 4 питания через разделительный диод 5 подключена к выходной силовой шине 2. К выходной клемме 6 ШИМ 1 подключен управляющий вход транзисторного каскада предварительного усилителя 7, транзистор 8 которого коллектором подключен через резистор 9 к базе- транзистора 10 силового пере

ключающего транзисторного ключа 11, который может быть построен как на одном, гак и на составном транзисторе, причем входной транзистор 10 силового транзисторного ключа 1I имеет противоположный тип проводимости по сравнению с транзистором 8 транзисторного каскада предварительного усилителя 7. Эмиттер выходного транзистора силового ключа 11 соединен с LCD-фильтром 12. Блок 13 запуска стабилизатора входами подключен к входной силовой шине и общей шине а выходом 14 - к шиие 4 питания ШИМ 1. Блок 15 защиты включает в себя транзистор 16 инвертора 17, База транзистора 16- через согласующий резистор 18 соединена с парафазным выходом 19 ШИМ 15 а коллектором через резистор 20 инвертора 17 - с входной силовой шиной. К коллектору транзистора 16 подключены первыми выводами две интегрирующие цепочки 21 и 22, состоящие из последовательно- соединенных резисторов 23, 24 и

O

5

5

о

0

5

0

5

0

5

конденсаторов 25 и 26 соответственно. Вторыми выводами интегрирующие цепочки 21 и 22 подключены к общей атне 3. Интегрирующие цепочки 21 и 22 обладают разным временем интегрирования, причём вторая интегрирующая цепь 22 обладает существенно большим временем интегрирования,-чем первая. Параллельно конденсатору 25 первой интегрирующей цепочки 21 подключен переменный резистор 27 (или два последовательно соединенных резистора) , движок которого подсоединен к базе выходного транзистора 28 и соединен с движком (средним выводом) переменного резистора 27 через диод 29, включенный в проводящем направлении (либо стабилитрон в обратном включении). Выход 14 блока 13 запуска соединен с первым выводом блокирующей последовательной цепочки 30 из резистора 31 и стабилитрона 32, вторым выводом подключенной к базе транзистора 16 инвертора 17. ШИМ 1 на фиг. 2 содержит блок 33 управления широтно-импульсным модулятором 1, построенный на транзисторах 34 и 35, входными цепями подключенный к выходной шине 2 и общей шине 3 стабилизатора, одновибратор 36 с управляемой шириной импульса, включающий в себя транзисторы 37-39 и часть транзисторного каскада предварительного усилителя 7 на транзисторе 40. ижм 1 включает в себя также блок 41 управления частотой импульсного генератора 42 на транзисторе 43. Импульсный генератор 42 построен на транзисторах 44-48. Блок 13 запуска построен на транзисторах 49 и 50 противоположного типа проводимости и содержит таймирующие элементы в виде резистивного делителя, состоящего из резисторов 51 и 52 и конденсатора 53.

Управлякяций вход силового транзисторного ключа 11 соединен с выводом резистора 9, включенного в коллекторную цепь выходного транзистора 54, вхо-дящего в транзисторный каскад предварительного усилителя 7 наряду с входным его каскадом на транзисторе 40. Транзистор 54, как и транзистор 8 (фиг. 1), имеет противоположный тип проводимости по сравнению с транзистором 10 силового переключающего транзисторного ключа 11.

На фиг. 3 приведен другой пример выполнения импульсного стабилизатоpa напряжения,- в котором UttIM содержит делитель 55 обратной связи, источник 56 опорного напряжения, дифференциальный усилитель 57 на транзисторах 58-60, мультивибратор 61 на транзисторах 62 и 63, который управляется дифференциальным усилителем 57. Транзисторный каскад предварительного усилителя 7 управляющим входом подключен к выходу мультивиб- ратора 61, а выходом через резистор 9 - к управляющему входу силового транзисторного ключа 11 при том же условии относительно типов проводимости транзисторов, что и раньше,

В третьем примере выполнения (фиг. 4) импульсный стабилизатор с дополнительным источником 64 построен на основе интегральной микросхемы 65 типа К142ЕП1 и содержит диффе- ренциальный усилитель 66 на транзисторах 67-70, делитель 71 обратной связи, источник 72 опорного напряжения, эмиттерные повторители на транзисторах 73 и 74, триггер Шмидта на транзисторах .75 и 76. Транзисторный каскад предварительного усилителя 7 на транзисторе-77 коллектором связан через свой согласуюпщй резистор 78 со входом транзисторного каскада предварительного усилителя 7.9 на транзисторах 80 и 81, а эмиттером через вывод транзистора 77 образует выход 6 ШИМ 1. Блок 13 запуска выполнен на трех транзисторах 49, 50 и 82, два из которых 50 и 82 - противополо ного типа проводимости, и дополнительном диоде 83, включенном между эмиттером и базой транзистора 50, ко торьш содержит таймирующие элемен- ты: конденсатор 53 и резистивный делитель на резисторах 51 и 52. Выхо 14 блока 13 запуска соединен с блокирующей цепочкой 30 из резистора 31 и стабилитрона 32, которая вто- рым выводом подсоединена к одному из управляющих входов инвертор а 84 блока 15 защиты. Инвертор 84 имеет два инвертирующих транзистора 85 и 86. База первого из них 85 образует первый управляющий вход инвертора 84 и через резистор 87 соединена с коллектором второго транзистора 86, база которого образует второй управляющий вход совместно с согласующим резистором 88, который соединен с коллекторным выходом транзистора 77 Коллекторы транзисторов 85 и 86 через резисторы 20 и 89 инвертора соот

5 Q

5

0

5

ветственно гоедипгкы со входной силовой шиной. Эмиттеры транзисторов 85 и 86 соединены с общей шиной 3.

Импульсный стабилизатор напряжения (фиг. I) работает следующим образом.

При подаче постоянного нестабилизированного напряжения на входную силовую шину с выхода 14 блока 13 запуска на шину 4 питания 1 поступает импульс напряжения, который одновременно поступает на базу транзистора 16 блока 15 защиты через резистор 31 и стабилитрон 32. Выходной сигнал ШИМ 1 с выхода 6 поступает на вход транзистора 8 усилительного каскада 7, в цепи коллектора которого возникает ток. Соответствующий ток начинает протекать через силовой переключающий транзисторный ключ 11, и на выходной шине 2 стабилизатора -появляется напряжение, определяемое параметрами входных цепей ШИМ I (делитель обратной связи и источник опорного напряжения на фиг. 1 не. показаны) . По окончании действия запускающего импульса блок 13 запуска запирается выходным напряжением стабилизатора, которое поступает через разделительный диод 5, подключенный к выходной шине 2 в проводящем направлении, запирается и стабилитрон 32. При изменении нагрузки на выходе стабилизатора соотношение длительностей времени, когда на выходе .

6ШИМ 1 существуют высокий и низкий потенциалы, изменяется. В период времени, когда предварительный усилитель

7открыт, транзистор 16 блока 15 защиты заперт, так как на его базу поступают импульсы с парафазного выхода 19 ШИМ I, и конденсаторы 25 и 26 интегрирующих цепей 21 и 22 заряжаются. Конденсатор 26 второй интегрирующей цепи 22 заряжается до напряжения, значительно меньшего, чем конденсатор 25 первой интегрирующей цепи 21.

В период времени, когда транзистор 8 закрыт, т.е. на выходе 6 ШИМ 1 присутствует низкий потенциал, оба конденсатора 25 и 26 разряжазртся через резисторы 23 и 24 своих цепей 2 к 22 и насыщенный транзистор 16 блока 15 зацщты. При увеличении нагрузки время запертого состояния транзистора 16 увеличивается, что приводит к увеличению напряжения, на конденсаторе 25 цепи 21. При увеличении тока нагрузки сверх номинального выводной транзистор 28 устройства 15 защиты откроется, и ток с выхода 6 ШИМ 1 потечет через транзистор 28 устройства 15 защиты. Эпар- гия, поступившая на шину 2 стабилизатора, уменьшится, что приведет к падению напряжения на шине 2 стабилизатора, а это, в свою очередь, приведет к увеличению длительности им- пульса на выходе 6 НИМ 1 и к дальнейшему росту средней составляющей напряжения на конденсаторах 25 и 26, что приведет к практически мгновенному насыщению выходного транзисто- ра 28 блока 15 защиты с одновременным увеличением длительности импульса на выходе 6 ШИМ 1 при одновременном прекращении поступления энергии на шину 2 стабилизатора, т.е. вызо- нет запирание транзистора 8.

Таким образом, происходит лавинообразное увеличение длительности ширины импульса на выходе 6 ШИМ 1, на- сьш;ение вы содного транзистора 28 бло- ка 15 защиты и полное выключение стабилизатора, за счет осуществления в схеме положительной обратной связи Для более надежного насыщения выходного транзистора 28 служит вторая ин- тегрирующая цепь 22, величина сопротивления резистора 24 которой выбирается значительно меньше, чем величина сопротивления резистора 23 первой интегрирующей цепи 21. При закрывании транзистора 16 конденсатор 26 заряжается до величины, достаточной для отпирания диода 29, и вводит транзистор 28 в более глубокое насыщение

обеспечивая надежное выключение ста

билизатора. После того, как пройдет время, достаточное для восстановления блока 13 запуска, оно сформирует импульс, которьй подаст напряжение гштания на ШИМ и заблокирует на короткое время работу блока 15 защиты. При этом в случае короткого замыка - ния на выходе или большой перегрузки Ток перегрузки не может превысить величину, определяемую резистором 9. По окончании действия импульса запуска стабилизатор снова выключится на длительное время.

В случае отсутствия перегрузки стабилизатор автоматически войдет в нормальный режим. При возникновении перегрузки стабилизатор выключится, как было указано выше. При этом величина срабатывания по току перегруз

5 0

5 о

5

0

5

0

ки может быть установлена, прг.кти- чески, с какой угодно точностью, В зависимости от особенностей выполнения принципиальной схемы импульсного стабилизатора, особенностей исполнения микросхем блока управления импульсным стабилизатором конкретная схема исполнения блока 15 защиты может изменяться. При этом может несколько варьироваться протекание физических процессов в стабилизаторе. ,

Стабилизатор (фиг. 2) работает следующим образом.

При подаче питающего напряжения на входную клемму, т.е. на коллектор выходного транзистора силового ключа 11, с задержкой, определяемой величиной емкости конденсатора 53 и величиной сопротивлений резисторов 51 и 52 блока 13 запуска, на его выходе 14 появляется импульс запуска, который запрещает работу блока 15 защиты (в этот период выходной транзистор 28 блока 15 защиты заперт из-за того, что импульс запуска превышает потенциал пробоя стабилитрона 32 блокиру- ющей цепочки 30) и подает напряжение питания на шину 4 питания блока 33 управления ШИМ 1. Стабилизатор включается на пониженной частоте. В процессе запуска напряжение на выходных шинах 2 и 3 стабилизатора возрастает, частота работы импульсного генератора 42 и выходное напряжение стабилизатора достигают номинальной величины, импульс запуска заканчивается, и блок 13 запуска через- диод 5 запирается выходным напряжением стабилизатора. Одновременно запирается стабилитрон 32.

При увеличении нагрузки время открытого состояния силового транзисторного ключа И увеличивается, что ведет к нарастанию напряжения на конденсаторах 25 и 26 интегрирующих цепей 21 и 22 блока 15 защиты, а следовательно, и на базе транзистора 28 блока 15 запреты. При превьшении. номинального тока нагрузки транзистор 28 откроется и мгновенно войдет в насыщение в силу возникновения в схеме стабилизатора положительной обратной связи (как это описано для блок-схемы на фиг. 1). Следовательно, стабилизатор выключается. Когда конденсатор 53 блока 13 запуска перезарядится до напряжения, достаточного для срабат1 1вания блока 13 за

пуска, стабилизатор снова включится на короткое время. В этот период максимальный ток перегрузки не может превысить ток, определяемый резистором 9 коллекторной цепи транзистора 54 предварительного усилителя 7, При исчезновении перегрузки стабилизатор автоматически войдет в нормальный режим.

Стабилизатор (фиг. 3) работает следующим образом.

При подаче питающего напряжения на вход стабилизатора на шине А питания иЖМ 1 появляется импульс запуска, который запрещает работу блока 15 защиты (как и в блок-схеме на фиг. 1). На выходных силовых шинах 2 и 3 стабилизатора при отсутствии перегрузки напряжение постепенно возрастает и достигает своего номиналь- ного значения. В случае возникновения перегрузки стабилизатор выключается (как и в блок-схеме на фиг . 1). В случае возникновения перегрузки в момент включения стабилизатора при появлении импульса запуска на выходе 14 блока 13 запуска ток перегрузки силового ключа 11 не превысит тока, определяемого резистором 9 коллекторной цепи предварительного усилителя .7, После- окончания импульса запуска стабилизатор выключится.

Стабилизатор (фиг. 4) работает следующим образом.

Благодаря дополнительному инвертирующему транзистору 86 блока 15 защиты, база которого через согласующий резистор 88 связана с коллекто

Импульсный стабилизатор напряжения, содержащий силовой переключающий транзисторный ключ, включенный последовательно в силовую шину, уп- равляюпщй вход которого соединен с выходом транзисторного каскада предварительного усилителя, образованного транзистором противоположного типа проводимости по отношению к iвходному транзистору силового транзисторного ключа, управляющим вхором транзистора 77, заряд конденсаторов 25 и 26 интегрирующих цепей 21 дом подключенного к выходу блока упи 22 происходит синхронно с включением СЮ1ОВОГО транзисторного ключа 11.

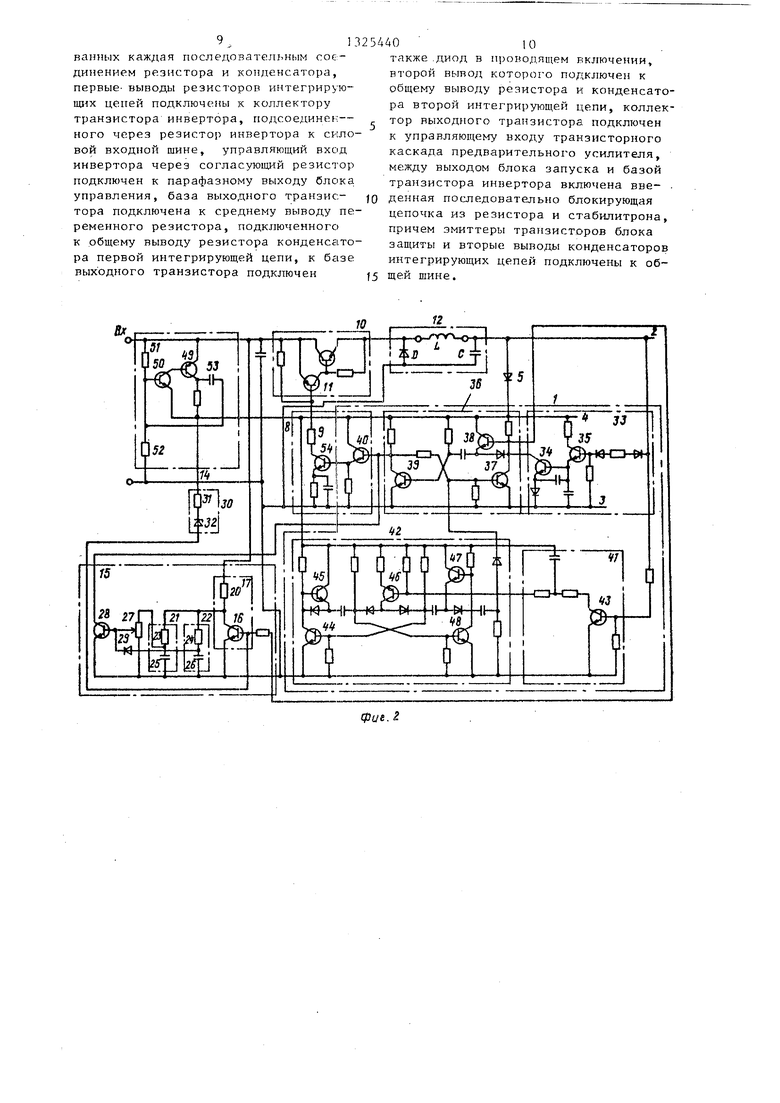

Таким образом, вьшолнение блока защиты на двух или трех транзисторах, один или два из которых являют- 5 ся инверторами, работающими в ключевом режиме, и одном выходном исполнительном транзисторе и двух интегрирующих цепях с их связями между собой и с известными частями импульс- Q ного стабилизатора напряжения, повышает КПД стабилизатора. Исключение из блока защиты транзистора, работающего в линейном режиме и обеспечивающего питание всей схемы управле- с ния стабилизатором, уменьшает потери мощности в стабилизаторе, повьш1а- ет точность срабатывания защиты, так как блок защиты реагирует на ширину

равления, выполненного на базе ши- ротно-импульсного модулятора, входными цепями соединенного с силовой выходной и общей шинами, а шиной питания через разделительный диод, подключенного к силовой выходной шине, блок запуска ,входами подключенный к входной силовой и общей шинам, а выходом - к шине питания блока управления, блок защиты, отличающийся тем, что, с целью получения более низкого напряжения на выходе стабилизатора, а также повьш1е ния КПД и надежности стабилизатора путем увеличения точности срабатывания защиты, блок защиты выполнен на транзисторном инверторе, выходном транзисторе и двух параллельно соединенных интегрирующих цепях, образо

импульса, включающего силовой транзистор, которая зависит от величины нагрузки, а не величины выходного напряжения, в то время, как в известном устройстве снижение выходного напряжения до величины, достаточной для запирания транзистора защиты, может происходить при весьма значительных перегрузках по току, т.е. от перегрузок в известном устройстве практически является защитой от короткого замыкания. Кроме того, исключение из блока защиты транзистора, работающего в линейном режиме и питаю- щегося с выхода стабилизатора, для нормальной работы которого необходимо дополнительное напряжение, обеспечивающее его работу в линейном режиме, позволяет получить более низкое выходное напряжение стабилизатора. Увеличение КПД стабилизатора наряду с повьшением точности срабатьта- ния защиты дает также повьппение надежности стабилизатора.

Формула изобретения

Импульсный стабилизатор напряжения, содержащий силовой переключающий транзисторный ключ, включенный последовательно в силовую шину, уп- равляюпщй вход которого соединен с выходом транзисторного каскада предварительного усилителя, образованного транзистором противоположного типа проводимости по отношению к входному транзистору силового транзисторного ключа, управляющим входом подключенного к выходу блока упдом подключенного к выходу блока управления, выполненного на базе ши- ротно-импульсного модулятора, входными цепями соединенного с силовой выходной и общей шинами, а шиной питания через разделительный диод, подключенного к силовой выходной шине, блок запуска ,входами подключенный к входной силовой и общей шинам, а выходом - к шине питания блока управления, блок защиты, отличающийся тем, что, с целью получения более низкого напряжения на выходе стабилизатора, а также повьш1е ния КПД и надежности стабилизатора путем увеличения точности срабатывания защиты, блок защиты выполнен на транзисторном инверторе, выходном транзисторе и двух параллельно соединенных интегрирующих цепях, образованных каждая последовательным соединением резистора и конденсатора, первые- выводы резисторов интегрирующих ценен подключены к коллектору транзистора инвертора, подсоединер-;- ноге через резистор инвертора к силовой входной шине, управляющий вход инвертора через согласующий резистор подключен к парафазному выходу блока управления, база выходного транзис- тора подключена к среднему выводу переменного резистора, подключенного к общему выводу резистора конденсатора первой интегрирующей цепи, к базе выходного транзистора подключен

JQ|5

5440 10

также .диод в проводящем включении, второй вывод которого подключен к общему выводу резистора и конденсатора второй интегрирующей цепи, коллектор выходного транзистора подключен к управляющему входу транзисторного каскада предварительного усилителя, между выходом блока запуска и базой транзистора инвертора включена вве- . денная последовательно блокирующая цепочка из резистора и стабилитрона, причем эмиттеры транзисторов блока защиты и вторые выводы конденсаторов интегрирующих цепей подключены к общей щине.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизированный транзисторный конвертор | 1977 |

|

SU736289A1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| Стабилизированный источник постоянного напряжения с защитой от пробоя в нагрузке | 1983 |

|

SU1157037A1 |

| Импульсный стабилизатор постоянного напряжения | 1991 |

|

SU1820944A3 |

| Стабилизированный преобразователь постоянного напряжения | 1981 |

|

SU1001366A1 |

| Регулируемый источник вторичного электропитания | 1989 |

|

SU1735978A1 |

| Устройство для регулирования температуры | 1982 |

|

SU1024891A1 |

| ИСТОЧНИК ВТОРИЧНОГО ЭЛЕКТРОПИТАНИЯ | 1995 |

|

RU2074492C1 |

| Ключевой стабилизатор напряжения постоян-НОгО TOKA | 1978 |

|

SU845146A1 |

| Стабилизированный преобразователь постоянного напряжения в постоянное с защитой | 1983 |

|

SU1089733A1 |

Изобретение относится к стабилизированным источникам питания с импульсным регулированием. Цель - повьшение КПД, надежности путем увеличения точности срабатывания защиты и получение понргаенного выходного напряжения, С этой целью блок защиты 15 вьтолнен на транзисторном инверторе 17, выходном транзисторе 28, интегрирующих цепях-21, 22, резисторе 27 и диоде 29. При увеличении нагрузки время запертого состояния транзистора 16- увеличивается, что приводит к увеличению напряжения на конденсаторе 25. При увеличении тока нагрузки сверх номинального выходной транзистор 28 открывается, что приводит к запиранию транзистора 8. Та;ким образом происходит лавинообразное увеличение длительности ширины импульса на выходе 6 ШИМ 1, на- сьпцение выходного транзистора 28 блока защиты 15 и полное выключение стабилизатора за счет осуществления в схеме положительной обратной связи. 4 ил. i (Г С 1C ел 4;ii 4

Лг

Составитель С.Горбачева Редактор НоЕгорова Техред А.Кравчук

Заказ 3108/43 Тираж 863Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор М.Демчик

| Стабилизатор постоянного напряжения с токовой самозащитой | 1975 |

|

SU584300A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Стабилизатор напряжения с самозащитой | 1982 |

|

SU1046751A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-07-23—Публикация

1985-12-30—Подача