. 1328940 .Изобретение относится к радиотехнике и связи и может быть использовано в радиовещательной приемной стереофонической аппаратуре с полярной модуляцией.

Цель изобретения - повышение качества воспроизводимых сигналов.

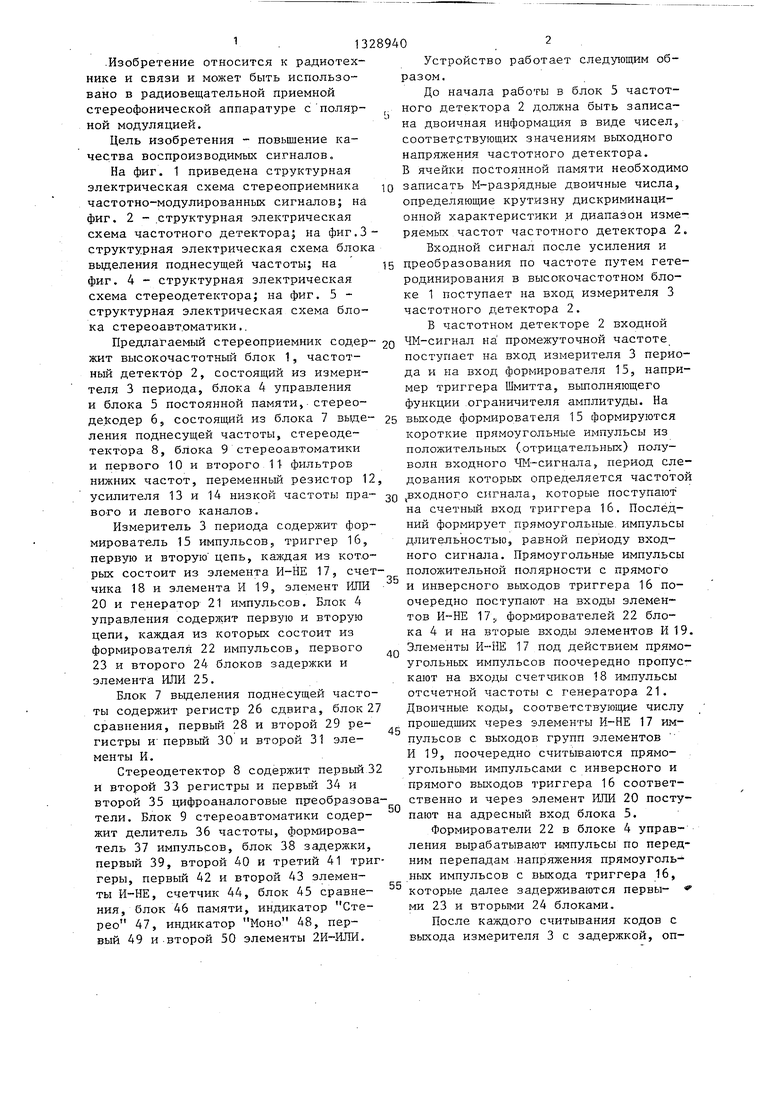

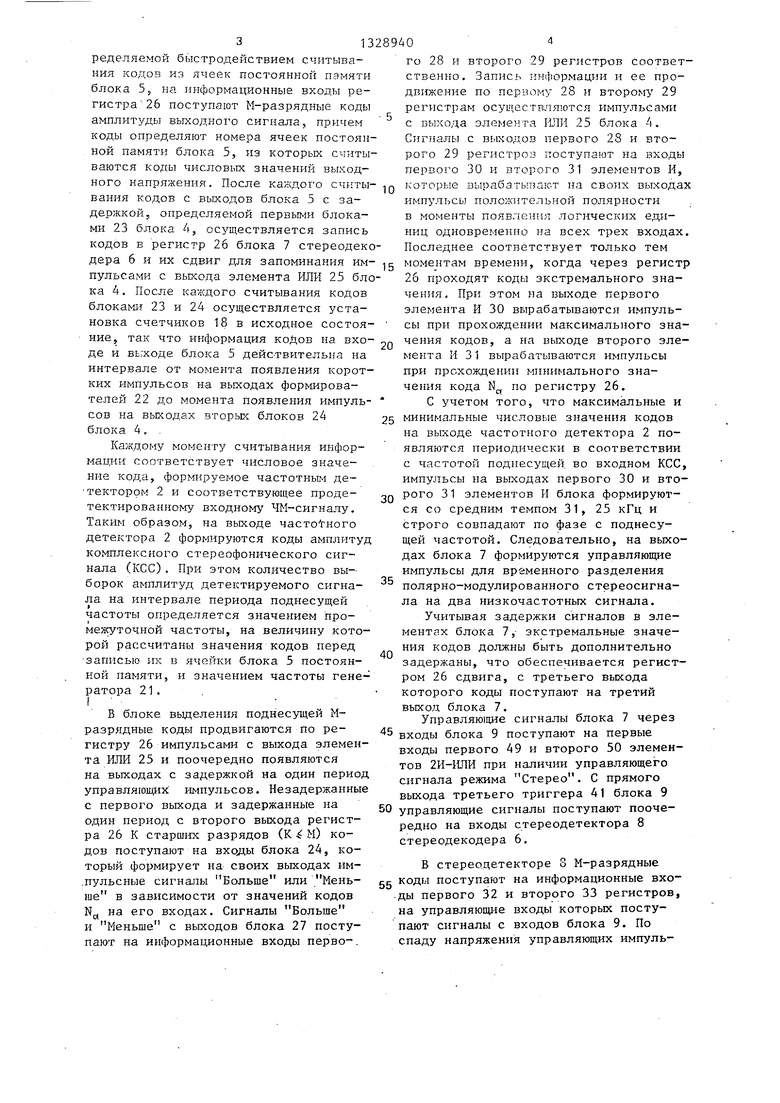

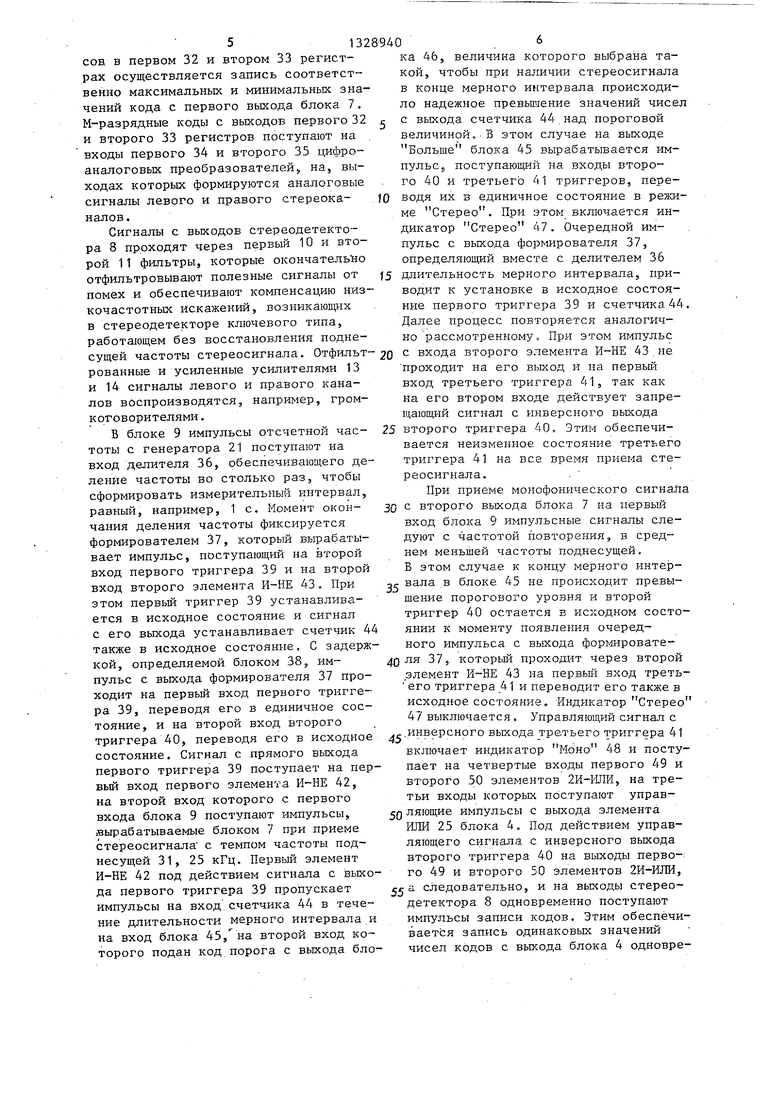

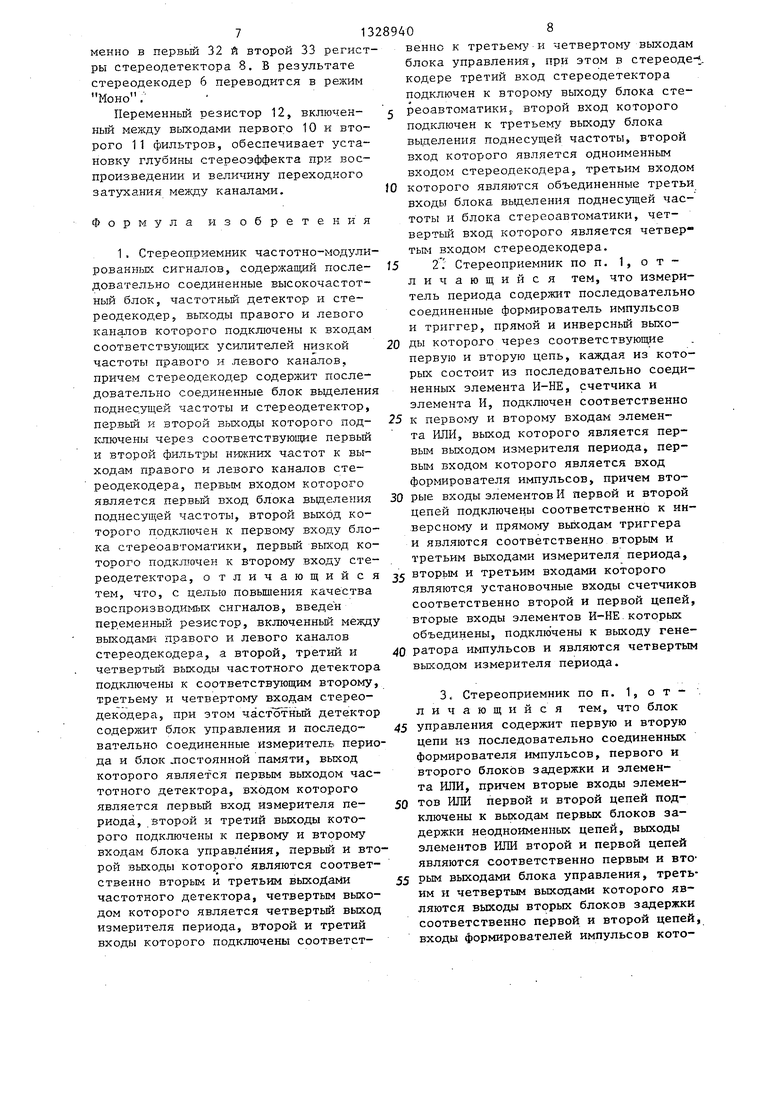

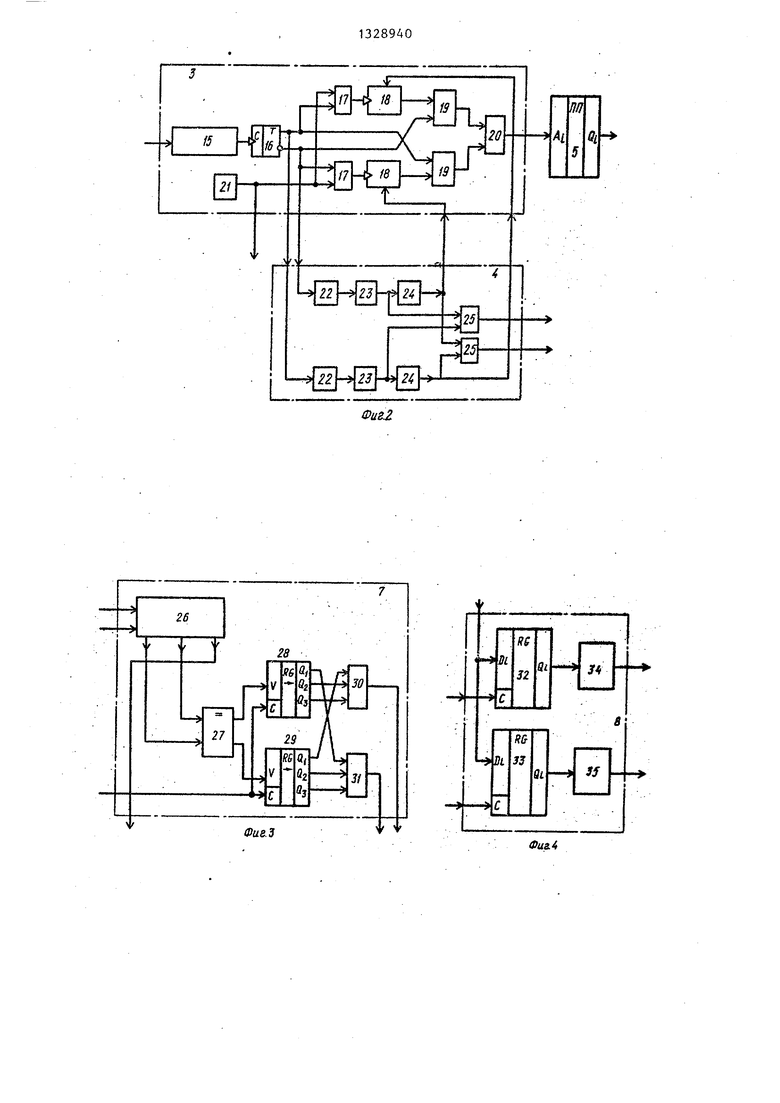

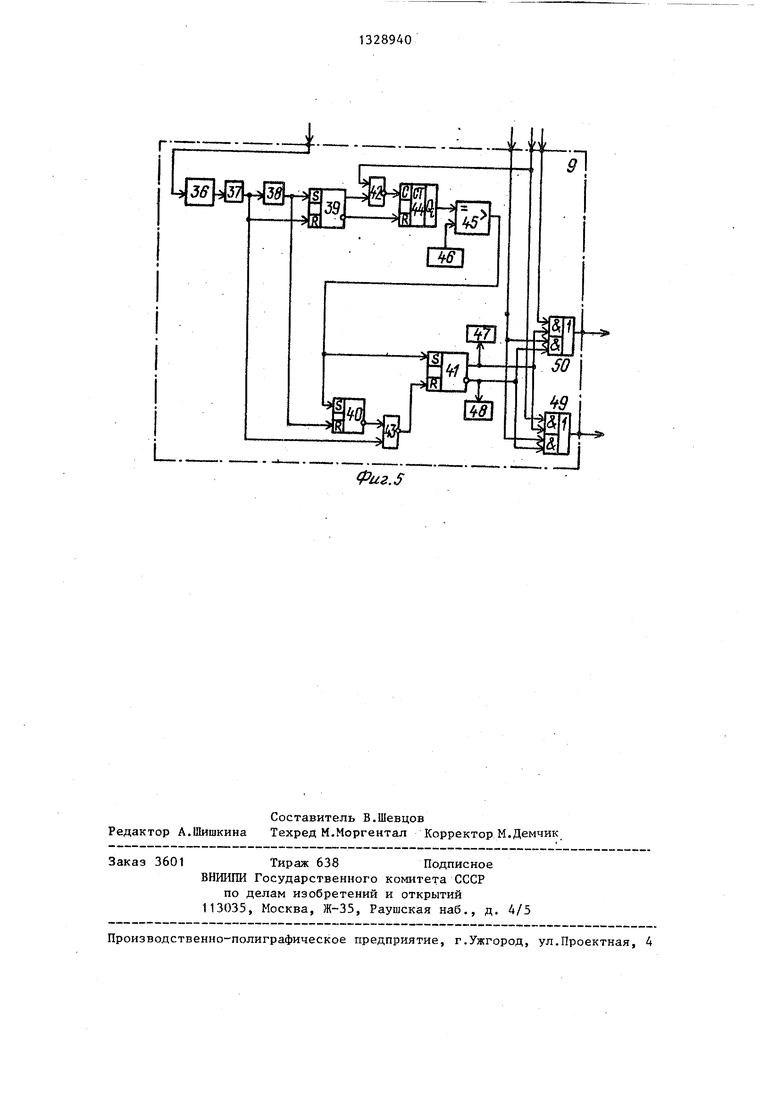

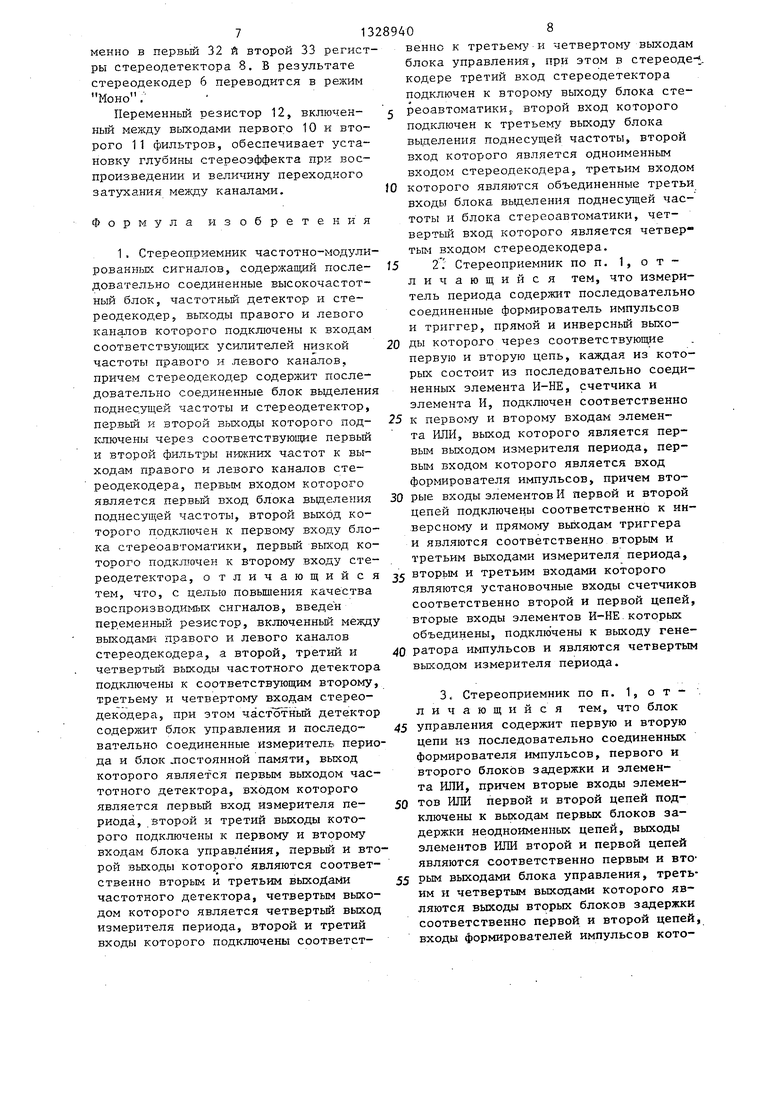

На фиг. 1 приведена структурная электрическая схема стереоприемника частотно-модулированных сигналов; на фиг. 2 - .структурная электрическая схема частотного детектора; на фиг.З структурная электрическая схема блок выделения поднесущей частоты; на фиг. 4 - структурная электрическая схема стереодетектора; на фиг, 5 - структурная электрическая схема блока стереоавт.оматики,.

Предлагаемый стереоприемник содер- 20 ЧМ-сигнал ка промежуточной частоте

жит высокочастотный блок 1, частотный детектор 2, состоящий из измерителя 3 периода, блока 4 управления и блока 5 постоянной памяти, стереодекодер 6, состоящий из блока 7 выде- 25 выходе формирователя 15 формируются

ления поднесущей частоты, стереодетектора 8, блока 9 стереоавтоматики и первого 10 и второго 11 фильтров нижних частот, переменньш резистор 12,

короткие прямоугольные импульсы из положительных (отрицательных) полуволн входного ЧМ-сигнала, период следования которых определяется частотой усилителя 13 и 14 низкой частоты пра- gg входного сигнала, которые поступают во.го и левого каналов.на счетный вход триггера 16. Последний формирует прямоугольные, импульсы длительностью, равной периоду входного сигнала. Прямоугольные импульсы

Измеритель 3 периода содержит формирователь 15 импульсов, триггер 16, первую и вторую цепь, калсдая из кот.о- рых состоит из элемента И-НЕ 17, счетчика 18 и элемента И 19, элемент ИЛИ 20 и генератор 21 импульсов. Блок 4 управления содерлсит первую и вторую цепи, каждая из которых состоит из формирователя 22 импульсов, первого 23 и второго 24 блоков задержки и элемента ИЛИ 25.

Блок 7 выделения поднесущей частоты содержит регистр 26 сдвига, блок 27 сравнения, первьй 28 и второй 29 регистры И первый 30 и второй 31 элементы И.

Стереодетектор 8 содержит первый 32 и второй 33 регистры и первый 34 и второй 35 цифроаналоговые преобразователи. Блок 9 стереоавтоматики содержит делитель 36 частоты, формирователь 37 импульсов, блок 38 задержки, первый 39, второй 40 и третий 41 триг геры, первый 42 и второй 43 элементы И-НЕ, счетчик 44, блок 45 сравнения, блок 46 памяти, индикатор Стерео 47, индикатор Моно 48, первый 49 и .второй 50 элементы 2И-ИЛИ.

35

40

45

50

55

положительной полярности с прямого и инверсного выходов триггера 16 поочередно поступают на входы элементов 17., формирователей 22 блока 4 и на вторые входы элементов И 19. Элементы И--НЕ 17 под действием прямоугольных импульсов поочередно пропускают на входы счетчиков 18 импульсы отсчетной частоты с генератора 21. Двоичные коды, соответствующие числу прошедших через элементы И-НЕ 17 импульсов с выходов групп элементов И 19, поочередно считываются прямо- угольными импульсами с инверсного и прямого вькодов триггера 16 соответственно и через элемент ИЛИ 20 поступают на адресный вход блока 5.

Формирователи 22 в блоке 4 управления вырабатывают импульсы по передним перепа,цам напряжения прямоуголь-- ных импульсов с выхода триггера 16, которые далее задерживаются первы- ми 23 и вторыми 24 блоками.

После каждого считывания кодов с выхода измерителя 3 с задержкой, оп

Устройство работает следующим образом.

До начала работы в блок 5 частотного детектора 2 быть записа-

на двоичная информация в виде чисеЛз

соответствующих значениям выходного

напряжения частотного детектора.

В ячейки постоянной памяти необходимо

записать М-разрядные двоичные числа, определяющие крутизну дискриминационной характеристики и диапазон измеряемых частот частотного детектора 2, Входной сигнал после усиления и

преобразования по частоте путем гете- родинирования в высокочастотном блоке 1 Поступает на вход измерителя 3 частотного детектора 2.

В частотном детекторе 2 входной

поступает на вход измерителя 3 периода и на вход формирователя 15, например триггера Шмитта, выполняющего функции .ограничителя амплитуды. На

5

0

5

0

5

положительной полярности с прямого и инверсного выходов триггера 16 поочередно поступают на входы элементов 17., формирователей 22 блока 4 и на вторые входы элементов И 19. Элементы И--НЕ 17 под действием прямоугольных импульсов поочередно пропускают на входы счетчиков 18 импульсы отсчетной частоты с генератора 21. Двоичные коды, соответствующие числу прошедших через элементы И-НЕ 17 импульсов с выходов групп элементов И 19, поочередно считываются прямо- угольными импульсами с инверсного и прямого вькодов триггера 16 соответственно и через элемент ИЛИ 20 поступают на адресный вход блока 5.

Формирователи 22 в блоке 4 управления вырабатывают импульсы по передним перепа,цам напряжения прямоуголь-- ных импульсов с выхода триггера 16, которые далее задерживаются первы- ми 23 и вторыми 24 блоками.

После каждого считывания кодов с выхода измерителя 3 с задержкой, определяемой быстродействием считывания кодов из ячеек постоянной памяти блока 55 на информационные входы регистра 26 поступают М-разрядные коды амплитуды выходного сигнала, причем коды определяют номера ячеек постоянной памяти блока 5, из которых считываются коды числовых значений выходного напряжения. После каждого считывания кодов с выходов блока 5 с задержкой, определяемой первыми блоками 23 блока АЗ осуществляется запись кодов в регистр 26 блока 7 стереодекодера 6 и их сдвиг для запоминания им- g моментам времени, когда через регистр пульсами с выхода элемента ИЛИ 25 бло- 26 проходят коды экстремального знака 4. После каждого считывания кодов блоками 23 и 24 осуществляется установка счетчиков 18 в исходное состоячения. При этом на выходе первого элемента И 30 вырабатываются импульсы при прохождении максимального значения кодов, а на выходе второго элемента И 31 вырабатываются импульсы при прохождении минимального значения кода N по регистру 26.

ние, так что информация коДов на входе и выходе блока 5 дейс-твителыга на интервале от момента появления коротких импульсов на выходах фop fflpoвa- телей 22 до момента появления импульсов на выходах вторых блоков 24 блока 4. .

Каждому моменту считывания информации соответствует числовое значение кода, формируемое частотным де тектором 2 и соответствующее проде- тектированному входному ЧМ-сигналу. Таким образом, на выходе часто гного детектора 2 формируются коды амплитуд комплексного стереофонического сигнала (КСС). При этом количество вы-- борок амплитуд детектируемого сигнала на интервале периода поднесущей частоты определяется значением про- мезкуточной частоты, на величину которой рассчитаны значения кодов перед записью их в ячейки блока 5 постоянной памяти, и значением частоты генератора 21 .. I

В блоке вьщеления поднесущей Мразрядные коды продвигаются по регистру 26 импульсами с выхода элемента ИЛИ 25 и поочередно появляются на выходах с задержкой на один период управляющих: импульсов. Незадержанные с первого выхода и задержанные на один период с второго выхода регистра 26 К старших разрядов (К М) кодов поступают на входы блока 24, который формирует на своих выходах им20

30

чения. При этом на выходе первого элемента И 30 вырабатываются импульсы при прохождении максимального значения кодов, а на выходе второго элемента И 31 вырабатываются импульсы при прохождении минимального значения кода N по регистру 26.

С учетом того, что максимальные и 25 минимальные ЧИСЛОВЕ Ш значения кодов на выходе частотного детектора 2 появляются периодически в соответствии с частотой поднесущей во входном КСС, импульсы на выходах первого 30 и второго 31 элементов И блока формируются со средним темпом 31, 25 кГц и строго совпадают по фазе с поднесущей частотой. Следовательно, на выходах блока 7 формируются управляющие импульсы для временного разделения полярно-модулированного стереосигнала на два низкочастотных сигнала.

Учитывая задержки сигналов в элементах блока 7,- экстремальные значения кодов должны быть дополнительно задержаны, что обеспечивается регистром 26 сдвига, с третьего выхода которого коды поступают на третий

выход блока 7.

Управляюгцие сигналы блока 7 через

5 входы блока 9 поступают на первые входы первого 49 и второго 50 элементов 2И-ИЛИ при наличии управляющего сигнала режима Стерео. С прямого выхода третьего триггера 41 блока 9

50 управляющие сигналы поступают поочередно на входы стереодетектора 8 стереодекодера 6.

В стереодетекторе 8 М-разрядные

35

40

.пульсные сигналы Больше или Мень-gg коды поступают на информационные вхо- ше в зависимости от значений кодов ды первого 32 и второго 33 регистров, Nj., на его входах. Сигналы Больше на управляющие входы которых посту- и Меньше с выходов блока 27 посту- пают сигналы с входов блока 9. По пают на информационные входы перво-. спаду напряжения управляющих импуль

го 28 и второго 29 регистров соответственно. Запись информации и ее продвижение по первому 28 и второму 29 регистрам осуществляются импульсами с выхода элемента I-DTH 25 блока 4. Сигналы с вЕ)1Ходов первого 28 и второго 29 регистров поступают на входы первого 30 и второго 31 элементов И, которые вырабатьпзают на своих выходах импульсы положительной полярности в моменты появления логических единиц одновременно на всех трех входах. Последнее соответствует только тем

g моментам времени, когда через регист 26 проходят коды экстремального зна20

30

чения. При этом на выходе первого элемента И 30 вырабатываются импульсы при прохождении максимального значения кодов, а на выходе второго элемента И 31 вырабатываются импульсы при прохождении минимального значения кода N по регистру 26.

С учетом того, что максимальные и 25 минимальные ЧИСЛОВЕ Ш значения кодов на выходе частотного детектора 2 появляются периодически в соответствии с частотой поднесущей во входном КСС импульсы на выходах первого 30 и второго 31 элементов И блока формируются со средним темпом 31, 25 кГц и строго совпадают по фазе с поднесущей частотой. Следовательно, на выходах блока 7 формируются управляющие импульсы для временного разделения полярно-модулированного стереосигнала на два низкочастотных сигнала.

Учитывая задержки сигналов в элементах блока 7,- экстремальные значения кодов должны быть дополнительно задержаны, что обеспечивается регистром 26 сдвига, с третьего выхода которого коды поступают на третий

выход блока 7.

Управляюгцие сигналы блока 7 через

5 входы блока 9 поступают на первые входы первого 49 и второго 50 элементов 2И-ИЛИ при наличии управляющего сигнала режима Стерео. С прямого выхода третьего триггера 41 блока 9

50 управляющие сигналы поступают поочередно на входы стереодетектора 8 стереодекодера 6.

В стереодетекторе 8 М-разрядные

35

40

сов в первом 32 и втором 33 регистрах осуществляется запись соответственно максимальных и минимальных значений кода с первого выхода блока 7. М-разрядные коды с выходов первого 32 и второго 33 регистров поступают на . входы первого 34 и второго 35 цифро- аналоговых преобразователей., на, выходах которых формируются аналоговые сигналы левого и правого стереоканалов.

Сигналы с выходов стереодетекто- ра 8 проходят через первый 10 и второй 11 фильтры, которые окончательно отфильтровывают полезные сигналы от помех и обеспечивают компенсацию низкочастотных искажений, возникающих в стереодетекторе ключевого типа, работающем без восстановления подне25

30

сущей частоты стереосигнала. Отфильт-20 входа второго элемента И-НЕ 43.не рованные и усиленные усилителями 13 и 14 сигналы левого и правого каналов воспроизводятся, например, громкоговорителями.

В блоке 9 импульсы отсчетной частоты с генератора 21 поступают на вход делителя 36, обеспечивающего деление частоты во столько раз, чтобы сформировать измерительный интервал, равный, например, 1 с. Момент окончания деления частоты фиксируется формирователем 37, который вырабатывает импульс, поступающий на второй вход первого триггера 39 и на второй вход второго элемента И-НЕ 43. При этом первый триггер 39 устанавливается в исходное состояние и сигнал с его выхода устанавливает счетчик 44 также в исходное состояние. С задержкой, определяемой блоком 38, импульс с выхода формирователя 37 проходит на первый вход первого триггера 39, переводя его в единичное соспроходит на его выход и на первьш вход третьего триггера 41, так как на его втором входе действует запрещающий сигнал с инверсного выхода второго триггера 40, Этим обеспечивается неизменное состояние третьего триггера 41 на все время приема стереосигнала. .

При приеме монофонического сигнал с второго выхода блока 7 на первьш вход блока 9 импульсные сигналы следуют с частотой повторения, в среднем меньшей частоты поднесущей. Б этом случае к концу мерного интерэг вала ,в блоке 45 не происходит превышение порогового уровня и второй триггер 40 остается в исходном состо янии к моменту появления очередного импульса с выхода формировате40 ля 37, который проходит через второй элемент И-НЕ 43 на первый вход треть его триггера 41 и переводит его также в исходное состояние. Индикатор Стерео 47 выключается. Управляющий сигнал с

тояние, и на второй вход второго триггера 40, переводя его в исходное состояние. Сигнал с прямого выхода первого триггера 39 поступает на первый вход первого элемента 42, на второй вход которого с первого входа блока 9 поступают импульсы, вырабатываемые блоком 7 при приеме стереосигнала с темпом частоты под несущей 31, 25 кГц. Первый элемент И-НЕ 42 под действием сигнала с выхо- да первого триггера 39 пропускает импульсы на вход,счетчика 44 в течение длительности мерного интервала и на вход блока 45,на второй вход которого подан код порога с выхода блока 46, величина которого выбрана такой, чтобы при наличии стереосигнала в конце мерного интервала происходило надежное превышение значений чисел

с выхода счетчика 44,над пороговой величиной. В этом случае на выходе Больше блока 45 вырабатывается импульс, поступающий на входы второго 40 и третьего 41 триггеров, переводя их в единичное состояние в режиме Стерео. При этом включается индикатор Стерео 47. Очередной импульс с выхода формирователя 37, определяющий вместе с делителем 36

длительность мерного интервала, приводит к установке в исходное состояние первого триггера 39 и счетчика 44. Далее процесс повторяется аналогично рассмотренному. При этом импульс

входа второго элемента И-НЕ 43.не

проходит на его выход и на первьш вход третьего триггера 41, так как на его втором входе действует запрещающий сигнал с инверсного выхода второго триггера 40, Этим обеспечивается неизменное состояние третьего триггера 41 на все время приема стереосигнала. .

При приеме монофонического сигнала с второго выхода блока 7 на первьш вход блока 9 импульсные сигналы следуют с частотой повторения, в среднем меньшей частоты поднесущей. Б этом случае к концу мерного интервала ,в блоке 45 не происходит превышение порогового уровня и второй триггер 40 остается в исходном состоянии к моменту появления очередного импульса с выхода формирователя 37, который проходит через второй элемент И-НЕ 43 на первый вход треть- его триггера 41 и переводит его также в исходное состояние. Индикатор Стерео 47 выключается. Управляющий сигнал с

инверсного выхода третьего триггера 41 включает индикатор Моно 48 и поступает на четвертые входы первого 49 и второго 50 элементов 2И-ИЛИ, на третьи входы которых пбступают управляющие импульсы с выхода элемента ИЛИ 25 блока 4. Под действием управляющего сигнала с инверсного выхода второго триггера 40 на выходы перво- го 49 и второго 50 элементов 2И-ИЛИ,

а следовательно, и на выходы стерео- детектора 8 одновременно поступают импульсы записи кодов. Этим обеспечивается запись одинаковых значений чисел кодов с выхода блока 4 одновременно в первый 32 и второй 33 регистры сте.реодетектора 8. В результате стереодекодер 6 переводится в режим Моно .

Переменный резистор 12, включенный между выходами первого 10 и второго 11 фильтров, обеспечивает установку глубины стереоэффекта при воспроизведении и величину переходного затухания между каналами.

Формула изобретения

1. Стереоприемник частотно-модули рованнг:.1Х сигналов, содержащий последовательно соединенные высокочастотный блок, частотньй детектор и стереодекодер, вькоды правого и левого каналов которого подключены к входам соответствующш : уси.пителей низкой частоты правого и левого каналов, причем стереодекодер содержит последовательно соединенные блок вьщеления поднесущей частоты и стереодетектор, первый и второй выходы которого подключены через соответствующие первый и второй фильтры нижних частот к выходам правого и левого каналов сте- реодекодера, первым входом которого является первый вход блока выделения поднесущей частоты, второй выход которого подключен к первому входу блока стереоавтоматики, первый выход которого подключен к второму входу стереодетектора, отличающийся 35 вторьм и третьим входами которого

тем, что, с целью повыатения качества воспроизводимых сигналов, введен переменный резистор, включенный между выходами правого и левого каналов стереодекодера, а второй, третий и четвертый выходы частотного детектора подключены к соответствующим второму, третьему и четвертому входам стерео- декодера, при этом част отный детектор содержит блок управления и последовательно соединенные измеритель периода и блок лостоянной памяти, выход которого является первым выходом частотного детектора, входом которого является первый вход измерителя периода, второй и третий выходы которого подключены к первому и второму входам блока управления, первый и второй выходы которого являются соответственно вторым и третьим выходами частотного детектора, четвертым выходом которого является четвертый выход измерителя периода, второй и третий входы которого подключены соответственно к третьем и четвертому выходам блока управления, при этом в стереоде-, кодере третий вход стереодетектора подключен к второму выходу блока стереоавтоматики второй вход которого подключен к третьему выходу блока выделения поднесуодей частоты, второй вход которого является одноименным входом стереодекодера, третьим входом

которого являются объединенные третьи входы блока выделения поднесущей частоты и блока стереоавтоматики, четвертый вход которого является четвер тым входом стереодекодера.

2. Стереоприемник по п. 1, о т - ли чающийся тем, что измеритель периода содержит последовательно соединенные формирователь импульсов и триггер, прямой и инверсный выхоДЫ которого через соответствующие

первую и вторую цепь, каждая из которых состоит из последовательно соединенных элемента И-НЕ, счетчика и элемента И, подключен соответственно

к первому и второму входам элемента ИЛИ, выход которого является первым выходом измерителя периода, первым входом которого является вход формирователя импульсов, причем вторые входы элементов И первой и второй цепей подключены соответственно к инверсному и прямому выходам триггера и являются соответственно вторым и третьим выходами измерителя периода.

являютс.я установочные входы счетчиков соответственно второй и первой цепей, вторые входы элементов И-НЕ которых объединены, подключены к выходу гене- 40 ратора импульсов и являются четвертым выходом измерителя периода.

3. Стереоприемник по п. 1, о т - . л и ч а ю щ и и с я тем, что блок

45 управления содержит первую и вторую цепи из последовательно соединенных формирователя импульсов, первого и второго блоков задержки и элемента ИЛИ, причем вторые входы элемен50 тов ИЛИ первой и второй цепей подключены к выходам первых блоков задержки неодноименных цепей, выходы элементов ИЛИ второй и первой цепей являются соответственно первым и вто55 рым выходами блока управления, третьим и четвертым выходами которого являются выходы вторых блоков задержки соответственно первой и второй цепей, входы формирователей импульсов которых являются соответственно первым и вторым входами блока управления.

4. Стереоприемник по п. 1, о т л и- чающийс я тем, что блок вьще- ления поднесущей частоты содержит ре- гистр сдвига и блок сравнения, первый и второй выходы которого подключены к информационным входам соответственно первого и второго регистров, выходы первых разрядов которых подклю- Ш триггер, второй элемента И-НЕ, третий

чены к первым входам соответствующих йторого и первого элементов И, второй и третий входы которых подключены к выходам второго и третьего разрядов соответствующих второго и перво- го регистров, первый и второй входы блока сравнения подключены к первому и второму выходам регистра сдвига, третий выход которого является первым выходом блока вьщеления поднесу- щей частоты, первым и вторым входами которого являются первый и второй входы регистра сдвига, при этом синхронизирующие входы первого и второго регистров объединены и являются третьим входом блока выделения поднесущей частоты, вторым и третьим выходами .которого являются выходы соответственно второго и первого элементов И..

5. Стереоприемник по п. 1, отличающийся тем, что стерео- детектор содержит первый и второй регистры, выходы которых подключены

к входам первого и второго цифроана- .,, которых попарно объединены и подклюлоговых преобразователей, выходы которых являются соответственно первым и вторым выходами стереодетектора, первым входом которого являются объечены соответственно к прямому и инверсному выходам третьего триггера, объединенные четвертые входы первого и второго элементов 2И-ИЛИ являются

диненные информационные входы первого Q третьим входом блока стереоавтоматии второго регистров, синхронизирующие входы которых являются соответственно

вторым и третьим выходами стереоде- тектора.

6. Стереоприемник по п. 1, о т - личающийс я тем, что блок стереоавтоматики содержит последовательно сЬединенные делитель частоты, формирователь ,импульсов, блок задержки и первый триггер, первый элемент И-НЕ, счетчик, блок сравнения, второй

триггер, прямой и инверсный выходы которого подключены к входам индикаторов Стерео и Моно соответственно, а также первьй и второй элементы 2И-ЮТИ и блок памяти, выход которого подключен к второму входу блока сравнения, выход которого подключен к другому входу третьего триггера, при этом выход формирователя импульсов подключен к объединенным вторым входам второго элемента И-НЕ и первого триггера, первый вход которого единен с вторым входом второго триггера, инверсный вьЕ{од первого триггера подключен к установочному входу счетчика, обт единенный с вторым входом первого элемента И-НЕ первый вход первого элемента 2И-ИЛИ и первый вход второго элемента 2И-ИЛИ являются соответственно первым и вторым входами блока стереоавтоматики, первым и вторым выходами которого являются выходы соотйетственно первого и второго элементов 2И-ИПИ, вторые и третьи вхоДы

чены соответственно к прямому и инверсному выходам третьего триггера, объединенные четвертые входы первого и второго элементов 2И-ИЛИ являются

ки, четвертым входом которого является вход делителя частоты.

Фиг.З

W

32

Qi

34

к&

3S

Qi

Фиг.4

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Стереоприемник частотно-модулированных сигналов | 1988 |

|

SU1578823A2 |

| Стереоприемник частотно-модулированных сигналов | 1988 |

|

SU1571783A2 |

| Стереоприемник частотно-модулированных сигналов | 1988 |

|

SU1596471A2 |

| Стереоприемник частотно-модулированных сигналов | 1988 |

|

SU1571782A2 |

| Стереоприемник частотно-модулированных сигналов | 1988 |

|

SU1570011A2 |

| Стереодекодер | 1984 |

|

SU1166327A1 |

| Стереодекодер | 1985 |

|

SU1241503A1 |

| Устройство для измерения коэффициента гармоник генераторов стереофонических частотно-модулированных сигналов | 1983 |

|

SU1101753A1 |

| СПОСОБ ПЕРЕДАЧИ ДОПОЛНИТЕЛЬНОЙ ИНФОРМАЦИИ В СИСТЕМЕ УКВ-ВЕЩАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2030835C1 |

| Стереодекодер | 1979 |

|

SU832748A1 |

Изобретение относится к радиотехнике и связи. Цель изобретения - повышение качества воспроизводимых сигналов. Стереоприемник содержит высокочастотный блок 1, частотный детектор 2, состоящий из измерителя 3 периода, блока управления 4 и блока иг.1 постоянной памяти 5, стереодекодер 6, состоящий из блока вьщеления поднесу- щей частоты (БВПЧ) 7, стереодетекто- ра 8, блока стереоавтоматики (БОА) 9 и фильтров 10 и 11 нижних частот, а также переменньй резистор 12 и усилители 13 и 14 низкой частоты правого и левого каналов. Цель достигается выполнением частотного детектора 2, на выходе которого формируются коды амплитуд комплексного стереофонического сигнала, и введением переменного резистора 12, обеспечивающего установку глубины стереоэффекта при воспроизведении и величину переходного затухания между каналами, Стереоприемник по пп. 2-6 ф-лы.отличается выполнением измерителя 3, блока управ- шения 4, БВПЧ 7, стереодетектора 8 и БОА 9. 5 з.п. ф-лы, 5 ил. а S (Л

Авторы

Даты

1987-08-07—Публикация

1986-01-21—Подача