Изобретение относится к преобразовательной технике и может быть использовано при проектировании централизованных источников вторичного электропитания, используемых в системах электропривода переменного то.ка с улучшенными массогабаритными показателями.

Цель изобретения - улучшение мас-- согабаритных показателей и расширение функциональных возможностей,преобразователя.

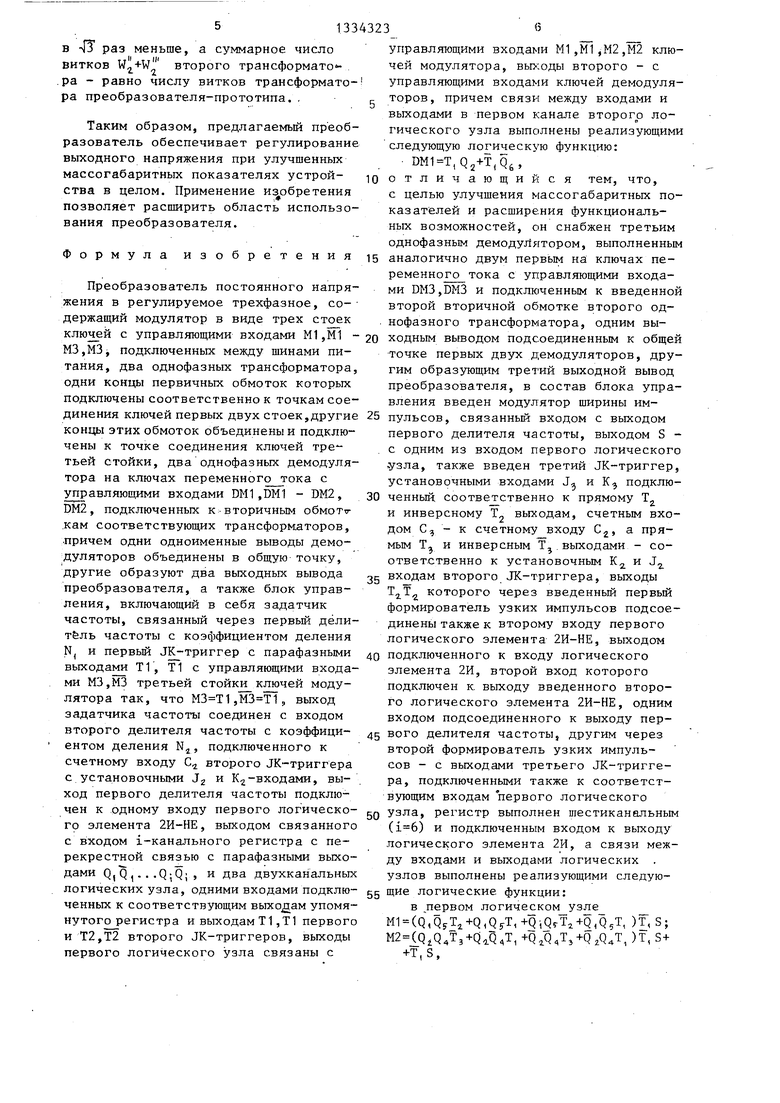

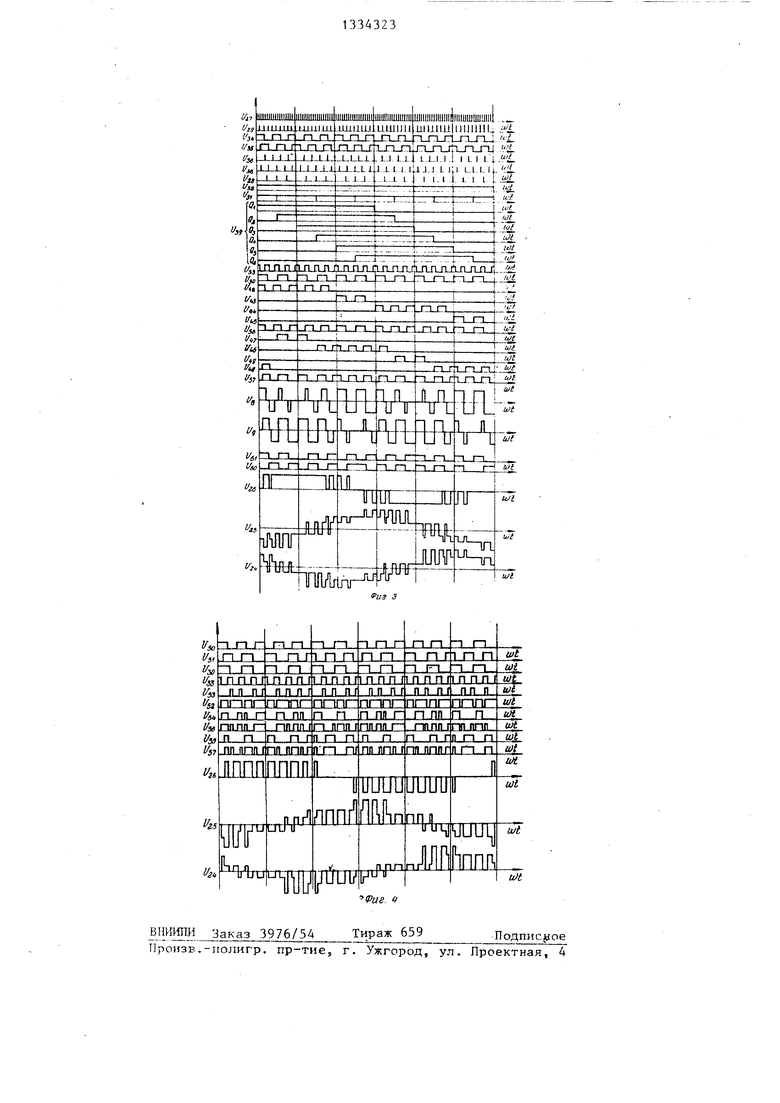

На фиг.1 приведена схема силовой части преобразователя; на фиг.2 - принципиальная схема блока управления преобразователем; на фиг.З и 4 - временные диаграммы, поясняющие принцип работы и формирования выходного Напряжения преобразователя при угле регулирования об 0 об соответственно.

Трехфазный преобразователь содержит модзшятор 1J выполненный в виде трех стоек ключей 2 - 7 (с управляющими входами Ml, М1 - МЗ, МЗ), «клю- ченных между шинами питания преобразователя. Точки соединения ключей 2-7 подключены к концам первичных обмоток 8 и 9 соответствующих трансформаторов 10 и 11. Три однофазных демодулятора 12 - 14 на ключах 15-20 переменноготока с управляющими входами DM1 , DM1 DM3, ШЗ подключены к вторичньэ.1 обмоткам 21-23 соответ36 узких импульсов подсоединены к второму входу первого логического элемента 2Н-НЕ 32, выходом подключен, ного к входу логического элемента 2И 37, второй вход которого подключен к выходу логического элемента 2И-НЕ 31. Второй вход логического элемента 2И-НЕ 31 подсоединен к вы10 ходу второго формирователя 38 узких импульсов, связанного с выходами третьего JK-триггера 35. Выход логического элемента 2И 37 соединен с входами шестиканал ьного регистра 39,

15 установочными входами .1 второго JK-триггера 34 и-К первого JK-триггера 30. Выходы регистра 39 МШИ 33, а также трех JK-триггеров 30,34 и 35 подсоединены к входам двухканаль20 ных логических узлов 40 и 41. Канал- логического узла 40 выполнен в виде четырех логических элементов ЗИ 42 - 45 (46 - 49), на выходах которых реализуются, следующие логические функ25 ции:

ЗИ 42 - Q,QfTa (ЗИ 46 - );

ЗИ 43 - Q,Qj.T4 (ЗИ 47 - ,), ЗИ 44 - QiQjTa (ЗИ 48 - QiQ4T,), ЗИ 45 - , (ЗИ 49 - .T,). 30 Выходы логических элементов ЗИ со- единены с входами логического элемента 4ИЛИ 50 (51), на выходе которого реализуются логические функции:

4ИЛИ50- Q,,QyT,+0,Q,,Q,T, ;,

ствующих трансформаторов 10 и 11. Три 35 (4ИЛИ 51 - Д +Q,Q4T,+Q ДТ,+QiQ,). вывода демодуляторов 12 - 14 объеди- й ены в одну точку, общая средняя точка вторичных обмоток 21-23 трансформаторов 10 и 11 и оставшиеся выводы 24-26 образуют три выходных вывода 40

ды логического элеме;нта 4ИЛИ 50 (51) соединены с одним входом логического элемента 2И 54 (55) .,-второй вход копреооразователя.

Блок управления преобразователем содержит задатчик 27 частоты, связанный с первым 28 и вторым 29 делителями частоты. Выход первого -делителя частоты 28 подключен к счетному входу С, первого JK-триггера 30, входам двух логических элементов 2И-.НЕ 31 и 32 и модулятору 33 ширины импульсов (МШИ) . Выход второго делителя 29 часто- 50 ты подключне к счетным входам С второго 34 и третьего 35 JK-триггеров. Установочные входы J и К, третьего JK-триггера 35 подключены соответст2 } -Х2Х4 1 -ХгХ4 Э

в каждом канале логических узлов 40 имеются также логические элементы 2 И 52 и 53, выходы которых соединены с выходом S МШИ 33, а также с выходом Tj (Т,) первого JK-триггера 30. Выхоторого соединен с выходом логического 45 элемента 2И 52 таким образом, что на их выходах реализуются логические функции:

2И 54 -(Q.QrTa+Q,QrT,.T,+Q,QjT, )T,S; 2И 55 -(,T,+Q,,,T,,T, )T,S.

венно к прямому Т и инверсному 1, выходам, а его прямой Tj и инверсный Т, выходы - к установочным К и J входам второго JK-триггера 34. Выходы Т, и Tj через первьй формирователь

36 узких импульсов подсоединены к второму входу первого логического элемента 2Н-НЕ 32, выходом подключенного к входу логического элемента 2И 37, второй вход которого подключен к выходу логического элемента 2И-НЕ 31. Второй вход логического элемента 2И-НЕ 31 подсоединен к выходу второго формирователя 38 узких импульсов, связанного с выходами третьего JK-триггера 35. Выход логического элемента 2И 37 соединен с входами шестиканал ьного регистра 39,

установочными входами .1 второго JK-триггера 34 и-К первого JK-триггера 30. Выходы регистра 39 МШИ 33, а также трех JK-триггеров 30,34 и 35 подсоединены к входам двухканальных логических узлов 40 и 41. Канал- логического узла 40 выполнен в виде четырех логических элементов ЗИ 42 - 45 (46 - 49), на выходах которых реализуются, следующие логические функции:

ЗИ 42 - Q,QfTa (ЗИ 46 - );

ЗИ 43 - Q,Qj.T4 (ЗИ 47 - ,), ЗИ 44 - QiQjTa (ЗИ 48 - QiQ4T,), ЗИ 45 - , (ЗИ 49 - .T,). Выходы логических элементов ЗИ со- единены с входами логического элемента 4ИЛИ 50 (51), на выходе которого реализуются логические функции:

(4ИЛИ 51 - Д +Q,Q4T,+Q ДТ,+QiQ

ды логического элеме;нта 4ИЛИ 50 (51) соединены с одним входом логического элемента 2И 54 (55) .,-второй вход -Х2Х4 1 -ХгХ4 Э

в каждом канале логических узлов 40 имеются также логические элементы 2 И 52 и 53, выходы которых соединены с выходом S МШИ 33, а также с выходом Tj (Т,) первого JK-триггера 30. Выхо50

торого соединен с выходом логического 45 элемента 2И 52 таким образом, что на их выходах реализуются логические функции:

2И 54 -(Q.QrTa+Q,QrT,.T,+Q,QjT, )T,S; 2И 55 -(,T,+Q,,,T,,T, )T,S.

55 Логические элементы 2И 54(55) выходами соединены с входами логического элемента 2ИЛИ 56(57), вторые входы которого соединены с выходами логического элемента 2И 53. На выходе ло31334323

гического элемента 2ИЛИ 56(57) реализуется логическая функция: 2ИЛИ (Q,,Q,T,+Q, +Q,Q,T,),S; 2ИЛИ (57)(Q,Q,T3+

,+Q2Q.4T3+QzQ4T,) T,s+T,s.

Выход логического элемента 2ИЛИ 56(57) образует выход логического узла 40 М1(М2), связанньй с управляювыходов этих элементов также логически складываются при помощи логического элемента 2И 37 и поступают на счетный вход шестиканального регистра 39. С выходов регистра 39 получают прямоугольные .симметричные парафазные импульсы вида Qt - Q (фиг.З), сдвинутые относительно друг

первого делителя частоты синхронизирует работу МШИ 33. Длительность oi сигнала S (Uj, фиг.З и 4) пропорциональна величине управляющего сигнала U

щим входом Ml ключа 6 модулятора, и д ДРУга на угол /6. Сигнал Ujg с выхода подключен к входу логического элемента НЕ,58(59), выход которого образует инверсный выход Ml (М2) канала логического узла 40, связанньй с управляющим входом Ml (М2) ключа 7(9) модулятора. Каждьм канал двухканального логического узла 41 включает логические элементы 2И-2ИЛИ 60(61), входы которых подключены к соответствующим входам регистра 39 и выходам Т,, Т, первого JK-триггера 30 так, что на выходе реализуются логические функции:2И-2ИЛИ 60 - ., ,Qg; 2И-2ИЛИ 61 - ,Qj+T,Q,.

Выход логического элемента 2И-2ИЛИ 60(61) образует выход логического (элемента) узла 41 pM1(DM2), связанный с управляющим выходом DM1(DM2 DM3) ключа 20(18,16) демодулятора, и подключен к входу логического элемента НЕ 62(63), выход которого образует инверсньй выход DM1() канала логического узла 41, связанньй с управляющим входом DM1(DM2 DM3) ключа 19(17,15) демодулятора.

об

15 определяющего величину выходного напряжения преобразователя. После осуществления соответствующих логических операций над полученными последовательностями импульсов на выходах ло20 гических узлов 40 и 41 получают новые последовательности управляющих импульсов, определяемые приведенными логическими выражениями. Номер каждого логического элемента 42-63 в логичес25 ких узлах 40 и 41 соответствует- индексу полученной последовательности импульсов, некоторые из которых представлены на фиг.З и 4. Сформированные последовательности импульсов , Ц.,

30 Uj7 39 Ujg поступают соответст- енно на управляющие входы М,М,,М2, М,М,, М силовых ключей 2-7 модулятора 1. В результате на обмотках трансформаторов 8 и 9 формируется пе2g ременное модулированное напряжение вида Ug,и,. После демодуляции этого напряжения в соответствии с управляющими сигналами U, U на выходе преобразователя формируется трехфазное напряжение вида tJ - в нерегулиПринцип работы преобразователя поясняется временными диаграммами, приведенными на фиг.З и 4: U - сигнал с выхода задатчика 27 частоты, синхронизирующего работу преобразо- вателя; U, U - сигналы с выходов первого 28 и второго 29 делителей частоты; и, U, сигналы с выходов первого 30, второго 34 и третьего 35 JK-триггеров. Частоты сигналов и и и равны между собой, а сами сигналы сдвинуты на угол 1Г/2 относительно друг друга. Частоты сигналов (со,) и и,(а)) связаны соотношением ц, /co,N/N+1, где N - любое целое число. Формирователи узких -36 и 38 импульсов осуществляют выделение фронтов импулксов U.j и и,5 после чего сигналы Ujg и сравниваются при помощи логических элементов 2И-НЕ 31 и 32 с сигналом U. ,, выхода первого деf- о

лителя 28 частоты. Сигналы совпадения

и,, и и„ с

выходов этих элементов также логически складываются при помощи логического элемента 2И 37 и поступают на счетный вход шестиканального регистра 39. С выходов регистра 39 получают прямоугольные .симметричные парафазные импульсы вида Qt - Q (фиг.З), сдвинутые относительно друг

ДРУга на угол /6. Сигнал Ujg с выхода

первого делителя частоты синхронизирует работу МШИ 33. Длительность oi сигнала S (Uj, фиг.З и 4) пропорциональна величине управляющего сигнала U

ДРУга на угол /6. Сигнал Ujg с выхода

об

определяющего величину выходного напряжения преобразователя. После осуществления соответствующих логических операций над полученными последовательностями импульсов на выходах логических узлов 40 и 41 получают новые последовательности управляющих импульсов, определяемые приведенными логическими выражениями. Номер каждого логического элемента 42-63 в логических узлах 40 и 41 соответствует- индексу полученной последовательности импульсов, некоторые из которых представлены на фиг.З и 4. Сформированные последовательности импульсов , Ц.,

Uj7 39 Ujg поступают соответст- енно на управляющие входы М,М,,М2, М,М,, М силовых ключей 2-7 модулятора 1. В результате на обмотках трансформаторов 8 и 9 формируется переменное модулированное напряжение вида Ug,и,. После демодуляции этого напряжения в соответствии с управляющими сигналами U, U на выходе преобразователя формируется трехфазное напряжение вида tJ - в нерегули

уемом (фиг.З) или регулируемом (фиг.4) вариантах.

Особенностью работы данного преоб-. разователя является наличие только двух напряжений вида Ug,Ug, используемых для формирования трехфазного вы- и„,. Фазовый

ходного напряжения . сдвиг между этими напряжениями составляет 90°, а соотношение между величинами этих напряжений 1/-4з . По сравнению с известным преобразователем, в состав которого входят два трансформатора, имеющих по одной вторичной обмотке, в предложенном устройстве один из трансформатоII

ров имеет две вторичные обмотки W и W , однако число витков вторичной обмотки первого трансформатора Wj

51334323 5

в 43 раз меньше, а суммарное число управляющими входами М1,М1,М2,М2 клювитков W +W второго трансформато«- .ра - равно числу витков трансформато- ра преобразователя-прототипа..

Таким образом, предлагаемьй преобразователь обеспечивает регулирование выходного напряжения при улучшенных массогабаритных показателях устройства в целом. Применение изобретения позволяет расширить область использования преобразователя.

чей модулятора, второго - с управляющими входами ключей демодуляторов, причем связи между входами и выходами в первом канале второго логического узла выполнены реализующими следующую логическую функцию: ,,,

10 отличающийся тем, что, с целью улучшения массогабаритных показателей и расширения функциональных возможностей, он снабжен третьим однофазным демодулятором, выполненным

Формула изобретения

15 аналогично двум первым на ключах пе- ременного тока с управляющими входами DM3,DM3 и подключенньпуг к введенной второй вторичной обмотке второго однофазного трансформатора, одним выПреобразователь постоянного напряжения в регулируемое трехфазное, со- держащий модулятор в виде трех стоек ключей с управляющими входами М1,М1 - 2о ходным выводом подсоединенным к общей МЗ,МЗ, подключенных между шинами пи- точке первых двух демодуляторов, дру- тания, два однофазных трансформатора, гим образующим третий выходной вывод одни концы первичных обмоток которых преобразователя, в состав блока упра- подключены соответственно к точкам сое- вления введен модулятор ширины им- динения ключей первых двух стоек,другие 25 пульсов, связанный входом с выходом концы этих обмоток объединены и подклю- первого делителя частоты, выходом S с одним из входом первого логического «узла, также введен третий JK-триггер,

чены к точке соединения ключей тьей стойки, два однофазных демодулятора на ключах переменного тока с управляющими входами DM1,DM1 - DM2, DM2 , подключенных к-вторичным обмоттг .кам соответствующих трансформаторов, причем одни одноименные выводы демодуляторов объединены в общую точку, другие образуют два выходньпс вывода преобразователя, а также блок управления, включающий в себя задатчик частоты, связанный через первый делитель частоты с коэффициентом деления N, и первьй JK-триггер с парафазными выходами Т1, Т1 с управляющими входами МЗ,МЗ третьей стойки ключей модулятора так, что , ,, выход задатчика частоты соединен с входом второго делителя частоты с коэффициентом деления N, подключенного к счетному входу С второго JK-триггера с установочными J2 и К -входами, вы- . ход первого делителя частоты подклюустановочными входа/ми J и К, подклю30 ченный соответственно к прямому Т и инверсному Т„ выходам, счетным входом С, - к счетному входу С, а прямым Т, и инверсным Т.выходами - соответственно к установочным Ку и J

32 входам второго JK-триггера, выходы T,j,T которого через введенный первый формирователь узких импульсов подсоединены также к второму входу первого логического элемента 2И-НЕ, выходом

40 подключенного к входу логического элемента 2И, второй вход которого подключен к. выходу введенного второго логического элемента 2И-НЕ, одним входом подсоединенного к выходу пер45 вого делителя частоты, другим через второй формирователь узких импульсов - с выходами третьего JK-триггера, подключенными также к соответствующим входам первого логического

чен к одному входу первого логическо-gg узла, регистр выполнен шеетиканальным го элемента 2И-НЕ, выходом связанного () и подключенным входом к выходу с входом i-канального регистра с пе- логического элемента 2И, а связи меж- рекрестной связью с парафазными выхо- ду входами и выходами логических дами Q,Q,...Q;Q;, и два двухканальных узлов выполнены реализующими следуюлогических узла, одними входами подклю-gg щие логические функции: ченных к соответствующим выходам упомя- в ,первом логическом узле нyтoгoJзeгиcтpa и выходам Т1 ,Т1 первого M1 (Q,Q5T.+Q,Q5-T,+QiQff j+QfQjT, )Т, S; и Т2,Т2 второго JK-триггеров, выходы М2 д д j+QaQJ,+РгР,Тз+д ., )Т, S + первого логического узла связаны с +1,8,

чей модулятора, второго - с управляющими входами ключей демодуляторов, причем связи между входами и выходами в первом канале второго логического узла выполнены реализующими следующую логическую функцию: ,,,

отличающийся тем, что, с целью улучшения массогабаритных показателей и расширения функциональных возможностей, он снабжен третьим однофазным демодулятором, выполненным

аналогично двум первым на ключах пе- ременного тока с управляющими входами DM3,DM3 и подключенньпуг к введенной второй вторичной обмотке второго однофазного трансформатора, одним выходным выводом подсоединенным к общей точке первых двух демодуляторов, дру- гим образующим третий выходной вывод преобразователя, в состав блока упра- вления введен модулятор ширины им- пульсов, связанный входом с выходом первого делителя частоты, выходом S установочными входа/ми J и К, подклю30 ченный соответственно к прямому Т и инверсному Т„ выходам, счетным входом С, - к счетному входу С, а прямым Т, и инверсным Т.выходами - соответственно к установочным Ку и J

32 входам второго JK-триггера, выходы T,j,T которого через введенный первый формирователь узких импульсов подсоединены также к второму входу первого логического элемента 2И-НЕ, выходом

40 подключенного к входу логического элемента 2И, второй вход которого подключен к. выходу введенного второго логического элемента 2И-НЕ, одним входом подсоединенного к выходу пер45 вого делителя частоты, другим через второй формирователь узких импульсов - с выходами третьего JK-триггера, подключенными также к соответст71334323

во втором канале второго логического узла

DM2 DM3 TQ+fQ, причем число витков каждой вторичной

8

мотки первого трансформатора, л коэ фициенты деления первого и второго делителей частоты связаны соотнотен 1

обмотки второго трансформатора в - (Nl4-1), где N1 - любое целое раз меньше числа витков вторичной обчисло.

8

мотки первого трансформатора, л коэффициенты деления первого и второго делителей частоты связаны соотнотени- 1

(Nl4-1), где N1 - любое целое

число.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь постоянного напряжения в трехфазное | 1985 |

|

SU1288870A1 |

| Устройство для управления преобразователем постоянного напряжения в регулируемое трехфазное | 1986 |

|

SU1415382A1 |

| Устройство для управления преобразователем постоянного напряжения в трехфазное квазисинусоидальное | 1985 |

|

SU1359872A1 |

| Устройство для управления трехфазным преобразователем постоянного напряжения | 1988 |

|

SU1598084A1 |

| Устройство для управления преобразователем постоянного напряжения в трехфазное | 1987 |

|

SU1504764A1 |

| Устройство для управления двухканальным трехфазным преобразователем | 1991 |

|

SU1826116A1 |

| Преобразователь постоянного напряжения в трехфазное квазисинусоидальное | 1984 |

|

SU1257791A1 |

| Устройство для управления преобразователем постоянного напряжения в постоянное | 1983 |

|

SU1144174A1 |

| Стабилизированный преобразователь напряжения | 1988 |

|

SU1614007A1 |

| Однофазный инвертор напряжения с многофазной широтно-импульсной модуляцией | 2023 |

|

RU2804997C1 |

Изобретение относится к преобразовательной технике и может быть использовано во вторичных источниках питания. Целью изобретения является улучшение массогабаритных показателей и расширение функциональных возможностей. Преобразователь выполнен в виде модулятора, к выходным вьшодам lioTo- рого подключены первичные обмотки двух однофазных трансформаторов, вторичные обмотки которых подключены к трем демодуляторам на ключах переменного тока. Первый однофазньм трансформатор имеет одну вторичную обмотку, число витков которой в -JJ раз больше числа.витков каждой из двух вторичных обмоток второго однофазного трансформатора. Система управления обеспечивает реализацию разработанно- -го алгоритма управления. Преобразователь постоянного напряжения в регулируемое трехфазное обеспечивает формирование выходного напряжения с широт- но-кмпульсно модуляцией и широтно- импульсное регулирование амплитуды основной гармоники этого напряжения. 4 ил. I (Л со со 4:: СО tsD СО

Т Г

55 Фиа i

.

Риг. г

| Преобразователь постоянного напряжения в трехфазное | 1976 |

|

SU731534A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь постоянного напряжения в трехфазное | 1985 |

|

SU1288870A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-08-30—Публикация

1986-04-18—Подача