Изобретение относится к электро- rexHtfKe, а именно к токовой защите. электродвигателей.

Цель изобретения - повьшение надежности устройства самонастраивающейся токовой защиты электродвигателей путем обеспечения независимости срабатывания защиты от скорости нарастания тока.

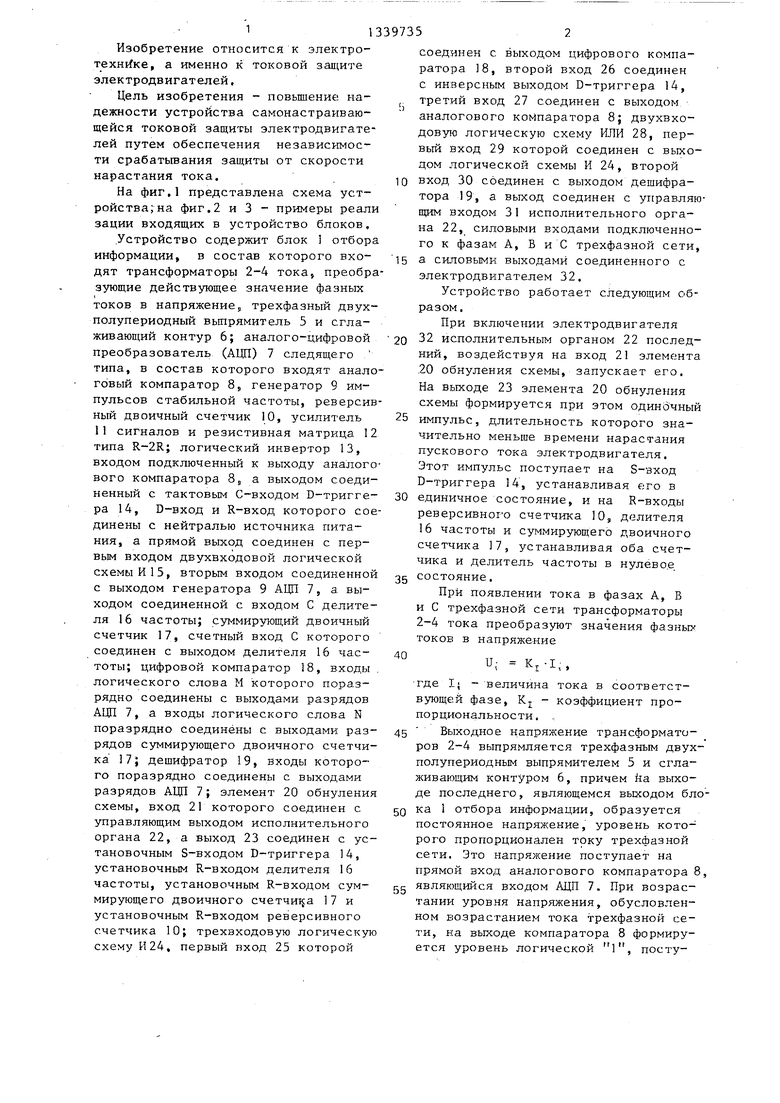

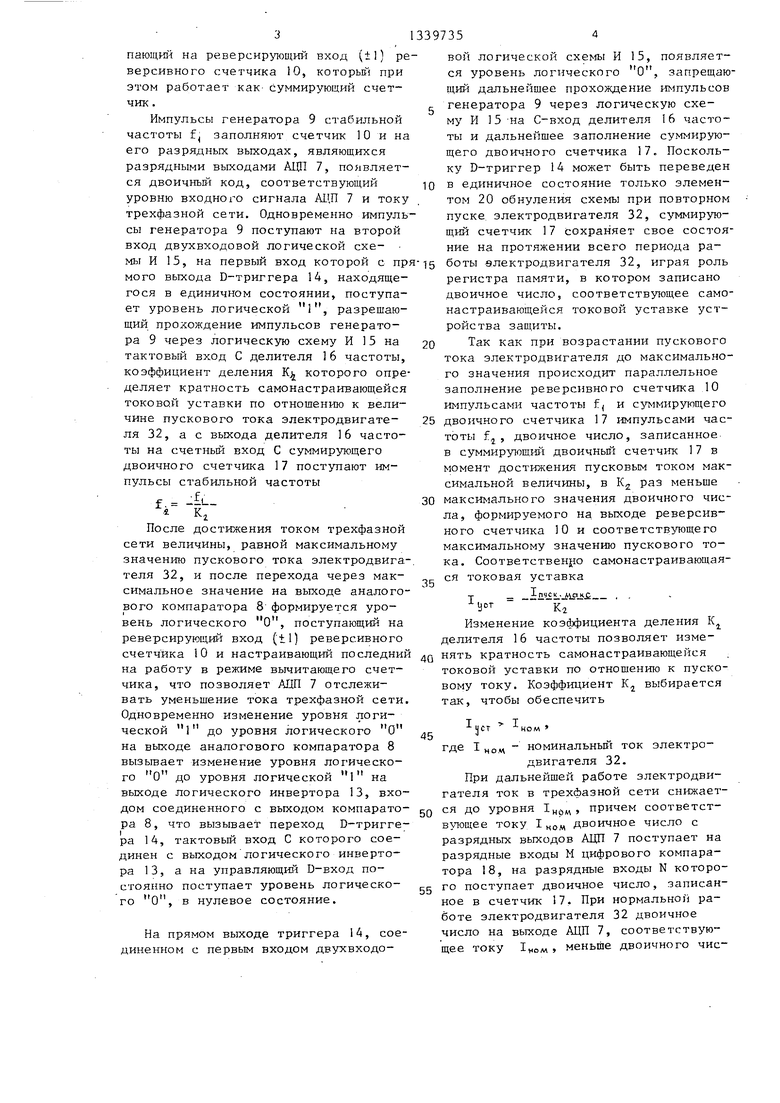

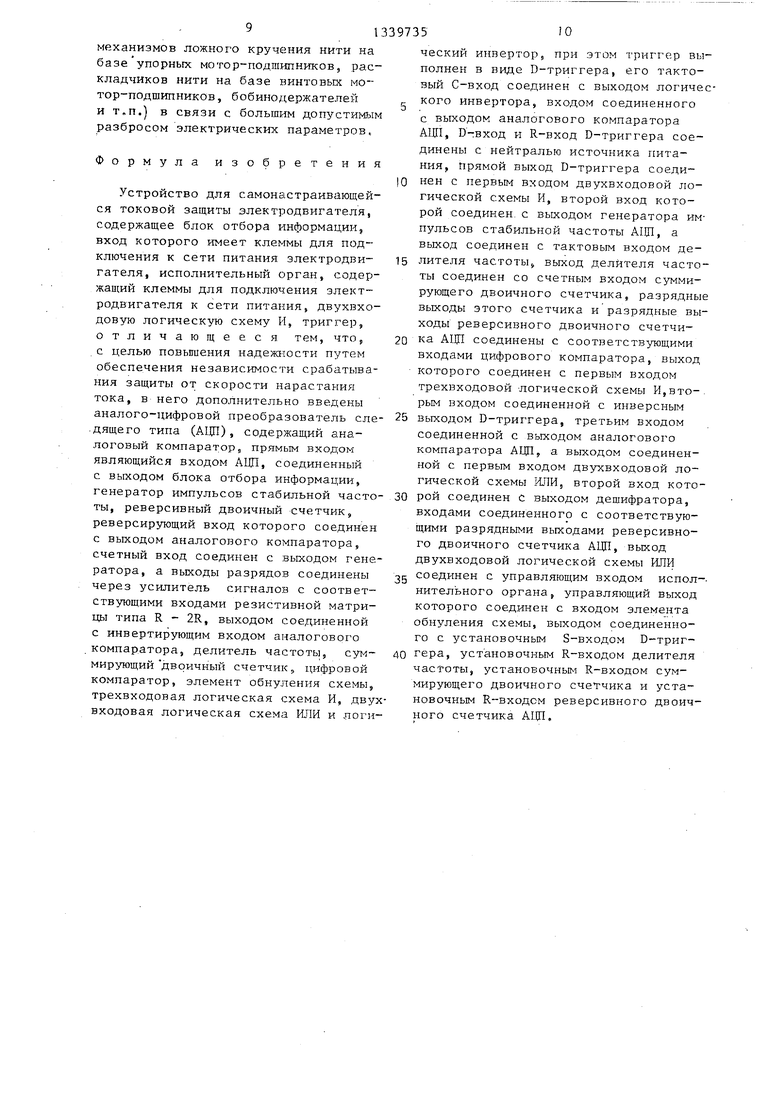

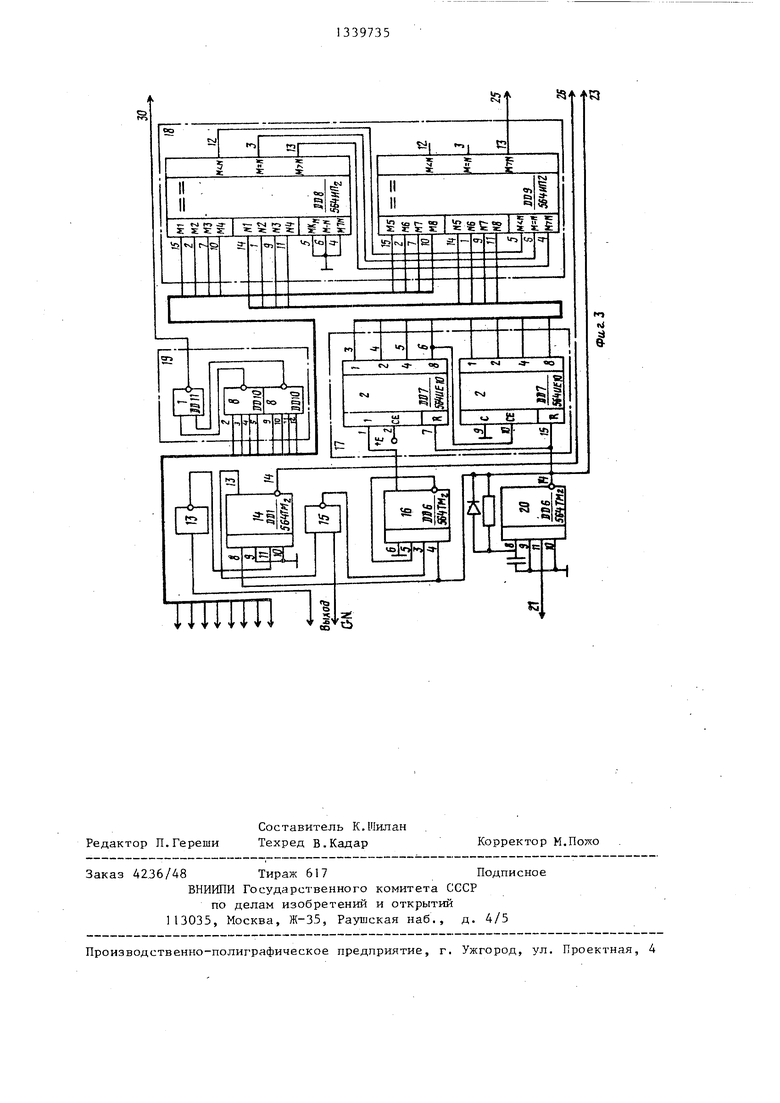

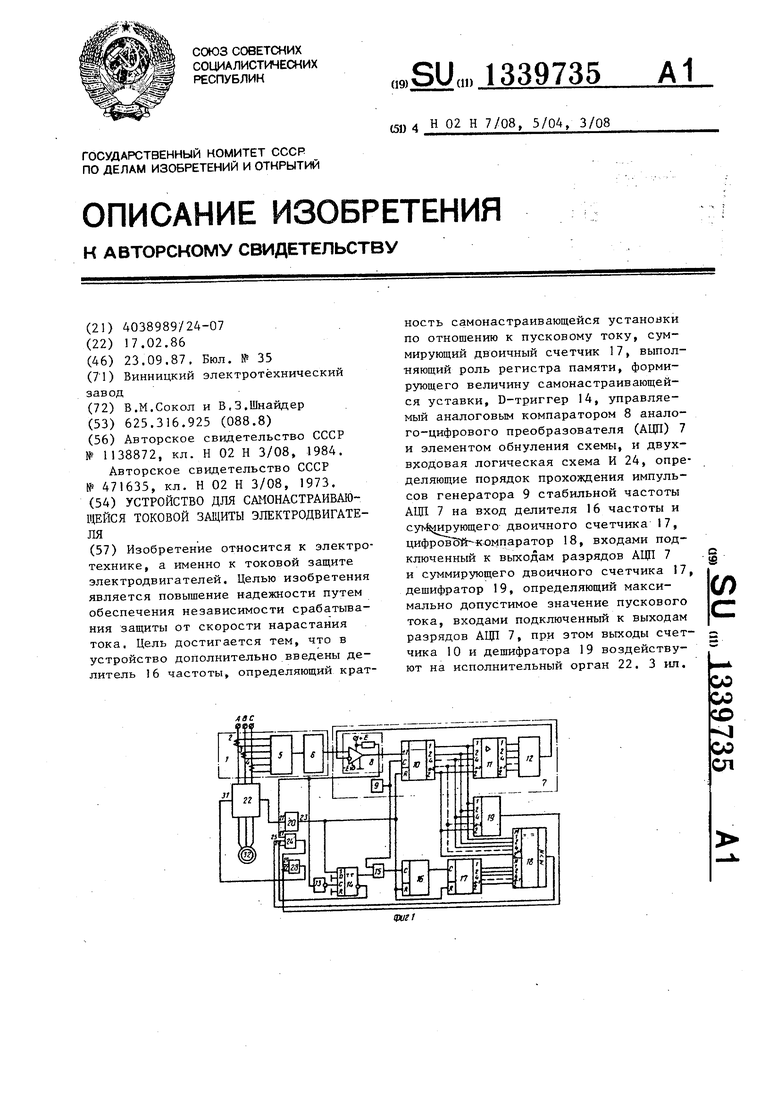

На фиг,1 представлена схема устройства; на фиг,2 и 3 - примеры реали зации входящих в устройство блоков,

.Устройство содержит блок 1 отбора информации, в состав которого входят трансформаторы 2-4 тока, преобразующие действующее значение фазных токов в напряжение, трехфазный двух- полупериодный выпрямитель 5 и сглаживающий контур 6; аналого-цифровой преобразователь (АЦП) 7 следящего типа, в состав которого входят аналоговый компаратор 8 генератор 9 импульсов стабильной частоты, реверсивный двоичный счетчик 10, усилитель 11 сигналов и резистивная матрица 12 типа R-2R; логический инвертор 13, входом подключенный к выходу аналогового компаратора 8, а выходом соединенный с тактовым С-входом D-тригге- ра 14, D-вход и R-вход которого соединены с нейтралью источника питания, а прямой выход соединен с первым входом двухвходовой логической схемы И 15, вторым входом соединенной с выходом генератора 9 АЦП 7, а выходом соединенной с входом С делителя 16 частоты; суммирующий двоичный счетчик 17, счетный вход С которого соединен с выходом делителя 16 частоты; цифровой компаратор 18, входы . логического слова М которого поразрядно соединены с выходами разрядов АЦП 7, а входы логического слова N поразрядно соединены с выходами разрядов суммирующего двоичного счетчика 17; дешифратор 19, входы которого поразрядно соединены с выходами разрядов АЦП 7; элемент 20 обнуления схемы, вход 21 которого соединен с управляющим выходом исполнительного органа 22, а выход 23 соединен с установочным S-входом D-триггера 14, установочным R-входом делителя 16 частоты, установочным R-входом суммирующего двоичного счетчит а 17 и установочным R-входом реверсивного счетчика 10; трехвходовую логическую схему И 24, первый вход 25 которой

соединен с выходом цифрового компаратора 8, второй вход 26 соединен с инверсным выходом D-триггера 14, J. третий вход 27 соединен с выходом аналогового компаратора 8; двухвхо- довую логическую схему ИЛИ 28, первый вход 29 которой соединен с выходом логической схемы И 24, второй 10 вход 30 соединен с выходом дешифратора 19, а выход соединен с управляющим входом 3I исполнительного органа 22, силовыми входами подключенного к фазан А, В и С трехфазной сети, 15 а силовыми выходами соединенного с электродвигателем 32,

Устройство работает следующим образом.

При включении электродвигателя 20 32 исполнительным органом 22 последний, воздействуя на вход 21 элемента .20 обнуления схемы, запускает его. На выходе 23 элемента 20 обнуления схемы формируется при этом одиночный 25 импульс, длительность которого значительно меньше времени нарастания пускового тока электродвигателя. Этот импульс поступает на S-вход D-триггера 14, устанавливая его в 30 единичное состояние, и на R-входы реверсивног о счетчика 10, делителя 16 частоты и суммирующего двоичного счетчика 17, устанавливая оба счетчика и делитель частоты в нулево.е, 35 состояние.

При появлении тока в фазах А, В и С трехфазной сети трансформаторы 2-4 тока преобразуют значения фазньк токов в напряжение

,-I.,

где 1) - величина тока в соответствующей фазе, Kj. - коэффициент пропорциональности. ,

45 Выходное напряжение трансформаторов 2-4 выпрямляется трехфазным двух- полупериодным выпрямителем 5 и сглаживающим контуром 6, причем йа выходе последнего, являющемся выходом бло5Q ка 1 отбора информации, образуется постоянное напряжение, уровень кото- рого пропорционален току трехфазной сети. Это напряжение поступает на прямой вход аналогового компаратора 8,

(с являющийся входом .АЦП 7. При возрастании уровня напряжения, обусловленном возрастанием тока трехфазной сети, на выходе компаратора 8 формируется уровень логической 1, лоступаю1ди1 на реверсирующий вход (±1) реверсивного счетчика 10, которы при этом работает как- суммирующий счетчик .

Импульсы генератора 9 стабильной частоты f заполняют счетчик 10 и на его разрядных выходах, являющихся разрядными выходами АЦП 7, появляется двоичный код, соответствующий уровню входного сигнала АЦП 7 и току трехфазной сети. Одновременно импульсы генератора 9 поступают на второй вход двухвходовой логической схе- - мы И 15, на первый вход которой с пр МОго выхода D-триггера 14, находящегося в единичном состоянии, поступа ет уровень логической 1, разрещаю- щий прохождение имлульсов генератора 9 через логическую схему И 15 на тактовый вход С делителя 6 частоты, коэффициент деления К которого определяет кратность самонастраивающейся токовой уставки по отнощению к величине пускового тока электродвигателя 32, а с делителя 16 частоты на счетньш вход С суммирующего двоичного счетчика 17 поступают импульсы стабильной частоты

f. К,

После достижения током трехфазной сети величины, равной максимальному значению пускового тока электродвигателя 32, и после перехода через максимальное значение на выходе аналогового компаратора 8 формируется уровень логического О, поступающий на реверсирующий вход (+1) реверсивного счетчика 10 и настраивающий последний на работу в режиме вычитающего счетчика, что позволяет АЦП 7 отслеживать уменьщение тока трехфазной сети. Одновременно изменение уровня логической 1 до уровня логического О на выходе аналогового компаратора 8 вызьшает изменение уровня логического О до уровня логической l на выходе логического инвертора 13, входом соединенного с выходом компаратора 8, что вызывает переход D-триггера 14, тактовый вход С которого соединен с выходом логического инвертора 13, а на управляющий D-вход постоянно поступает уровень логического О, в нулевое состояние.

На прямом выходе триггера 14, соединенном с первым входом двухвходо397354

вой логической схемы И 15, появляется уровень логического О, запрещающий дальнейшее прохождение импульсов (- генератора 9 через логическую схему И 15 -на С-БХОД делителя 16 частоты и дальнейшее заполнение суммирующего двоичного счетчика 17. Поскольку D-триггер 14 может быть переведен 10 в единичное состояние только элементом 20 обнуления схемы при повторном пуске электродвигателя 32, суммирующий счетчик 17 сохраняет свое состоя ние на протяжении всего периода ра- 5 боты электродвигателя 32, играя роль регистра памяти, в котором записано двоичное число, соответствующее самонастраивающейся токовой уставке устройства защиты.

0 Так как при возрастании пускового тока электродвигателя до максимального значения происходит параллельное заполнение реверсивного счетчика 10 импульсами частоты f( и суммирующего 5 двоичного счетчика 17 импульсами частоты f,j, , двоичное число, записанное в суммирующий двоичньш счетчик 17 в момент достижения пусковым током максимальной величины, в Kg раз меньше 0 максимального значения двоичного числа, формируемого на выходе реверсивного счетчика 10 и соответствующего максимальному значению пускового тока. Соответствен самонастраивающаяся токовая уставка

5

1.,,

Ki Изменение коэффициента деления К делителя 16 частоты позволяет изме- Q нять кратность самонастраивающейся токовой уставки по отношению к пусковому току. Коэффициент К выбирается так, чтобы обеспечить

где I цодд - номинальный ток электродвигателя 32.

При дальнейшей работе электродвигателя ток в трехфазной сети снижается до уровня 1цй« причем соответствующее току I ном двоичное число с разрядных выходов АЦП 7 поступает на разрядные входы М цифрового компаратора 18, на разрядные входы N которого поступает двоичное число, записанное в счетчик 17, При нормальной работе электродвигателя 32 двоичное число на выходе АЦП 7, соответствующее току IXOM меньше двоичного числа, записанного в счетчик 17 и соответствующего токовой уставке I.CT и на выходе цифрового компаратора 18 формируется уровень логического О.

При перегрузке электродвигателя ток в трехфазной сети начинает превышать величину Iijcr , хотя остается

Аналоговый компаратор 8 АЦП 7 построен на интегральной микросхеме DAI типа 521 САЗ. Кроме того, в качестве аналогового компаратора могут быть применены микросхемы типа К554СА2, К554САЗ, К554СА4. Генератор 9 АЦП 7 построен на микросхеме DDI типа 564ТМ2, представляющей собой два неменьше уровня InijcK.MdKC При этом дво--|Q зависимых D-триггера (в схеме генера- ичное число на разрядных входах М цифрового компаратора 18, поступающее с разрядных выходов АЦП 7, начинает превьппать двоичное число на разрядных входах N, поступающее с разрядных выходов счетчика 17, на выходе цифрового компаратора 18 появляется уровень логической 1, являющийся сигналом срабатывания защиты и постутора использован один из них). При необходимости повышения точности АЦП приведенньй на фиг.2 генератор 9 может быть заменен кварцевым генератором.

Реверсивньш счетчик 10 АЦП 7 реализован на двух последовательно соединенных микросхемах DD2 и DD3 типа

|564ИЕ1 1 ,каждая из которых представ- пающий на первый вход 25 трехвходовой 20 ляет собой 4-разрядный двоичный ре- логической схемы И 24, на второй версивньй счетчик. Реверсирующие вхо- вход 26 которой поступает разрешающий сигнал с инверсного выхода D- триггера 14, чем предотвращается ложное срабатывание защиты при превьщте- нии двоичного числа, соответствующе- Г-Р. пусковому току,, над двоичным числом, записанным в суммирующий счетчик 17, в период формирования самоды (tl) обеих микросхем (вывода 10) соединены между собой и подключены к выходу аналогового компаратора 8 (к, 25 выводу 1 микросхемы DA1). Выход переноса (вывод 7) микросхемы DD2 соединен с тактовым входом С (вывод 15) микросхемы DD3, а тактовый С-вход (вывод 1 5) микросхемы DD2 и вход РЕ

ды (tl) обеих микросхем (вывода 10) соединены между собой и подключены к выходу аналогового компаратора 8 (к, 25 выводу 1 микросхемы DA1). Выход переноса (вывод 7) микросхемы DD2 соединен с тактовым входом С (вывод 15) микросхемы DD3, а тактовый С-вход (вывод 1 5) микросхемы DD2 и вход РЕ

настраивающейся уставки, и на третий зо разрешения счета (вывод 1) микрос хе- вход 27 которой поступает разрешающий сигнал с выхода аналогового компаратора 8, чем обуславливается сра- батьшаниё защиты только при возрастамы DD3 соединены с выходом генератора 9 (вьшод 1 микросхемы DU1).

Остальные входы микросхем DD2 и DD3 соединены с нейтралью источни- 35 ка питания. Выходы этих микросхем яв ляются выходами разрядов АЦП 7, причем вьЕходы микросхемы DD2 являются -четырьмя младшими, а выходы микросхемы DD3 - четярьмя старшими разрядами

нии тока трехфазной сети и предотвращается ложное срабатывание защиты при снижении тока электродвигателя

от I

nijcv. MgiKC

ДО I

У

в пусковой пеОстальные входы микросхем DD2 и DD3 соединены с нейтралью источни- 35 ка питания. Выходы этих микросхем являются выходами разрядов АЦП 7, причем вьЕходы микросхемы DD2 являются -четырьмя младшими, а выходы микросхемы DD3 - четярьмя старшими разрядами

риод.

Сигнал с выхода трехвходовой логи- 40 8-разрядного двоичного кода АЦП 7. ческой схемы И 24 поступает на первый Кроме того, выходы микросхем DD2 иВВЗ

вход 29 двухвходовой логической схемы ИЛИ 28, выход которой воздействует на управляющий вход 31 исполнительного органа 22, чем обеспечивается отключение электродвигателя 32

при его перегрузке.

Если при включении электродвигателя 32 пусковой ток превьшает максимально допустимое значение, на выходе АЦП 7 появляется соответствующее двоичное число, вызывающее появление уровня логической l на выходе дешифратора 19, на втором входе 30 и на выходе двухвходовой логической схемы ИЛИ 28 и на управляющем вхо-де 31 исполнительного органа 22, чем обеспечивается отключение электродвигателя 32 от сети.

Аналоговый компаратор 8 АЦП 7 построен на интегральной микросхеме DAI типа 521 САЗ. Кроме того, в качестве аналогового компаратора могут быть применены микросхемы типа К554СА2, К554САЗ, К554СА4. Генератор 9 АЦП 7 построен на микросхеме DDI типа 564ТМ2, представляющей собой два независимых D-триггера (в схеме генера-

зависимых D-триггера (в схеме генера-

тора использован один из них). При необходимости повышения точности АЦП приведенньй на фиг.2 генератор 9 может быть заменен кварцевым генератором.

Реверсивньш счетчик 10 АЦП 7 реализован на двух последовательно соединенных микросхемах DD2 и DD3 типа

|564ИЕ1 1 ,каждая из которых представ- 20 ляет собой 4-разрядный двоичный ре- версивньй счетчик. Реверсирующие вхо-

ды (tl) обеих микросхем (вывода 10) соединены между собой и подключены к выходу аналогового компаратора 8 (к, 25 выводу 1 микросхемы DA1). Выход переноса (вывод 7) микросхемы DD2 соединен с тактовым входом С (вывод 15) микросхемы DD3, а тактовый С-вход (вывод 1 5) микросхемы DD2 и вход РЕ

зо разрешения счета (вывод 1) микрос хе-

зо разрешения счета (вывод 1) микрос хе-

мы DD3 соединены с выходом генератора 9 (вьшод 1 микросхемы DU1).

Остальные входы микросхем DD2 и DD3 соединены с нейтралью источни- 35 ка питания. Выходы этих микросхем являются выходами разрядов АЦП 7, причем вьЕходы микросхемы DD2 являются -четырьмя младшими, а выходы микросхемы DD3 - четярьмя старшими разрядами

через усилитель 11 сигналов, реализованный на микросхемах DD4 и DD5 типа 564ПУ4, соединены, с разрядными входа45 1ЧИ резистивной матрицы типа R - 2R, в качестве которой применена микросхема DA2 типа 304ИД4Б, причем выход последней (вывод 1) соединен с инверсным входом (вывод 3) микросхемы

5Q DA1. В качестве резистивной матрицы типа R - 2R могут быть применены также микросхемы типа 301НР4, 301НР6, 301 HP 12 и другие функционально подобные типы микросхем.

D-триггер 14 представляет собой

55

неиспользованный триггер микросхемы DD1 типа 564та2.

Поскольку пусковой ток электродвигателя превьш1ает его номинальный ток

71339735

не более, чем в 5-10 раз, а тик самонастраивающейся уставки должен быть меньше пускового и больше номинально10

го, достаточно установить коэффициент g деления частоты .

В качестве делителя 16 частоты использован включенный по счетному входу D-триггер (микросхема DD6 типа 564ТМ2), При этом К 2. При необходимости установки большего значения К в качестве делителя частоты может быть использован двоичный счетчик типа 564ИЕ10 ипи делитель частоты с переменным регулируемым ентом деления.

Двоичный суммирующий счетчик 17 вьтолнен 8-разрядным и реализован на микросхеме .DD7 типа 564ИЕ10, представляющей собой два независимых 4-разрядных двоичных счетчика. Для получения 8-разрядного счетчика оба счетчика микросхемы DD7 соединены последовательно . Счетный С-вход счетчиПри необходимости дешифрирования меньшего 8-разрядного двоичного числа те выходы разрядов АЦП 7, в которых при записи двоичного числа, соответствующего максимально допустимому значению пускового тока, содержится двоичное число О, подключаются к соответствующим входам 8-разрядной логической схемы И (микросхема DD10) через логические инверторы.

Установочные R-входы (выводы 9) микросхем DD2 и DD3 типа 564ИЕ11, образующих реверсивный счетчик 10 коэффици-15 АЦП 7, установочные R-входы (выводы 7 и 15) микросхемы DD7 типа 564ИЕ10, на которой построен двоич- ньй суммир5тощий счетчик 17, установоч- ньй R-вход триггера - делителя 16 частоты - (вывод 4 микросхемы DD6 типа 564ТМ2) и установочный S-вход D-триггера 14 (вьюод 8 микросхемы, DD1 типа 564ТМ2) соединены с выходом 23 одновибратора 20, реализованного на

20

ка 17 (вывод 1 микросхемы DD7) соеди- 25 неиспользованном D-триггере микросхе- нен с прямым выходом триггера - дели- мы DD6 типа 564ТМ2, причем выходу од- теля 16 частоты (с выводом 1 микро- новибратора 20 соответствует вывод 12 схемы DD6).микросхемы DD6, а входу одновибратоРазрядные выходы счетчика 17 (вы- ра 20, соединенному с управляющим вы- воды 3-6 и 11-14 микросхемы DD7) сое- 30 ходом 21 исполнительного органа 22,

динены с разрядными входами слова N, . а разрядные выходы АЦП 7 - с разрядными выходами слова М 8-разрядного цифрового компаратора 18, реализованного на двух последовательно .соединенных 4-разрядных цифровых компараторах типа 564ИП2 (микросхемы DM и DD9), причем выхОд цифрового компаратора 18 (вывод 13 микросхемы DD9) соединен с входом трехвходовой логической схемы И 24,

Поскольку зада чей дешифратора 19 является дешифрирование одного двоичного числа, соответствующего максимально допустимому значению пускового 45 шении действующим значением тока ветока, дешифратор 19 выполнен упрощенным и представляет собой 8-входовую логическую схему И, реализованную на двух элементах 4И-НЕ (микросхема DD10

типа 564ЛА8) и элементе 2ИЛИ-НЕ (мик- 50 шении пусковым .током максимально доросхема DD11 типа 564ЛЕ5),

В рассматриваемом примере макси- мально допустимому значению пускового тока соответствует наибольшее 8-раз-- рядное двоичное число 11111111, поэтому все входы 8-входовой логической схемы И (выводы 2-5 и 9-12 микросхемы DD10) подключены непосредственно к выходам разрядов АЦП 7,

пустимого значения, чем достигается поставленная цель.

Применение предлагаемого изобретения обеспечивает эффективную токовую 55 защиту электродвигателей при самонастраивающейся уставке срабатывания, что особенно важно при массовом применении и частой замене электродвигателей (например, электроверетен.

10

15

20

соответствует вывод 11 микросхемы DD6,

В качестве элементной базы могут быть использованы также микросхемы

серий КПЗ, К155, К176, К555, К561 и другие. Однако применение микросхем серий К561 и 564 предпочтительней в связи с их высокой помехоустойчивостью и малым энергопотреблением,

Таким образом, устройство обеспечивает получение самонастраивающейся токовой уставки срабатывания, кратной пусковому току электродвигателя, отключение электродвигателя при превыличины самонастраивающейся уставки :при независимости срабатывания от скорости нарастания тока, а также отключение электродвигателя при превыпустимого значения, чем достигается поставленная цель.

Применение предлагаемого изобретения обеспечивает эффективную токовую защиту электродвигателей при самонастраивающейся уставке срабатывания, что особенно важно при массовом применении и частой замене электродвигателей (например, электроверетен.

механизмов ложного кручения нити на базе упорных мотор-подшипников, раскладчиков нити на базе винтовьк мо- тор-подшртников, бобинодержателей и т.п.) в связи с большим допустимым разбросом электрических параметров.

Формула изобретения

Устройство для самонастраивающейся токовой защиты электродвигателя, содержащее блок отбора информации, вход которого имеет клеммы для подключения к сети питания электродвигателя, исполнительный орган, содержащий клеммы для подключения злект- родвигателя к сети питания, двухвхо- довую логическую схему И, триггер, отличающееся тем, что с целью повыгиения надежности путем обеспечения независимости срабатывания защиты от скорости нарастания тока, в него дополнительно введены аналого-цифровой преобразователь сле .дящего типа (АЦП), содержащий аналоговый компаратор, прямым входом являющийся входом АЦП, соединенный с выходом блока отбора информации,

генератор импульсов стабильной часто- 30 РОЙ соединен С выходом дешифратора,

ты, реверсивный двоичный счетчик, реверсирующий вход которого соединен с выходом аналогового компаратора, счетный вход соединен с выходом генератора, а выходы разрядов соединены через усилитель сигналов с соответствующими входами резистивной матрицы типа R - 2R, выходом соединенной с инвертирующим входом аналогового компаратора, делитель частоты, суммирующий двоичный счетчик, цифровой компаратор, элемент обнуления схемы, трехвходовая логическая схема И, двух входовая логическая схема ИЛИ и логический инвертор, при этом триггер выполнен в виде D-триггера, его тактовый С-вход соединен с выходом логического инвертора, входом соединенного с выходом аналогового компаратора АЦП, Вгвход и D-триггера соединены с нейтралью источника питания, прямой выход D-триггера соединен с первым входом двухвходовой логической схемы И, второй вход которой соединен, с выходом генератора импульсов стабильной частоты АЦП, а выход соединен с тактовым входом делителя частоты выход делителя частоты соединен со счетным входом суммирующего двоичного счетчика, разрядные выходы этого счетчика и разрядные выходы реверсивного двоичного счетчика АЩ соединены с соответствующими входами цифрового компаратора, выход которого соединен с первым входом трехвходовой логической схемы И,вто-- рым входом соединенной с инверсным

выходом D-триггера, третьим входом соединенной с выходом аналогового компаратора АЦП, а выходом соединенной с первым входом двухвходовой логической схемы ИЛИ, второй вход кото5

входами соединенного с соответствующими разрядными выходами реверсивного двоичного счетчика АЦП, выход двухвходовой логической схемы ИЛИ соединен с управляющим входом испол-. нительного органа, управляющий выход которого соединен с входом элемента обнуления схемы, выходом соединенного с установочным S-входом D-триг- 0 гера, установочным R-входом делителя частоты, установочным R-входом суммирующего двоичного счетчика и установочным R--вxoдoм реверсивного двоичного счетчика АЦП,

Л А

t

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО РЕГУЛИРОВАНИЯ ТЕМПЕРАТУРЫ СУШКИ ЗЕРНА | 2008 |

|

RU2395048C2 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ВЛАЖНОСТИ СЫПУЧИХ МАТЕРИАЛОВ | 2008 |

|

RU2394232C2 |

| ДАТЧИК ВЕСА | 2003 |

|

RU2257551C2 |

| СПОСОБ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2102836C1 |

| ДАТЧИК РАСХОДА | 2003 |

|

RU2262080C2 |

| Устройство для определения остатка жидкого металла в сталеразливочном ковше | 1989 |

|

SU1634361A1 |

| СПОСОБ КОМПЬЮТЕРНОЙ РЕГИСТРАЦИИ СИГНАЛА ИЗОБРАЖЕНИЯ ИНТЕРФЕРОГРАММ И ТЕЛЕВИЗИОННАЯ СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2012 |

|

RU2491755C1 |

| СИСТЕМА УПРАВЛЕНИЯ РЕГИСТРАЦИЕЙ СТАТИЧЕСКИХ ХАРАКТЕРИСТИК МАГНИТОТВЕРДЫХ МАТЕРИАЛОВ | 1998 |

|

RU2130634C1 |

| ПАССИВНЫЙ ПРИЕМОПЕРЕДАТЧИК | 2000 |

|

RU2174239C1 |

| Устройство для управления процессом перемешивания навозных стоков | 1988 |

|

SU1558885A1 |

Изобретение относится к электротехнике, а именно к токовой защите электродвигателей. Целью изобретения является повышение надежности путем обеспечения независимости срабатывания защиты от скорости нарастания тока. Цель достигается тем, что в устройство дополнительно введены делитель 16 частоты, определяющий кратность самонастраивающейся установки по отношению к пусковому току, суммирующий двоичный счетчик 17, выполняющий роль регистра памяти, формирующего величину самонастраивающейся уставки, D-триггер 14, управляемый аналоговым компаратором 8 аналого-цифрового преобразователя (АЦП) 7 и элементом обнуления схемы, и двух- вкодовая логическая схема И 24, определяющие порядок прохождения импульсов генератора 9 стабильной частоты АЦП 7 на вход делителя 16 частоты и су 5 рующего двоичного счетчика 17, цифров й- компаратор 18, входами подключенный к выходам разрядов АЦП 7 и суммирующего двоичного счетчика 17, дешифратор 19, определяющий максимально допустимое значение пускового тока, входами подключенный к выходам разрядов АЦП 7, при этом выходы счетчика 10 и дешифратора 19 воздействуют на исполнительный орган 22. 3 ил. i (Л С

Л A A Л A Л

i«

«о

UrJ

J

Л Л Л Л

«Tj

fM

INJ

.

to ЗГ CNI

- esj

00

ta S: SJcsj

ca и

t-CNJ J-OO

5

«o и

5 g I (р

«M

b- to

T

Uj

«JTi

5ЖЖЖ1 е

№

Редактор П.Гереши

Составитель КЛЧилан Техред В.Кадар

Заказ 4236/48Тираж 617Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

-:-

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор М.Пожо

| Устройство для максимальной токовой защиты электросети с электродвигателем | 1982 |

|

SU1138872A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для токовой самонастраивающейся защиты электроустановок | 1973 |

|

SU471635A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-09-23—Публикация

1986-02-17—Подача