1

Изобретение относится к электротехнике, предназначено для дискретного регулирования электрической мощности Е электротермических установках, подключенных к трехфазной сети переменного тока без нейтрали, и является усовершенствованием изобретения по авт.св. № 596930.

Целью изобретения является обеспечение независимости величины период импульсного регулирования от дискретности регулирования и улучшение динамических характеристик регулятора путем уменьшения запаздывания.

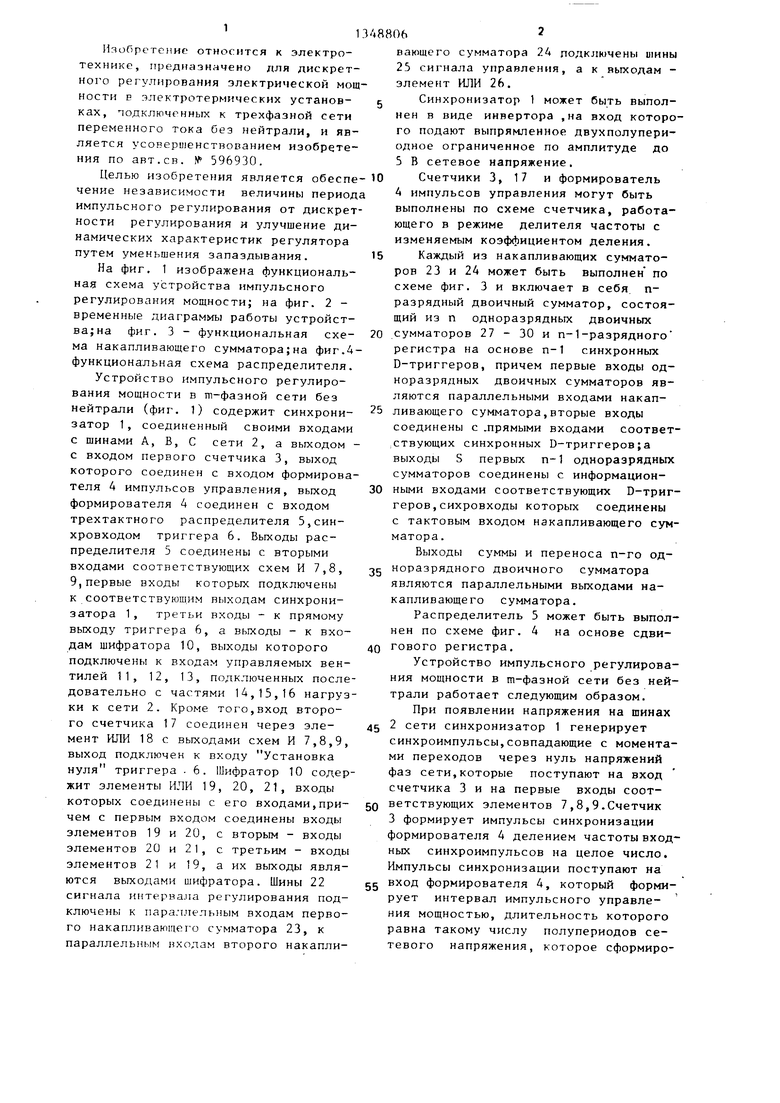

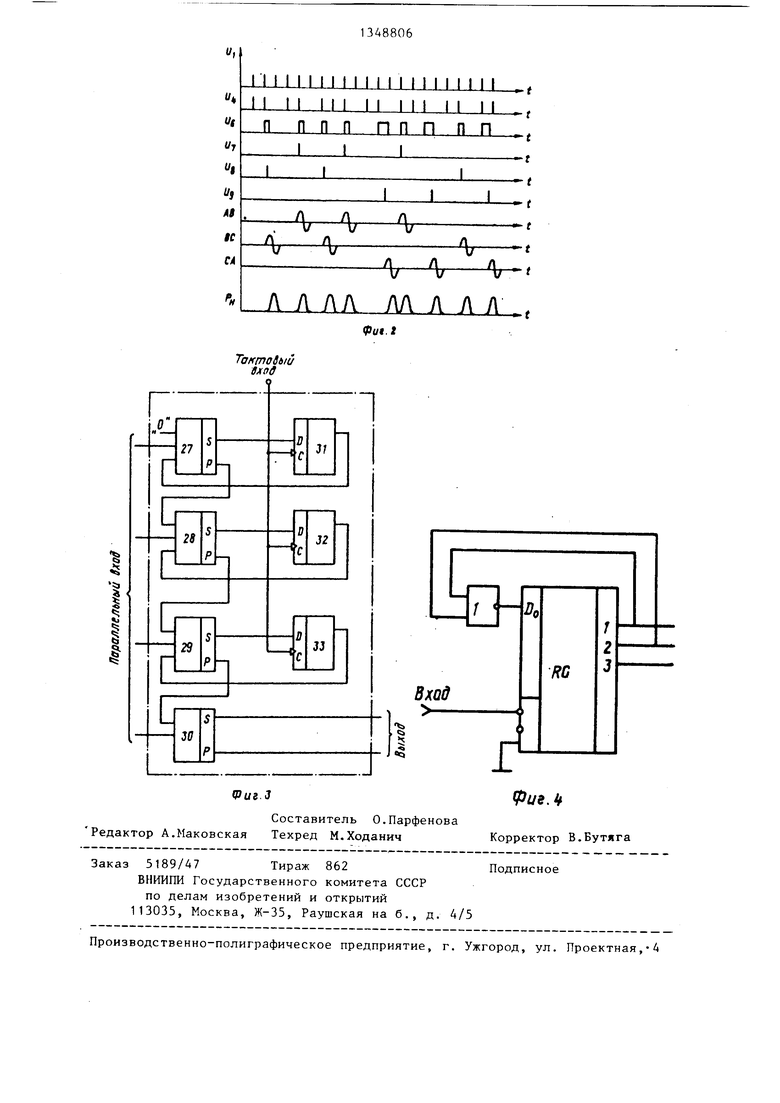

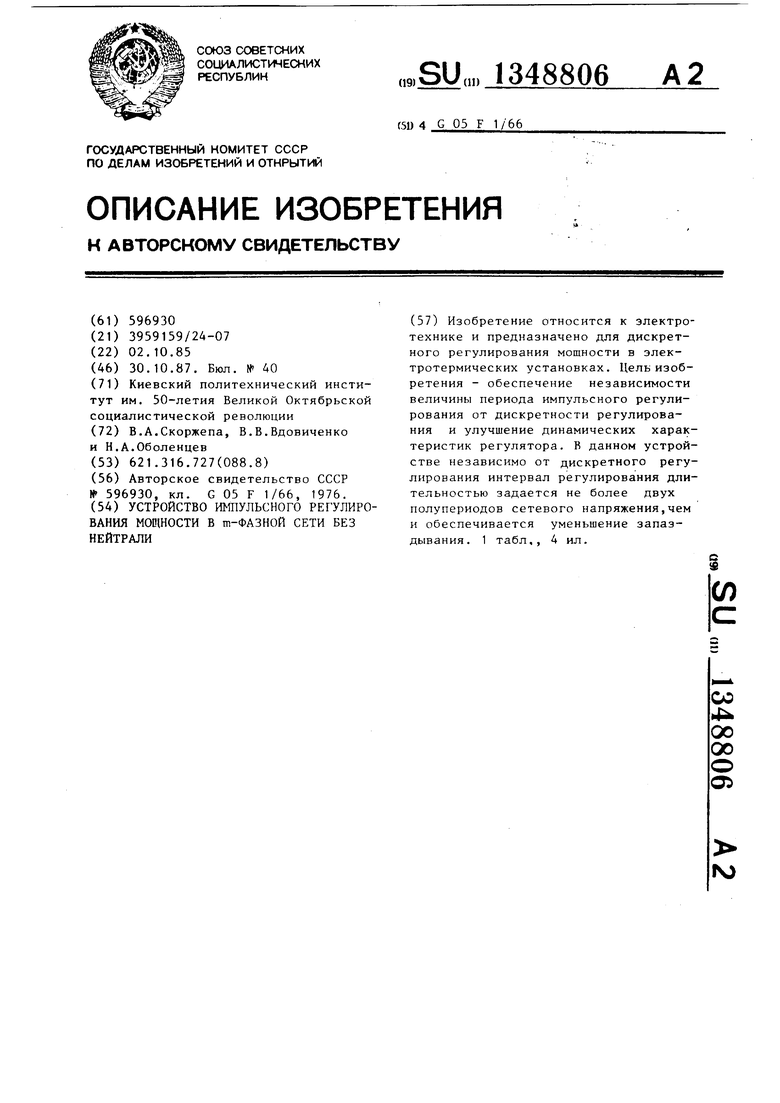

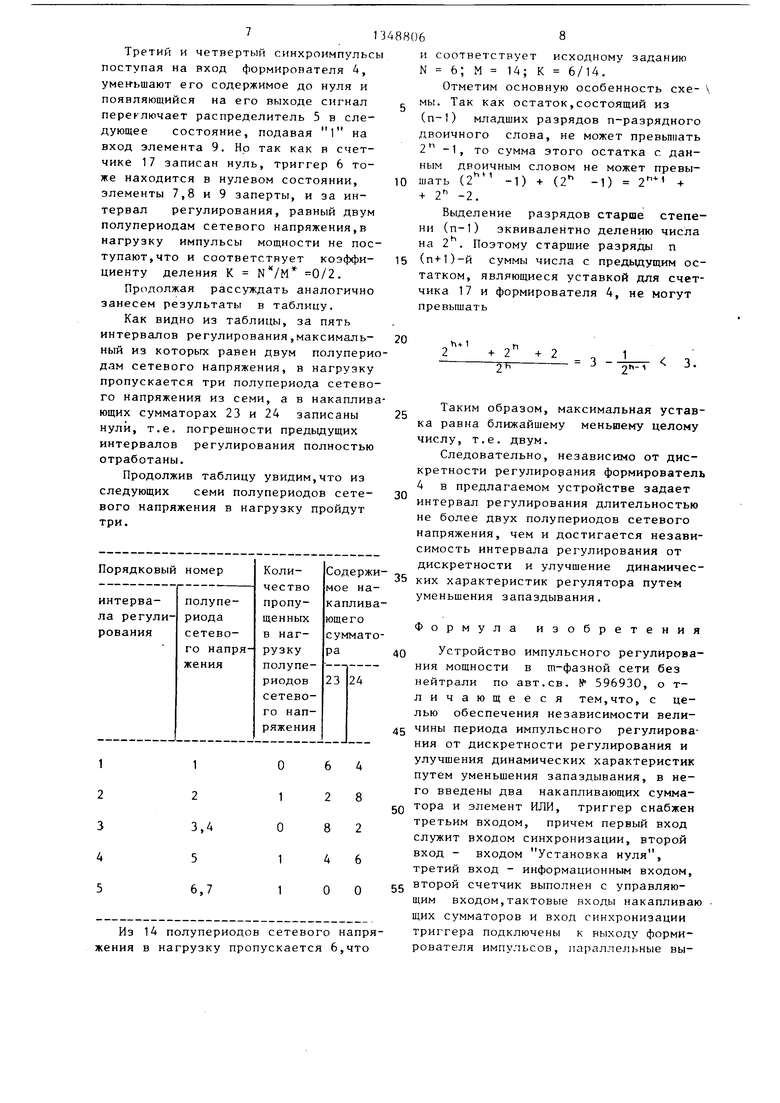

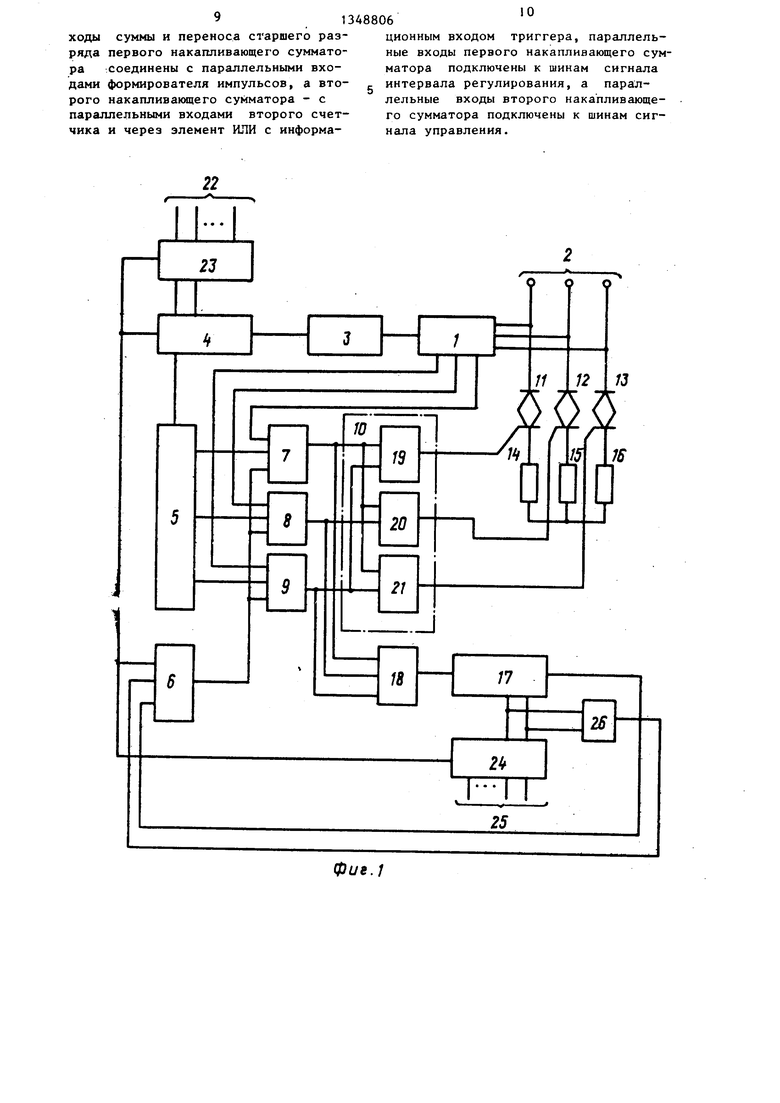

На фиг, 1 изображена функциональная схема устройства импульсного регулирования мощности; на фиг. 2 - временные диаграммы работы устройства; на фиг. 3 - функциональная схема накапливающего сумматора;на фиг.4 функциональная схема распределителя.

Устройство импульсного регулирования мощности в гп-фазной сети без нейтрали (фиг. 1) содержит синхронизатор 1, соединенный своими входами с шинами А, В, С сети 2, а выходом с входом первого счетчика 3, выход которого соединен с входом формирователя А импульсов управления, выход формирователя 4 соединен с входом трехтактного распределителя 5,син- хровходом триггера 6. Выходы распределителя 5 соединены с вторыми входами соответствующих схем И 7,8, 9,первые входы которых подключены к соответствуюш.им выходам синхронизатора 1, третьи входы - к прямому выходу триггера 6, а выходы - к входам шифратора 10, выходы которого подключены к входам управляемых вентилей 11, 12, 13, подключенных последовательно с частями 14,15,16 нагрузки к сети 2. Кроме того,вход второго счетчика 17 соединен через элемент ИЛИ 18 с выходами схем И 7,8,9, выход подключен к входу Установка нуля триггера . 6. Шифратор 10 содержит элементы ИЛИ 19, 20, 21, входы которых соединены с его входами,причем с первым входом соединены входы элементов 19 и 20, с вторьм - входы элементов 20 и 21, с третьим - входы элементов 21 и 19, а их выходы являются выходами шифратора. Шины 22 сигнала интервала регулирования подключены к пара.члельным входам первого накапливающего сумматора 23, к параллельным входам второго накапли

а

48806

Бающего сумматора 24 подключены тины 25 сигнала управления, а к выходам - элемент ИЛИ 26.

с Синхронизатор 1 может быть выполнен в виде инвертора ,на вход которого подают выпрямленное двухполупери- одное ограниченное по амплитуде до 5 В сетевое напряжение.

10 Счетчики 3, 17 и формирователь 4 импульсов управления могут быть выполнены по схеме счетчика, работающего в режиме делителя частоты с изменяемым коэффициентом деления.

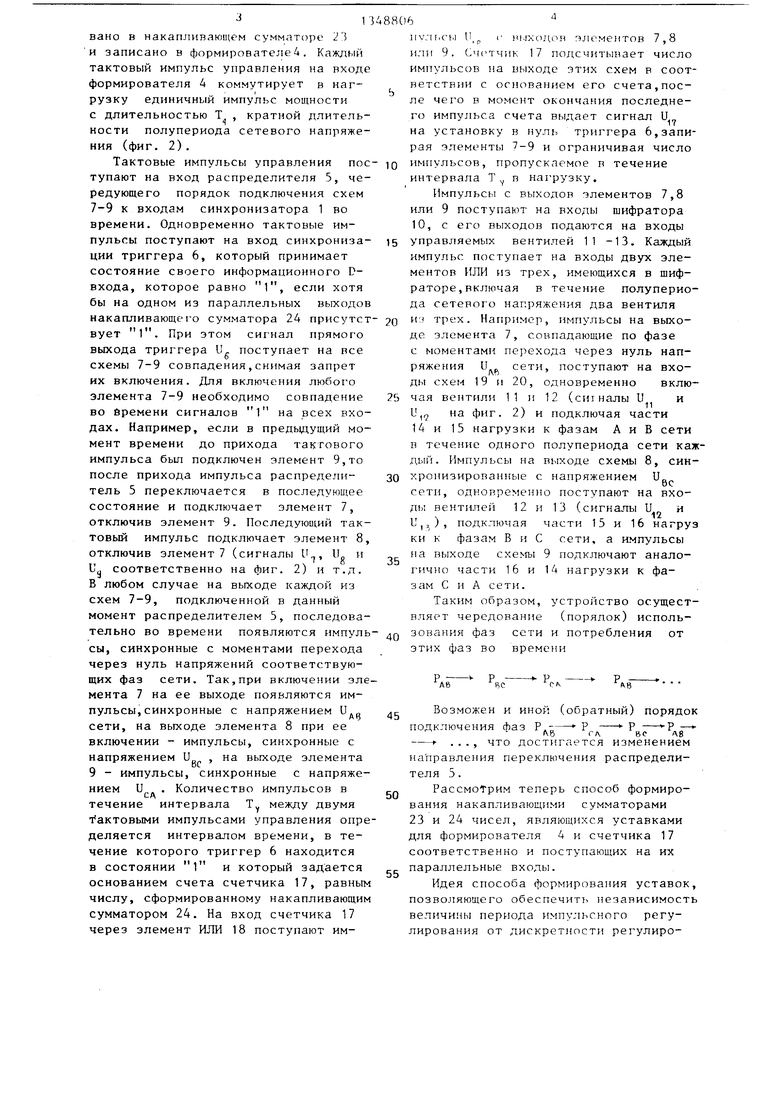

15 Каждый из накапливающих сумматоров 23 и 24 может быть выполнен по схеме фиг. 3 и включает в себя, п- разрядный двоичный сумматор, состоящий из п одноразрядных двоичных

20 сумматоров 27 - 30 и п-1-разрядного регистра на основе п-1 синхронных D-триггеров, причем первые входы одноразрядных двоичных сумматоров являются параллельными входами накап25 ливающего сумматора,вторые входы

соединены с .прямыми входами соответствующих синхронных D-триггеров;а выходы S первых п-1 одноразрядных сумматоров соединены с информацион30 ными входами соответствующих D-триггеров, сихровходы которых соединены с тактовым входом накапливающего сумматора.

Выходы суммы и переноса п-го од25 норазрядного двоичного сумматора являются параллельными выходами накапливающего сумматора.

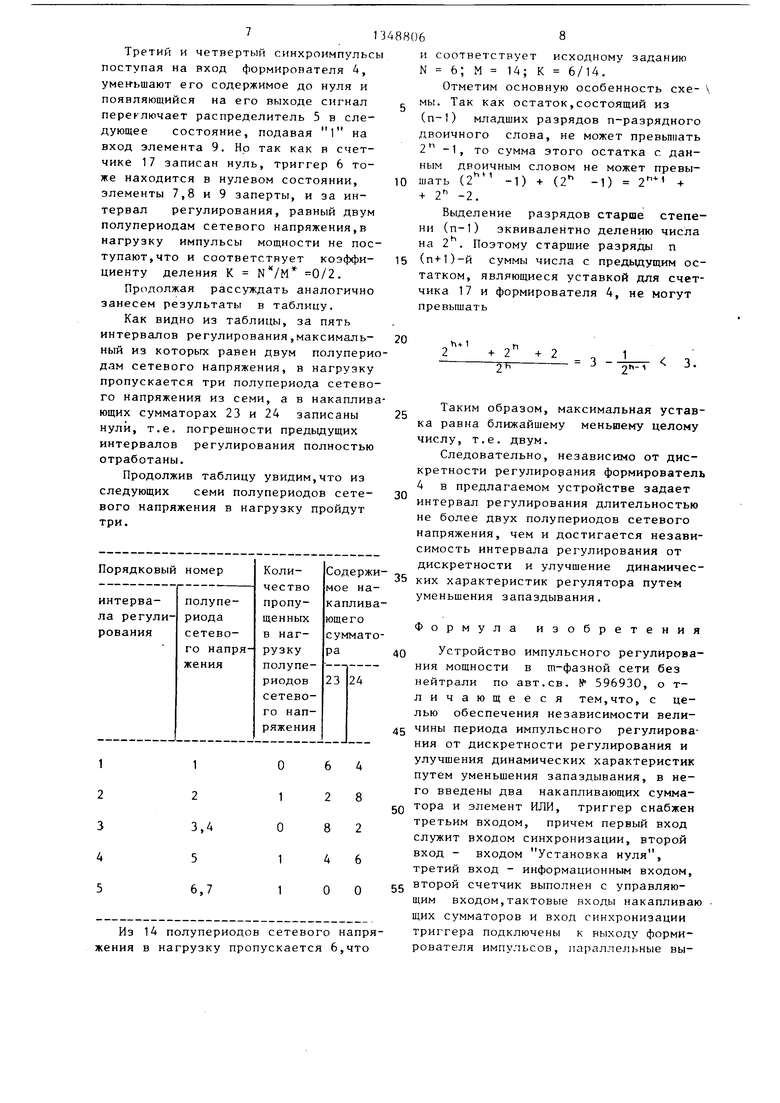

Распределитель 5 может быть выполнен по схеме фиг. 4 на основе сдви40 гового регистра.

Устройство импульсного регулирования мощности в т-фазной сети без нейтрали работает следующим образом. При появлении напряжения на шинах

45 2 сети синхронизатор 1 генерирует

синхроимпульсы,совпадающие с моментами переходов через нуль напряжений фаз сети,которые поступают на вход счетчика 3 и на первые входы соот50 ветствующих элементов 7,8,9.Счетчик 3 формирует импульсы синхронизации формирователя 4 делением частоты входных синхроимпульсов на целое число. Импульсы синхронизации поступают на

55 вход формирователя 4, который формирует интервал импульсного управления мощностью, длительность которого равна такому числу полупериодов сетевого напряжения, которое сформиро 11

ано в накапливающем сумматс ре 2 S записано в формирователей. Каждый актовый импульс управления на входе ормирователя 4 коммутирует в нагузку единичный импульс мощности длительностью Т , кратной длительности полупериода сетевого напряжения (фиг. 2).

Тактовые импульсы управления поступают на вход распределителя 5, чередующего порядок подключения схем 7-9 к входам синхронизатора 1 во времени. Одновременно тактовые импульсы поступают на вход синхронизации триггера 6, который принимает состояние своего информационного D- входа, которое равно 1, если хотя бы на одном из параллельных выходов накапливающе1 о сумматора 24 присутствует 1. При этом сигнал прямого выхода триггера U. поступает на все

о

схемы 7-9 совпадения,снимая запрет их включения. Для включения любого элемента 7-9 необходимо совпадение во йремени сигналов 1 на всех входах. Например, если в предыдущий момент времени до прихода тактового импульса был подключен элемент 9,то после прихода импульса распредетп - тель 5 переключается в последующее состояние и подключает элемент 7, отключив элемент 9. Последующий тактовый импульс подключает элемент 8, отключив элемент 7 (сигналы U, U и L соответственно на фиг. 2) и т.д.

8любом случае на выходе каждой из схем 7-9, подключенной в данный момент распределителем 5, последовательно во времени появляются импульсы, синхронные с моментами перехода через нуль напряжений соответствующих фаз сети. Так,при включении элемента 7 на ее выходе появляются импульсы, синхронные с напряжением U.., сети, на выходе элемента о при ее включении - импульсы, синхронные с напряжением U , на выходе элемента

DC

9- импульсы, синхронные с напряжением и . Количество импульсов в течение интервала Т между двумя faктoвыми импульсами управления определяется интервалом времени, в течение которого триггер 6 находится

в состоянии 1 и который задается основанием счета счетчика 17, равным числу, сформированному накапливающим сумматором 24. На вход счетчика 17 через элемент ИЛИ 18 поступают им

-

8806

iivjTi.cbi и.р с хиходон элементов 7,8 или 9. Сж тчик 17 подсчитывает число импульсов на выходе этих схем в соответствии с основанием его счета,после чего в момент окончания последнего импульса счета выдает сигнал U на установку в нуль триггера 6,запирая элементы 7-9 и ограничивая число

10 импульсов, пропускаемое в течение

интервала Т в нагрузку.

Импульсы с выходов элементов 7,8 или 9 поступают на входы шифратора 10, с его выходов подаются на входы 15 управляемых вентилей 11 -13. Каждый импульс поступает на входы двух элементов ИЛИ из трех, имеющихся в шифраторе, включая в течение полупериода сетевого напряжения два вентиля

20 трех. Например, импульсы на выходе элемента 7, совпадающие по фазе с моментами перехода через нуль напряжения и, сети, поступают на входы схем 19 и 20, одновременно вклю25 чая вентили 11 п 12 (сигналы U и и, на фиг. 2) и подключая части 14 и 15 нагрузки к фазам А и В сети и течение одного полупериода сети каждый. Импульсы на выходе схемы 8, син30 хропизированные с напряжением U

сетп, одновременно поступают на входы вентилей 12 и 13 (сигналы U и и,- ) , подключая части 15 и 16 нагруз ки к фазам В и С сети, а импульсы на выходе схемы 9 подключают аналогично части 16 и 14 нагрузки к фазам С и А сети.

Таким образом, устройство осуществляет чередование (порядок) испольдд зевания фаз сети и потребления от этих фаз во времени

35

де

РСЛ

лв

Возможен и иной (обратный) порядок

подключения фаз Р.- лв

р р

г л в с А 8 ЧТО достигается изменением

направления переключения распределителя 5.

Рассмотрим теперь способ формирования накапливающими сумматорами 23 и 24 чисел, являющихся уставками для формирователя 4 и счетчика 17 соответственно и поступающих на их параллельные входы.

Идея способа формирования уставок, позволяющего обеспечип независимость величины периода импульсного регулирования от дискретности регулированияи уменьшить запаздывание, заключается в следующем.

В начале каждого интервала регулирования в устройство поступают п-раз- рядные двоичные коды сигнала управления и числам М, равного 1/В,где D - дискретность регулирования .Устройство по основному авт.св. № 596930 отрабатывает задание, пропуская в нагрузку N элементарных посылок мощности (в частном случае - полупериодов сетевого напряжения) из М, составляющих интервал регулирования.

В предлагаемом устройстве вместо чисел М и N для регулирования используются уставки М и N , являющиеся старшими разрядами чисел М и N соответственно, и устройство за интервал регулирования,равный М полупериодам сетевого напряжения,пропускает в нагрузку N полупериодов. Образовавишеся при зтом остатки (М-М ) и (N-N 2) запоминаются и учитываются в следующий интервал регулирования путем сложения их с числами М и N.

Операции выделения старших разрядов и учитывания младших в следующем интервале регулирования производятся в накапливающих сумматорах.

Рассмотрим работу устройства в целом на конкретном примере (для простоты понимания в десятичном коде).

Пусть N Ь, М 14.Записав числа N и MB виде 06 и 14 соответственно выделим их старшие разряды:

г

N

О, М 1, которые в качестве уставок поступают на параллельные входы счетчика 17 и формирователя А соответственно. Первый синхроимпульс с выхода синхронизатора 1 через счетчик 3 (примем его основание счета равным 1) поступает на вход формирователя 4, содержимое которого равно 1, вычитает единицу,и на выходе формирователя 4 появляется сигнал,переключающий распределитель в следующее состояние и поступающий на тактовые входы накапливающих сумматоров 23 и 24. Однако ни на одном из выходов элементов 7-9 сигнала не появляется,так как в счетчике 17 запи-55 формируются числа и 14+8

сан нуль, а следовательно, прямый вы- 22 соответственно.Старшие разряды

ход триггера 6 находится в нулевомN О и М 2 записываются соотсостоянии, запирая элементы 7-9 од-ветственно в счетчике 17 и формироновременно.вателе 4.

,. а остатки

(N-N 2) 2 остаИТак, в первый интервал регулирования, равный одному полупериоду сетевого напряжения, импульс мощности в нагрузку не поступает.

Остатки N-N 2 6 и 2 4 записаны сооответственно в накапливающих сумматорах 24 и 23.Сигнал формирователя 4 поступает на

тактовые входы накапливающих сумматоров 23 и 24, при этом происходит операция сложения в накапливающем сумматоре 23 (14 -i- 4 18), в накапливающем сумматоре 24 (6 6 12),

5 и на параллельные входы формирователя 4 и счетчика 17 поступают ста ршие разряды К 1 и N 1 (М-М 2М 8 и ются соответственно в накапливающих

0 сумматорах 23 и 24. В счетчик 17 записывается единица. Единица с параллельных выходов накапливающего сум- .матора 24 через схему ИЛИ 26 поступает на информационный вход триггера

5 6.

Второй синхроимпульс вычитает из формирователя 4 записанную единицу, и появляющийся на его выходе сигнал поступает на распределелитель,пере0 ключая его в следующее состояние

(например, подается 1 на вход элемента 8) и на синхровход триггера 6, опрокидывая его в единичное состояние. При этом открывается элемент 8, на управляющие входы тиристоров (12 и 13) поступает сигнал, тиристоры отпираются, и в части нагрузки 15 и 16 поступает импульс мощности. Сигнал с выхода схемы 8 через эле0 мент 18 поступает на вход счетчика 17,содержимое которого равно 1, вычитая из него единицы,и сигнал,появляющийся при этом на выходе счетчика 17, опрокидывает триггер 6 в

5 нуль, запирая элементы 7-9.

Итак, во второй интервал регулирования длительностью один полупериод сетевого напряжения в нагрузку поступает импульс мощности, что и

0 соответствует коэффициенту деления К 1 М .

Этим же сигналом формирователя 4, поступающим на тактовые входы накапливающих сумматоров 23 и 24, в

5

7Г3

Третий и четвертый синхроимпульсы поступая на вход формирователя 4, уменьшают его содержимое до нуля и появляющийся на его выходе сигнал переключает распределитель 5 в следующее состояние, подавая 1 на вход элемента 9. Но так как в счетчике 17 записан нуль, триггер 6 тоже находится в нулевом состоянии, элементы 7,8 и 9 заперты, и за интервал регулирования, равный двум полупериодам сетевого напряжения,в нагрузку импульсы мощности не поступают,что и соответствует коэффи- циенту деления К 0/2.

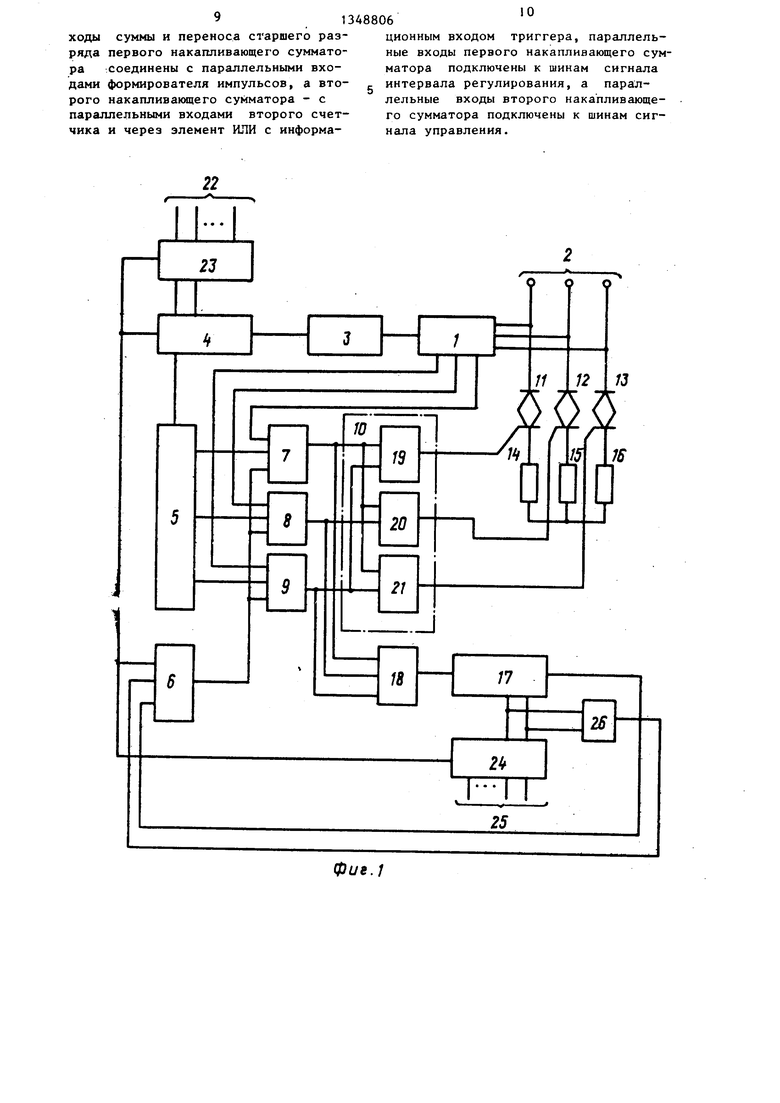

Продолжая рассуждать аналогично занесем результаты в таблицу.

Как видно из таблицы, за пять интервалов регулирования,максималь- ный из которых равен двум полупериодам сетевого напряжения, в нагрузку пропускается три полупериода сетевого напряжения из семи, а в накапливающих сумматорах 23 и 24 записаны

нули, т.е. погрешности предыдущих интервалов регулирования полностью отработаны.

Продолжив таблицу увидим,что из следующих семи полупериодов сете- вого напряжения в нагрузку пройдут три.

Из 14 полупериодов сетевого напряжения в нагрузку пропускается 6,что

и соответствует исходному заданию N 6; М 14; К 6/14.

Отметим основную особенность схе- мы. Так как остаток,состоящий из (п-1) младших разрядов п-разрядного двоичного слова, не может превьппать 2 -1, то сумма этого остатка с данным двоичным словом не может превы- шать ( -1) + (2 -1) + + 2 -2.

Выделение разрядов старше степени (п-1) эквивалентно делению числа на 2 . Поэтому старшие разряды п (п+О-й суммы числа с предыдущим остатком, являющиеся уставкой для счетчика 17 и формирователя 4, не могут превышать

h+1

3 3.

Таким образом, максимальная уставка равна ближайшему меньшему целому числу, т.е. двум.

Следовательно, независимо от дискретности регулирования формирователь 4 в предлагаемом устройстве задает интервал регулирования длительностью не более двух полупериодов сетевого напряжения, чем и достигается независимость интервала регулирования от дискретности и улучшение динамических характеристик регулятора путем уменьшения запаздывания.

Формула изобретения

Устройство импульсного регулирования мощности в т-фазной сети без нейтрали по авт.св. № 596930, о т- личающееся тем,что, с целью обеспечения независимости величины периода импульсного регулирования от дискретности регулирования и улучшения динамических характеристик путем уменьшения запаздывания, в него введены два накапливающих сумматора и элемент ИЛИ, триггер снабжен третьим входом, причем первый вход служит входом синхронизации, второй вход - входом Установка нуля, третий вход - информационным входом, е второй счетчик выполнен с управляющим входом,тактовые входы накапливаю щих сумматоров и вход синхронизации триггера подключены к выходу формирователя импульсов, параллельные выходы суммы и переноса старшего разряда первого накапливающего сумматора соединены с параллельными входами формирователя импульсов, а второго накапливающего сумматора - с параллельными входами второго счетчика и через элемент ИЛИ с информационным входом триггера, параллельные входы первого накапливающего сумматора подключены к шинам сигнала интервала регулирования, а параллельные входы второго накапливающего сумматора подключены к шинам сигнала управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство импульсного регулирования мощности в @ -фазной сети без нейтрали | 1984 |

|

SU1244652A1 |

| Устройство импульсного регулирования мощности в @ -фазной сети без нейтрали | 1985 |

|

SU1272327A1 |

| Устройство для импульсного регулирования мощности в @ -фазной сети без нейтрали и схема управления вентилями устройства для импульсного регулирования мощности в @ -фазной сети без нейтрали | 1983 |

|

SU1120467A1 |

| Многоканальное устройство для импульсного регулирования мощности в @ подключенных через вентили к сети нагрузках | 1983 |

|

SU1226585A1 |

| Устройство импульсного регулирования мощности в -фазной сети без нейтрали | 1976 |

|

SU596930A1 |

| Устройство импульсного регулирования мощности переменного тока | 1983 |

|

SU1100693A1 |

| Импульсный регулятор мощности | 1983 |

|

SU1111143A1 |

| Аналого-цифровое устройство импульсного регулирования мощности | 1983 |

|

SU1229920A1 |

| Импульсный регулятор мощности переменного тока | 1984 |

|

SU1244764A2 |

| Импульсный регулятор мощности переменного тока | 1983 |

|

SU1115179A1 |

Изобретение относится к электротехнике и предназначено для дискретного регулирования мощности в электротермических установках. Цель изобретения - обеспечение независимости величины периода импульсного регулирования от дискретности регулирования и улучшение динамических характеристик регулятора. В данном устройстве независимо от дискретного регулирования интервал регулирования длительностью задается не более двух полупериодов сетевого напряжения,чем и обеспечивается уменьшение запаздывания. 1 табл,, 4 ил. оо 00 00 о О5 N)

фие.1

Тантобый вход

Фиг J

Составитель О.Парфенова Редактор А.Маковская Техред М.Ходанич

Заказ 5189/47 Тираж 862

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская на б., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,-4

Ui.it

Корректор В.Бутяга Подписное

| Устройство импульсного регулирования мощности в -фазной сети без нейтрали | 1976 |

|

SU596930A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-10-30—Публикация

1985-10-02—Подача