1

Изобретение относится к автоматике и вычислительной технике и может найти применение в информа:ционно вы- числительных системах и в системах автоматизированного проектирования, управления, обучения в качестве средств считывания графической информации для ввода ее в ЭВМ, передачи на устройство отображения или в систему хранения.

Цель изобретения - повьпиение точности и быстродействия устройства.

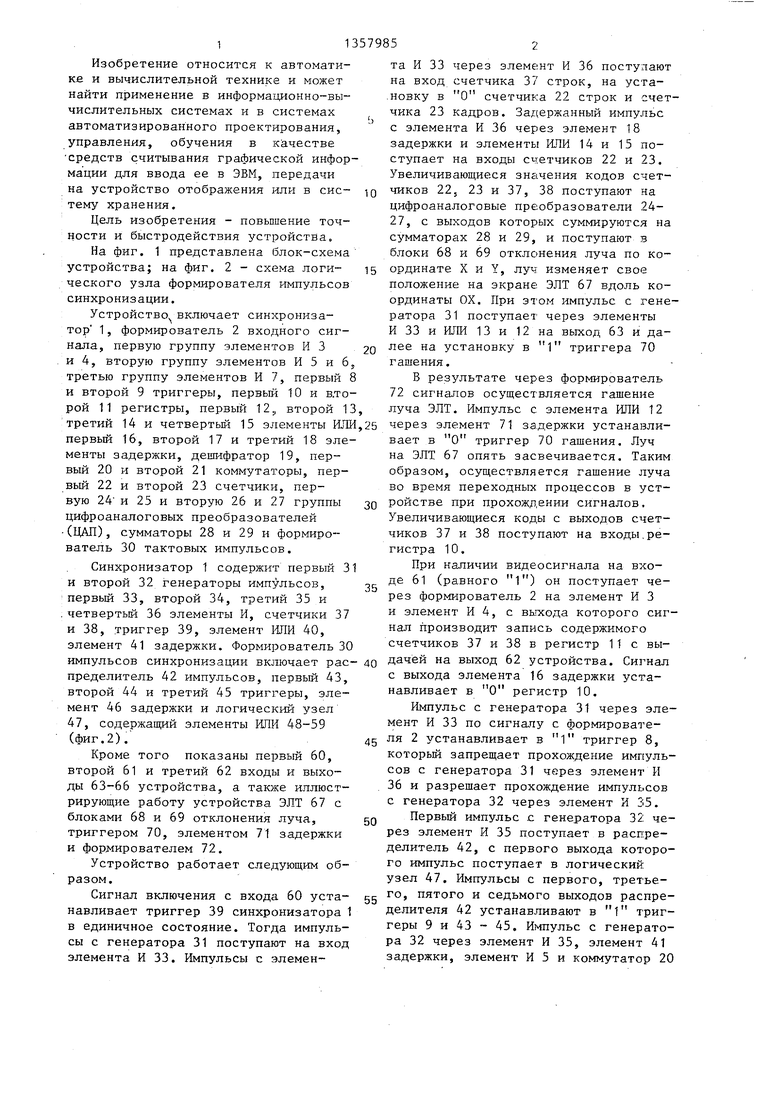

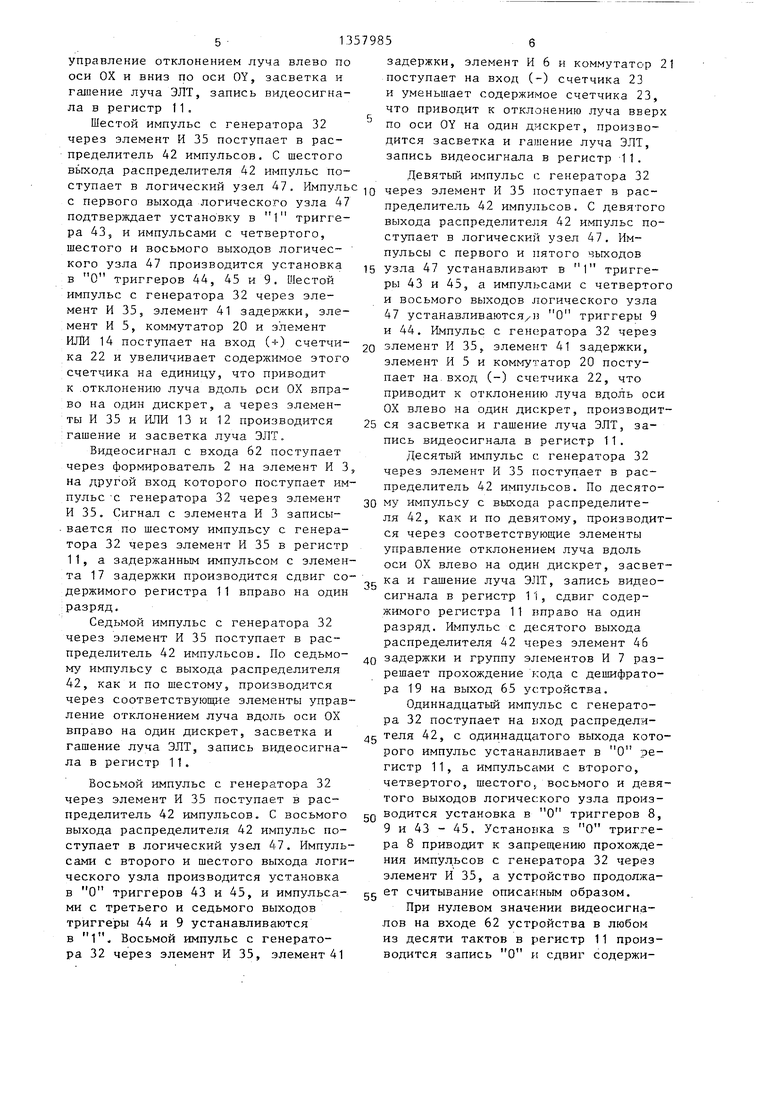

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - схема логического узла формирователя импульсов синхронизации.

Устройство включает синхронизатор 1, формирователь 2 входного сигнала, первую группу элементов И 3 и 4, вторую группу элементов И 5 и 6,, третью группу элементов И 7, первый 8 и второй 9 триггеры, первый 10 и второй 11 регистры, первый 12., второй 13,

1357985

та И 33

2

Ш

15

20

херез элемент И 36 поступают на вход счетчика 37 строк, на установку в О счетчика 22 строк и счетчика 23 кадров. Задержанный импульс с элемента И 36 через элемент 18 задержки и элементы ИЛИ 14 и 15 поступает на входы счетчиков 22 и 23. Увеличивающиеся значения кодов счетчиков 22, 23 и 37, 38 поступают на цифроаналоговые преобразователи 24- 27, с выходов которых суммируются на сумматорах 28 и 29, и поступают в блоки 68 и 69 отклонения луча по координате X и Y, луч изменяет свое положение на экране ЭЛТ 67 вдоль координаты ОХ. При этом импульс с генератора 31 поступает через элементы И 33 и ИЛИ 13 и 12 на выход 63 и далее на установку в 1 триггера 70 гашения.

В результате через формирователь 72 сигналов осуществляется гашение луча ЭЛТ. Импульс с элемента ИЛИ 12

30

35

третий 14 и четвертьш 15 элементы ИЛИ,25 через элемент 71 задержки устанавли- первый 16, второй 17 и третий 18 элементы задержки, дешифратор 19, первый 20 и второй 21 коммутаторы, первый 22 и второй 23 счетчики, первую 24 и 25 и вторую 26 и 27 группы цифроаналоговых преобразователей (ЦАП), сумматоры 28 и 29 и формирователь 30 тактовых импульсов.

Синхронизатор 1 содержит первый 31 и второй 32 генераторы импульсов, первый 33, второй 34, третий 35 и . четвертый 36 элементы И, счетчики 37 и 38, триггер 39, элемент ИЛИ 40, элемент 41 задержки. Формирователь 30 импульсов синхронизации включает рас- 40 пределитель 42 импульсов, первый 43, второй 44 и третий 45 триггеры, элемент 46 задержки и логический узел 47, содержащий элементы ИЛИ 48-59 (фиг. 2).

Кроме того показаны первый 60, второй 61 и третий 62 входы и выходы 63-66 устройства, а также иллюстрирующие работу устройства ЭЛТ 67 с блоками 68 и 69 отклонения луча, триггером 70, элементом 71 задержки и формирователем 72.

Устройство работает следующим образом.

Сигнал включения с входа 60 устанавливает триггер 39 синхронизатора 1 в единичное состояние. Тогда импульсы с генератора 31 поступают на вход элемента И 33. Импульсы с элемен45

50

55

вает в О триггер 70 гашения. Луч на ЭЛТ 67 опять засвечивается. Таким образом, осуществляется гашение луча во время переходных процессов в устройстве при прохождении сигналов. Увеличивающиеся коды с выходов счетчиков 37 и 38 поступают на входы.регистра 10.

При наличии видеосигнала на входе 61 (равного 1) он поступает через формирователь 2 на элемент И 3 и элемент И 4, с выхода которого сигнал производит запись содержимого счетчиков 37 и 38 в регистр 11 с выдачей на выход 62 устройства. Сигнал с выхода элемента 16 задержки устанавливает в О регистр 10.

Импульс с генератора 31 через элемент И 33 по сигналу с формирователя 2 устанавливает в 1 триггер 8, которьй запрещает прохождение импульсов с генератора 31 через элемент И 36 и разрешает прохождение импульсов с генератора 32 через элемент И 35.

Первый импульс с генератора 32 через элемент И 35 поступает в распределитель 42, с первого выхода которого импульс поступает в логический узел 47. Импульсы с первого, третьего, пятого и седьмого выходов распределителя 42 устанавливают в 1 триггеры 9 и 43 45. Импульс с генератора 32 через элемент И 35, элемент 41 задержки, элемент И 5 и коммутатор 20

2

5

0

херез элемент И 36 поступают на вход счетчика 37 строк, на установку в О счетчика 22 строк и счетчика 23 кадров. Задержанный импульс с элемента И 36 через элемент 18 задержки и элементы ИЛИ 14 и 15 поступает на входы счетчиков 22 и 23. Увеличивающиеся значения кодов счетчиков 22, 23 и 37, 38 поступают на цифроаналоговые преобразователи 24- 27, с выходов которых суммируются на сумматорах 28 и 29, и поступают в блоки 68 и 69 отклонения луча по координате X и Y, луч изменяет свое положение на экране ЭЛТ 67 вдоль координаты ОХ. При этом импульс с генератора 31 поступает через элементы И 33 и ИЛИ 13 и 12 на выход 63 и далее на установку в 1 триггера 70 гашения.

В результате через формирователь 72 сигналов осуществляется гашение луча ЭЛТ. Импульс с элемента ИЛИ 12

0

5

5 через элемент 71 задержки устанавли-

0

5

0

5

вает в О триггер 70 гашения. Луч на ЭЛТ 67 опять засвечивается. Таким образом, осуществляется гашение луча во время переходных процессов в устройстве при прохождении сигналов. Увеличивающиеся коды с выходов счетчиков 37 и 38 поступают на входы.регистра 10.

При наличии видеосигнала на входе 61 (равного 1) он поступает через формирователь 2 на элемент И 3 и элемент И 4, с выхода которого сигнал производит запись содержимого счетчиков 37 и 38 в регистр 11 с выдачей на выход 62 устройства. Сигнал с выхода элемента 16 задержки устанавливает в О регистр 10.

Импульс с генератора 31 через элемент И 33 по сигналу с формирователя 2 устанавливает в 1 триггер 8, которьй запрещает прохождение импульсов с генератора 31 через элемент И 36 и разрешает прохождение импульсов с генератора 32 через элемент И 35.

Первый импульс с генератора 32 через элемент И 35 поступает в распределитель 42, с первого выхода которого импульс поступает в логический узел 47. Импульсы с первого, третьего, пятого и седьмого выходов распределителя 42 устанавливают в 1 триггеры 9 и 43 45. Импульс с генератора 32 через элемент И 35, элемент 41 задержки, элемент И 5 и коммутатор 20

3

поступает на вход (-) счетчика 22 и одновременно через элемент И 6 и коммутатор 21 на вход (-) счетчика 23. Значения кодов счетчиков 22 и 23 поступают на цифроаналоговые преобразователи 26 и 27, преобразующие двоичные коды в аналоговые сигналы, которые складываются на сумматорах 28 и 29 с сигналами, поступающими с циф- роаналоговых преобразователей 24 и 25, и через блоки 68 и 69 отклонения луча по координате X и Y соответственно на отклонение луча ЭЛТ вверх по оси OY и влево по оси ОХ с меньшим дискретом. Первый импульс с генератора 32 через элементы И 35 и ИЛИ 13 и 12 устанавливает триггер 70 гашения в состояние 1, и луч гасится. Задержанный сигнад с элемента 71 за13

держки устанавливает триггер 70 гаше-20 Дов логического узла 47 устанавливания в О, и луч на ЭЛТ засвечивается.

При наличии видеосигнала на входе 61 он поступает на элемент И. 3 и импульсом с генератора 32 через элемент И 35 записывается в регистр 11. Импульсом с элемента 17 задержки содержимое регистра 11 сдвигается вправо на один двоичньш разряд.30

Второй импульс с генератора 32 через элемент И 35 поступает в распределитель 42 импульсов. С второго выхода распределителя 42 импульс поступает в логический узел 47. С первого выхода логического узла 46 подтверждается установка в 1 триггера 43, и импульсами с четвертого.

ют в 1 триггеры 43-45, а импульсом с восьмого выхода распределителя устанавливается в О триггер 9. Импульс с генератора 32 через элемент 25 И 35, элемент 41 задержки, элемент И 5 и коммутатор 20 поступает на вход (-) счетчика 22 и одновременно через элемент И 6 и коммутатор 21 на вход (+) счетчика 23. Значения кодов счет чиков 22 и 23 поступают на цифроаналоговые преобразователи 26 и 27, пре образую01ие двоичные коды в аналоговы сигналы, которые складываются на сум маторах 28 и 29 с сигналами, поступающими с цифроаналоговых преобразователей 24 и 25, и через блоки 68 и 69 соответственно ,на отклонение луча ЭЛТ влево по оси ОХ.и вниз по оси OY с меньшим дискретом. Четвер35

шестого и восьмого выходов триггеры 9, 44 и 45 устанавливаются в О. Второй40 тый импульс с генератора 32 через импульс с генератора 32 через эле- элементы И 35 и ИЛИ 13 и 12 устанав- мент И 35, элемент 41 задержки, элемент И 5, коммутатор 20 и элемент ИЛИ 14 поступает на вход (+) счетчика 22

ливает триггер 70 в состояние .1 , и луч гасится. Задержанный сигнал с элемента 71 задержки устанавливает

и увеличивает содержимое этого счетчи45 триггер 70 гашения в О, и луч ла

ка на единицу, что приводит к отклонению луча вдоль оси ОХ вправо на один дискрет, а через элементы И 35 и ИЛИ 13 и 12 производится гашение и засветка луча ЭЛТ.50

Видеосигнал с входа 61 поступает через формирователь 2 на элемент ИЗ, на другой вход которого поступает импульс с генератора 32 через элементзз И 35. Сигнал с элемента И 3 записывается по второму импульсу с генератора 32 через элемент И 35 в регистр 11, а задержанным импульсом с элемен79854

та 17 задержки производится сдвиг содержимого регистра 11 вправо на один разряд.

Третий импульс с генератора 32 г через элемент И 35 поступает в распределитель 42 импульсов. По третьему импульсу с выхода распределителя 42, как и по второму, производится через соответствующие элементы управление fO отклонением луча вдоль оси ОХ вправо на один дискрет, засветка и гашение луча ЭЛТ, запись видеосигнала в регистр 11.

Четвертый импульс с генератора 32 15 через элемент И 35 поступает в распределитель 42 импульсов, с четвертого выхода которого импульс подается на вход логического узла 47. Импульсы с первого, третьего и пятого выхо

ют в 1 триггеры 43-45, а импульсом с восьмого выхода распределителя устанавливается в О триггер 9. Импульс с генератора 32 через элемент И 35, элемент 41 задержки, элемент И 5 и коммутатор 20 поступает на вход (-) счетчика 22 и одновременно через элемент И 6 и коммутатор 21 на вход (+) счетчика 23. Значения кодов счетчиков 22 и 23 поступают на цифроаналоговые преобразователи 26 и 27, пре- образую01ие двоичные коды в аналоговые сигналы, которые складываются на сумматорах 28 и 29 с сигналами, поступающими с цифроаналоговых преобразователей 24 и 25, и через блоки 68 и 69 соответственно ,на отклонение луча ЭЛТ влево по оси ОХ.и вниз по оси OY с меньшим дискретом. Четвер

тый импульс с генератора 32 через элементы И 35 и ИЛИ 13 и 12 устанав-

тый импульс с генератора 32 через элементы И 35 и ИЛИ 13 и 12 устанав-

ливает триггер 70 в состояние .1 , и луч гасится. Задержанный сигнал с элемента 71 задержки устанавливает

ЭЛТ засвечивается.

При наличии видеосигнала на входе 61 он поступает на элемент И 3 и Импульсом с генератора 32 через элемент И 35 записывается в регистр 11. Импульсом с элемента 17 задержки содержимое регистра 11 сдвигается вправо на один двоичный разряд.

Пятый импульс с генератора 32 через элемент И 35 поступает в распределитель 42 импульсов. По пятому импульсу, как и по четвертому, производится через соответствующие элементы

управление отклонением луча влево по оси ОХ и вниз по оси OY, засветка и гашение луча ЭЛТ, запись видеосигнала в регистр 11.

Шестой импульс с генератора 32 через элемент И 35 поступает в распределитель 42 импульсов. С шестого вьгхода распределителя 42 импульс позадержки, элемент И 6 и коммутатор 2 поступает на вход (-) счетчика 23 и уменьшает содержимое счетчика 23, что приводит к отклонению луча вверх по оси OY на один дискрет, производится засветка и гашение луча ЭЛТ, запись видеосигнала в регистр 11. Девятый импульс с генератора 32

ступает в логический узел 47. Импульс Q через элемент И 35 поступает в расс первого выхода логического узла 47 подтверждает установку в 1 триггера 43, и импульсами с четвертого, шестого и восьмого выходов логического узла 47 производится установка в О триггеров 44, 45 и 9. Шестой импульс с генератора 32 через элемент И 35, элемент 41 задержки, элемент И 5, коммутатор 20 и элемент ИЛИ 14 поступает на вход (-i-) счетчика 22 и увеличивает содержимое этого счетчика на единицу, что приводит к .отклонению луча вдоль рси ОХ вправо на один дискрет, а через элементы И 35 и ИЛИ 13 и 12 производится гашение и засветка луча ЭЛТ,

Видеосигнал с входа 62 поступает через формирователь 2 на элемент И 3, на другой вход которого поступает импульс С генератора 32 через элемент И 35. Сигнал с элемента И 3 записывается по шестому импульсу с генератора 32 через элемент И 35 в регистр 11, а задержанным импульсом с элемента 17 задержки производится сдвиг содержимого регистра 11 вправо на один разряд.

Седьмой импульс с генератора 32 через элемент И 35 поступает в распределитель 42 импульсов. С девятого выхода распределителя 42 импульс поступает в логический узел 47. Импульсы с первого и пятого выходов

15 узла 47 устанавливают в 1 триггеры 43 и 45, а импульсами с четвертог и восьмого выходов логического узла 47 устанавливаются/в О триггеры 9 и 44. Импульс с генератора 32 через

20 элемент И 35, элемент 41 задержки, элемент И 5 и коммутатор 20 поступает на.вход (-) счетчика 22, что приводит к отклонению луча вдоль оси ОХ влево на один дискрет, производит

25 ся засветка и гашение луча ЭЛТ, запись видеосигнала в регистр 11.

Десятый импульс с генератора 32 через элемент И 35 поступает в распределитель 42 импульсов. По десято30 му импульсу с выхода распределителя 42, как и по девятому, производит ся через соответствующие элементы управление отклонением луча вдоль оси ОХ влево на один дискрет, засвет ка и гашение луча ЭЛТ, запись видеосигнала в регистр 11, сдвиг содержимого регистра 11 вправо на один разряд. Импульс с десятого выхода распределителя 42 через элемент 46

35

30 му импульсу с выхода распределителя 42, как и по девятому, производится через соответствующие элементы управление отклонением луча вдоль оси ОХ влево на один дискрет, засветка и гашение луча ЭЛТ, запись видеосигнала в регистр 11, сдвиг содержимого регистра 11 вправо на один разряд. Импульс с десятого выхода распределителя 42 через элемент 46

пределитель 42 импульсов. По седьмо- задержки и группу элементов И 7 раз- му импульсу с выхода распределителя решает прохождение кода с дешифрато- 42, как и по шестому, производится ра 19 на выход 65 устройства, через соответствующие элементы управ- Одиннадцатый импульс с генератоление отклонением луча вдоль оси ОХ вправо на один дискрет, засветка и гашение луча ЭЛТ, запись видеосигнала в регистр 1 1.

Восьмой импульс с генератора 32 через элемент И 35 поступает в распределитель 42 импульсов. С восьмого выхода распределителя 42 импульс поступает в логический узел 47. Импульсами с второго и шестого выхода логического узла производится установка

ра 32 поступает на вход распредели- 45 теля 42, с одиннадцатого выхода которого импульс устанавливает в О регистр 11, а импульсами с второго, четвертого, шестого;, восьмого и девятого выходов логического узла производится установка в О триггеров 8, 9 и 43 - 45. Установка в О триггера 8 приводит к запрещению прохождения импульсов с генератора 32 через элемент И 35, а устройство продолжа50

в О триггеров 43 и 45, и импульса- 55 считывание описанным образом.

При нулевом значении видеосигн лов на входе 62 устройства в любо из десяти тактов в регистр 11 про 0

ми с третьего и седьмого выходов триггеры 44 и 9 устанавливаются в 1. Восьмой импульс с генератора 32 через элемент И 35, элемент 41

задержки, элемент И 6 и коммутатор 21 поступает на вход (-) счетчика 23 и уменьшает содержимое счетчика 23, что приводит к отклонению луча вверх по оси OY на один дискрет, производится засветка и гашение луча ЭЛТ, запись видеосигнала в регистр 11. Девятый импульс с генератора 32

через элемент И 35 поступает в распределитель 42 импульсов. С девятого выхода распределителя 42 импульс поступает в логический узел 47. Импульсы с первого и пятого выходов

узла 47 устанавливают в 1 триггеры 43 и 45, а импульсами с четвертого и восьмого выходов логического узла 47 устанавливаются/в О триггеры 9 и 44. Импульс с генератора 32 через

элемент И 35, элемент 41 задержки, элемент И 5 и коммутатор 20 поступает на.вход (-) счетчика 22, что приводит к отклонению луча вдоль оси ОХ влево на один дискрет, производится засветка и гашение луча ЭЛТ, запись видеосигнала в регистр 11.

Десятый импульс с генератора 32 через элемент И 35 поступает в распределитель 42 импульсов. По десятому импульсу с выхода распределителя 42, как и по девятому, производится через соответствующие элементы управление отклонением луча вдоль оси ОХ влево на один дискрет, засветка и гашение луча ЭЛТ, запись видеосигнала в регистр 11, сдвиг содержимого регистра 11 вправо на один разряд. Импульс с десятого выхода распределителя 42 через элемент 46

задержки и группу элементов И 7 раз- решает прохождение кода с дешифрато- ра 19 на выход 65 устройства, Одиннадцатый импульс с генератора 32 поступает на вход распредели- 45 теля 42, с одиннадцатого выхода которого импульс устанавливает в О регистр 11, а импульсами с второго, четвертого, шестого;, восьмого и девятого выходов логического узла производится установка в О триггеров 8, 9 и 43 - 45. Установка в О триггера 8 приводит к запрещению прохождения импульсов с генератора 32 через элемент И 35, а устройство продолжа50

считывание описанным образом.

При нулевом значении видеосигналов на входе 62 устройства в любом из десяти тактов в регистр 11 произ- 0

водится запись

и сдвиг содержимого регистра 11 вправо на один разряд.

При заполнении счетчиков 37 и 38 сигналы переполнения поступают на вход элемента И 34, где формируется сигнал, который через элемент ИЛИ 40 установит триггер 39 в О, и устройство прекращает считывание. Считывание графической информации может быть 10 вертым управляющим выходом синхрониостановлено в любой момент времени с входа 61 устройства.

При коэффициенте заполнения машиностроительных чертежей 3 - 7% в четыре раза увеличивается точность и быстродействие при уменьшении избыточности передаваемой информации.

Формула изобретения

Устройство для управления считыванием графической информации, содержащее синхронизатор, первый и второй синхронизирующие входы которого являются первым и вторым входами устройства, первый и второй управляюиц1е входы соединены с нулевым и единичным выходами первого триггера, соответственно первый и второй синхронизирующие выходы подключены к входам первого элемента ИЛИ, выход которого является синхронизирующим выходом устройства, а первый и второй информационные выходы синхронизатора подключены к информационным входам первого регистра, установочный вход которого соединен с выходом первого элемента задержки, а выход является первым информационным выходом устройства, второй элемент ИЛИ, входы которого соединены с первым и вторым управляющими выходами синхронизатора, а выход подключен к входу первого элемента ИЛИ, первую группу элементов И, одни входы которых соединены с первым и вторым управляющими йыхо дами синхронизатора соответственно, другие подключены к выходу формирователя входного сигнала, сигнальный

затора, к нулевому входу первого триггера, единичный вход которого соединен с выходом соответствующего элемента И первой группы, к одним

15 входам элементов И третьей группы и к управляющему входу первого коммутатора, информационный вход которого соединен с выходом соответствующего элемента И второй группы, дешифратор,

20 информационный вход которого соединен с выходом второго регистра, а выходы соединены с другими входами элементов И третьей группы, вьпсоды которых являются вторым информацион25 ным выходом устройства, цифроаналого- вые преобразователи первой группы, информационные входы которых подключены к первому информационному выходу синхронизатора, счетчики, устаЯО новочные входы которых подключены к третьему управляющему выходу синхронизатора, а выходы соединены с информационными входами цифроаналоговых преобразователей второй группы, выходы которых подключены к одним информационным входам соответствующих сумматоров, другие информационные входы которых соединены с. выходами соответствующих цифроаналоговых преобразова4Q телей -первой группы, при этом синхронизирующий вход первого регистра подключен к выходу соответствующего элемента И первой группы, а вычитающий вход первого счетчика соединен

g с выходом первого коммутатора, о т35

личающееся тем, что, с целью повышения точности и быстродействия устройства, оно содержит второй триггер, единичньш и нулевой входы вход которого является информационным 50 которого соединены с первым и вторым входом устройства, второй регистр, управляющими выходами формирователя

тактовых импульсов, второй коммутатор, информационный вход которого подключен к выходу соответствующего

информационный вход которого соединен с выходом соответствующего элемента И первой группы, а синхронизирующий вход подключен к третьему управ- 55 элемента И второй группы, управляющий вход соединен с единичным выходом второго триггера, а выход подключен к вычитающему входу второго счетчика, третий элемент задержки, вход

ляющему выходу синхронизатора, соединенному с входом второго элемента задержки, выход которого подключен к входу управления сдвигом второго

регистра, формирователь тактовых импульсов, счетный вход которого соединен, с вторым управляющим выходом синхронизатора, а синхронизирующие выходы подключены к установочному входу второго регистра, к одним входам элементов И второй группы, другие входы которых соединены с четзатора, к нулевому входу первого триггера, единичный вход которого соединен с выходом соответствующего элемента И первой группы, к одним

входам элементов И третьей группы и к управляющему входу первого коммутатора, информационный вход которого соединен с выходом соответствующего элемента И второй группы, дешифратор,

информационный вход которого соединен с выходом второго регистра, а выходы соединены с другими входами элементов И третьей группы, вьпсоды которых являются вторым информационным выходом устройства, цифроаналого- вые преобразователи первой группы, информационные входы которых подключены к первому информационному выходу синхронизатора, счетчики, установочные входы которых подключены к третьему управляющему выходу синхронизатора, а выходы соединены с информационными входами цифроаналоговых преобразователей второй группы, выходы которых подключены к одним информационным входам соответствующих сумматоров, другие информационные входы которых соединены с. выходами соответствующих цифроаналоговых преобразователей -первой группы, при этом синхронизирующий вход первого регистра подключен к выходу соответствующего элемента И первой группы, а вычитаюий вход первого счетчика соединен

с выходом первого коммутатора, о т

элемента И второй группы, управляющий вход соединен с единичным выходом второго триггера, а выход подключен к вычитающему входу второго счетчика, третий элемент задержки, вход

5135798510

которого подключен к третьему управ- го коммутаторов соответственно и к

ляющему .выходу синхронизатора, и элементы ИЛИ группы, входы которых

подключены к вькодам первого и в торо- дами соответствуюпщх счетчиков.

выходу третьего элемента задержки, а выходы соединены с суммируюпщми вхо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления считыванием графической информации | 1986 |

|

SU1334170A1 |

| Устройство для управления считыванием графической информации | 1984 |

|

SU1343430A1 |

| Устройство для управления считыванием графической информации | 1985 |

|

SU1325535A1 |

| Устройство для управления считыванием графической информации | 1987 |

|

SU1439639A1 |

| Устройство для управления считыванием графической информации | 1987 |

|

SU1552207A1 |

| Устройство для считывания графической информации | 1982 |

|

SU1164752A1 |

| Устройство для считывания графической информации | 1984 |

|

SU1290378A1 |

| Устройство для считывания графической информации | 1988 |

|

SU1522257A1 |

| Устройство для управления считыванием графической информации | 1990 |

|

SU1725241A1 |

| Устройство для управления считыванием графической информации | 1989 |

|

SU1631564A1 |

Изобретение относится к автоматике, в частности к устройствам для управления считыванием графической информации, и может быть использовано в системах автоматизированного проектирования. Цель изобретения состоит в повьшении точности и быстродействии устройства. Поставленная цель достигается путем сокращения избыточности считьшаемой дискретной информации за счет циклического формирования микрорастров по координатам Х, Y в области изображений, несущих полезную информацию. 2 ил.

| Устройство для считывания графической информации | 1982 |

|

SU1164752A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления считыванием графической информации | 1985 |

|

SU1325535A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-07—Публикация

1985-03-18—Подача