(21)4120823/2А-24

(22)13.06,86

(46) 07.02.88.ВЮЛ. № 5

(71)Челябинский политехнический институт им.Ленинского комсомола

(72)Л.И.Цытович

(53)681.335 (088.8)

(56) Авторское свидетельство СССР № 1206816, кл. G 06 G 7/12, 1984.

Авторское свидетельство СССР № 1260975, кл. G 06 G 7/12, 1985.

(54)РАЗВЕРТЫВАЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к усилительным устройствам с широтно-им- пульсным преобразованием сигнала и

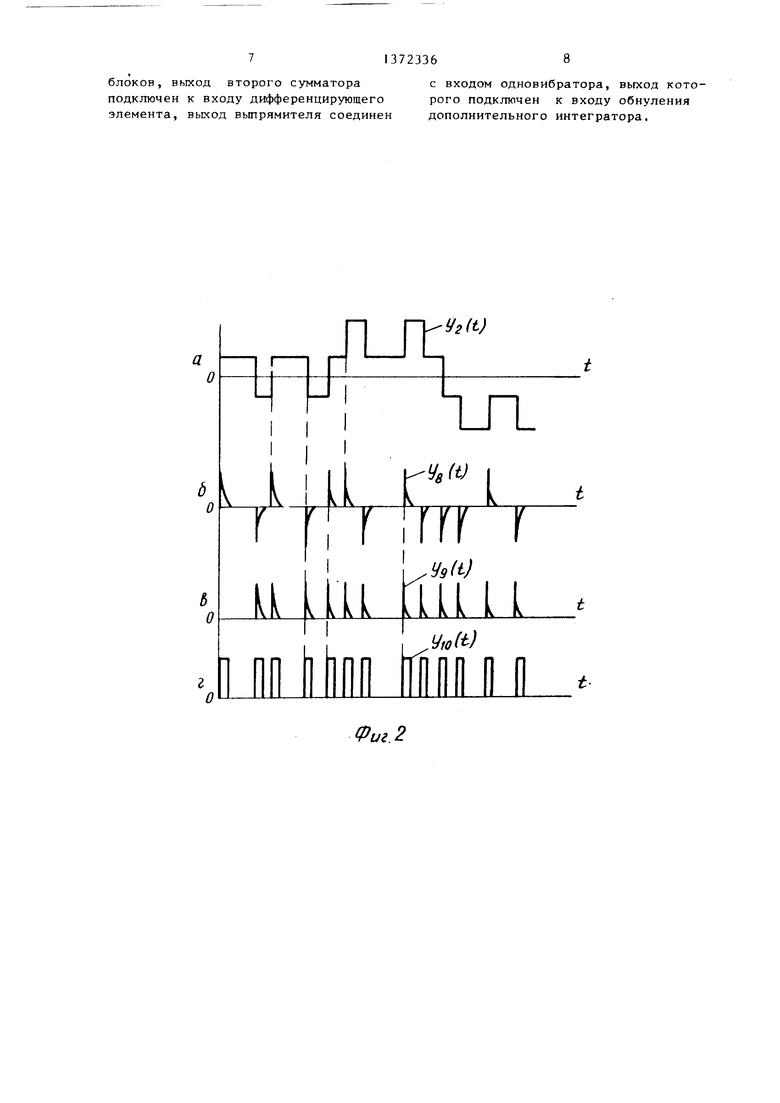

может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повьппение точности. Развертьшающий преобразователь содержит первый и второй сумматоры 1 и 2, ш тегратор 3, дoпoлни-. тельный интегратор 4, релейные блоки 5,амплитудный модулятор 6, пороговый элемент 7, дифференцирующий элемент 8, вьшрямитель 9, одновибратор 10, вход 11, выход 12. Развертьшающий преобразователь работает в автоколебательном режиме, среднее значение широтно-импульсного выходного сигнала пропорционально входному сигналу . 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Развертывающий операционный усилитель | 1985 |

|

SU1260975A1 |

| Развертывающий усилитель | 1988 |

|

SU1508245A2 |

| Многозонный развертывающий преобразователь | 1987 |

|

SU1418765A1 |

| Развертывающий преобразователь | 1986 |

|

SU1332336A1 |

| Множительное устройство | 1981 |

|

SU955104A1 |

| Развертывающий операционный усилитель | 1983 |

|

SU1088014A1 |

| Устройство для управления вентильным преобразователем | 1985 |

|

SU1288864A1 |

| МНОГОЗОННЫЙ РАЗВЕРТЫВАЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ДЛЯ ПЕРЕДАЧИ ЛОГИЧЕСКИХ ДАННЫХ ПО ОДНОПРОВОДНОЙ ЛИНИИ СВЯЗИ | 2001 |

|

RU2206922C2 |

| Развертывающий операционный усилитель | 1984 |

|

SU1206815A1 |

| Развертывающий усилитель | 1983 |

|

SU1108468A1 |

(Л

С

00 00 О5

Изобретение относится к усилительным устройствам с широтно-импульсным преобразованием сигнала и может быть использовано в аналоговых вычислительных машинах.

Целью изобретения является повышение точности.

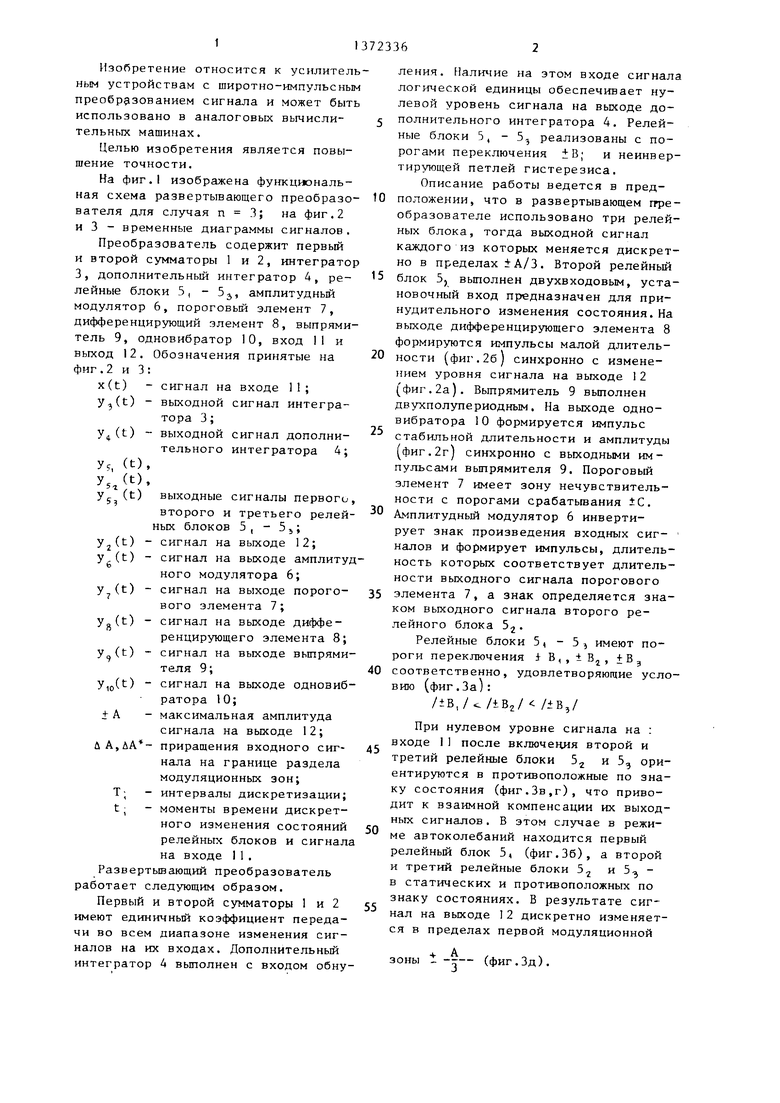

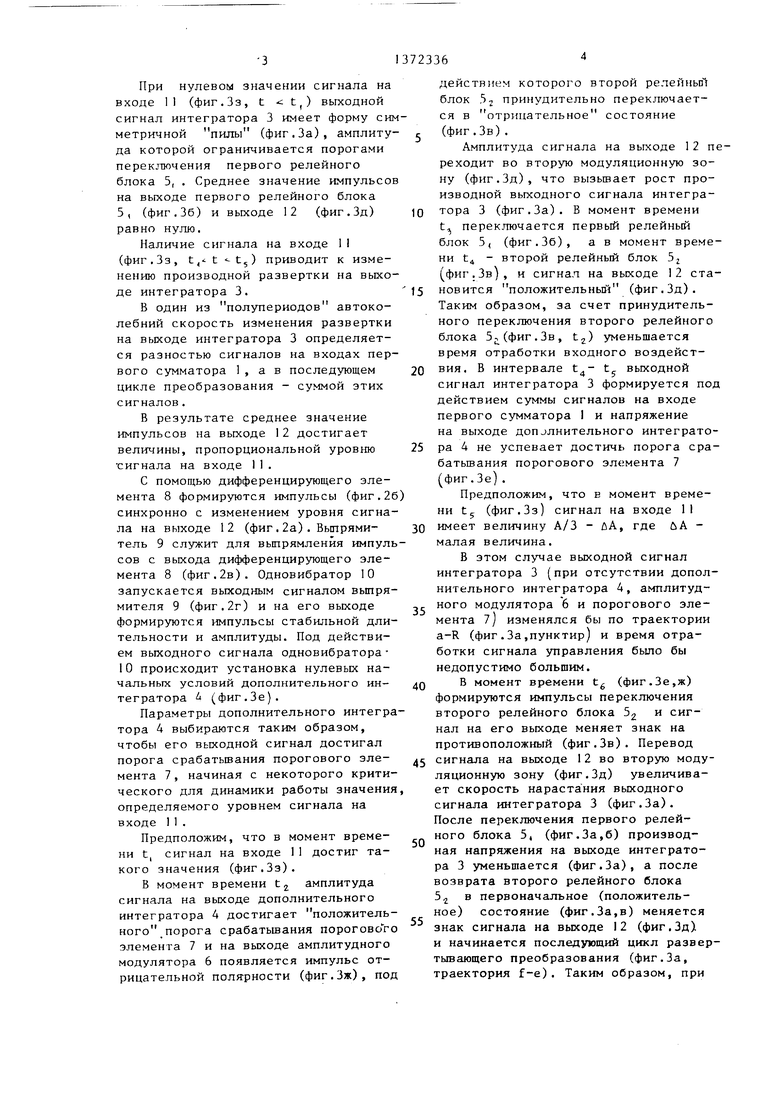

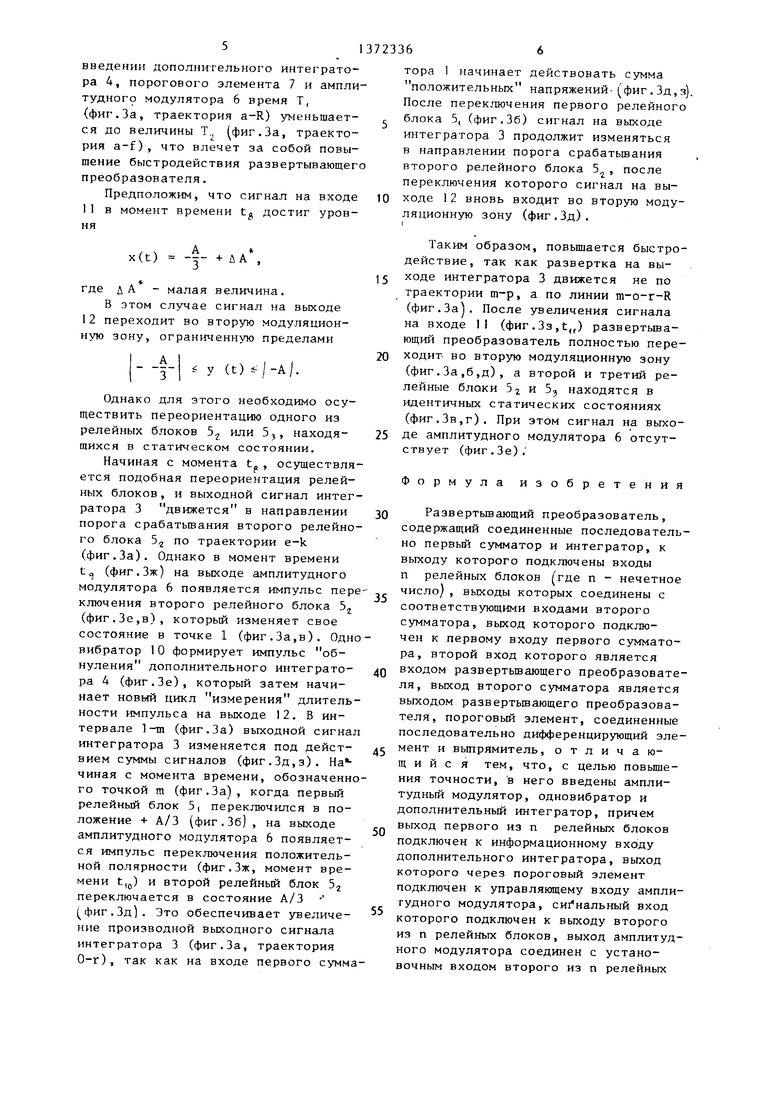

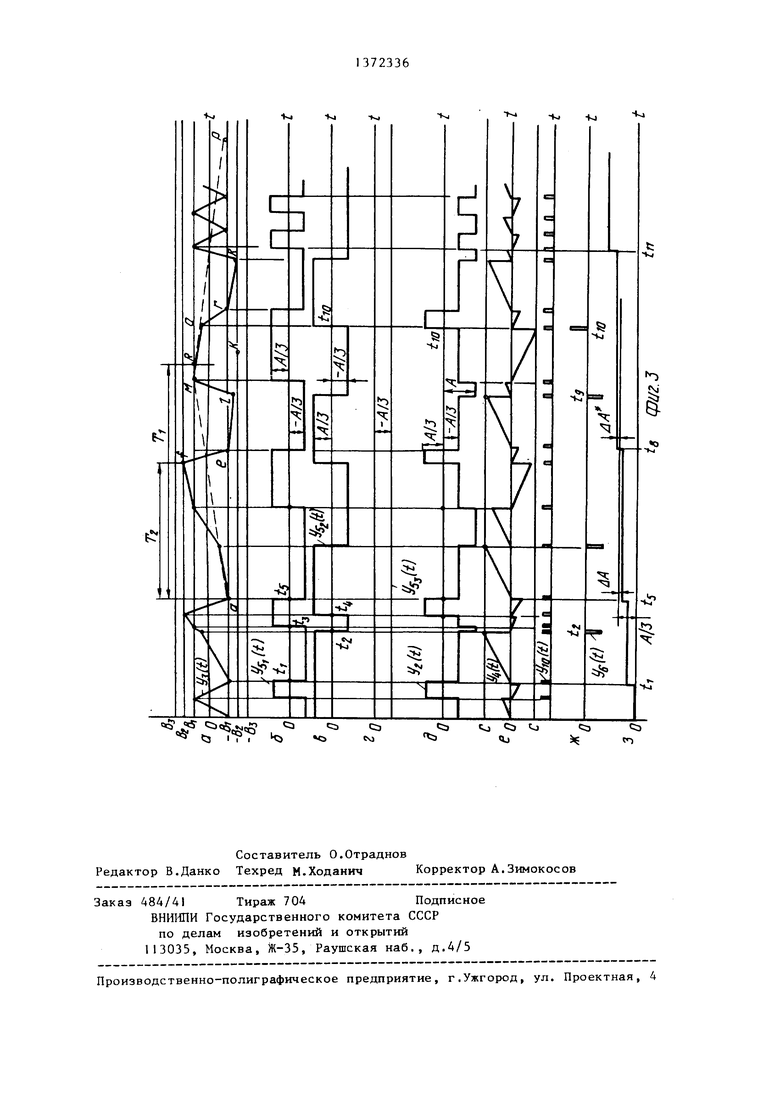

На фиг.I изображена функциональная схема развертывающего преобразователя для случая п 3; на фиг.2 и 3 - временные диаграммы сигналов.

Преобразователь содержит первьй и второй сумматоры 1 и 2, интегратор 3, дополнительный интегратор 4, релейные блоки 5, - 5,,, амплитудньй модулятор 6, пороговый элемент 7, дифференцирующий элемент 8, выпрямитель 9, одновибратор 10, вход И и выход 12. Обозначения принятые на фиг.2 и 3:

x(t) - сигнал на входе 11;

y(t) - выходной сигнал интегратора 3;

у.(t) - выходной сигнал дополниУ., (t),

- .Iтельного интегратора 4;

5

y,(t) yjt)

выходные сигналы первого, второго и третьего релейных блоков 5 , - 5,;

-сигнал на выходе 12;

-сигнал на выходе амплитудного модулятора 6;

у (t) - сигнал на выходе порогового элемента 7; у (t) - сигнал на выходе дифференцирующего элемента 8; у (t) - сигнал на выходе выпрямителя 9; y,p(t) - сигнал на выходе одновибратора 10; ± А - максимальная амплитуда

сигнала на выходе 12; йА, приращения входного сигнала на границе раздела модуляционных зон; Т; - интервалы дискретизации; t; - моменты времени дискретного изменения состояний релейных блоков и сигнала на входе 11.

Развертьшающий преобразователь аботает следующим образом.

Первый и второй сумматоры 1 и 2 меют единичный коэффициент передаи во всем диапазоне изменения сигалов на их входах. Дополнительный нтегратор Д выполнен с входом обну

5

0

5

0

5

0

5

0

ления. Наличие на этом входе сигнала логической единицы обеспечивает нулевой уровень сигнала на выходе дополнительного интегратора 4. Релейные блоки 5, - 5 реализованы с порогами переключения ±В; и неинвертирующей петлей гистерезиса.

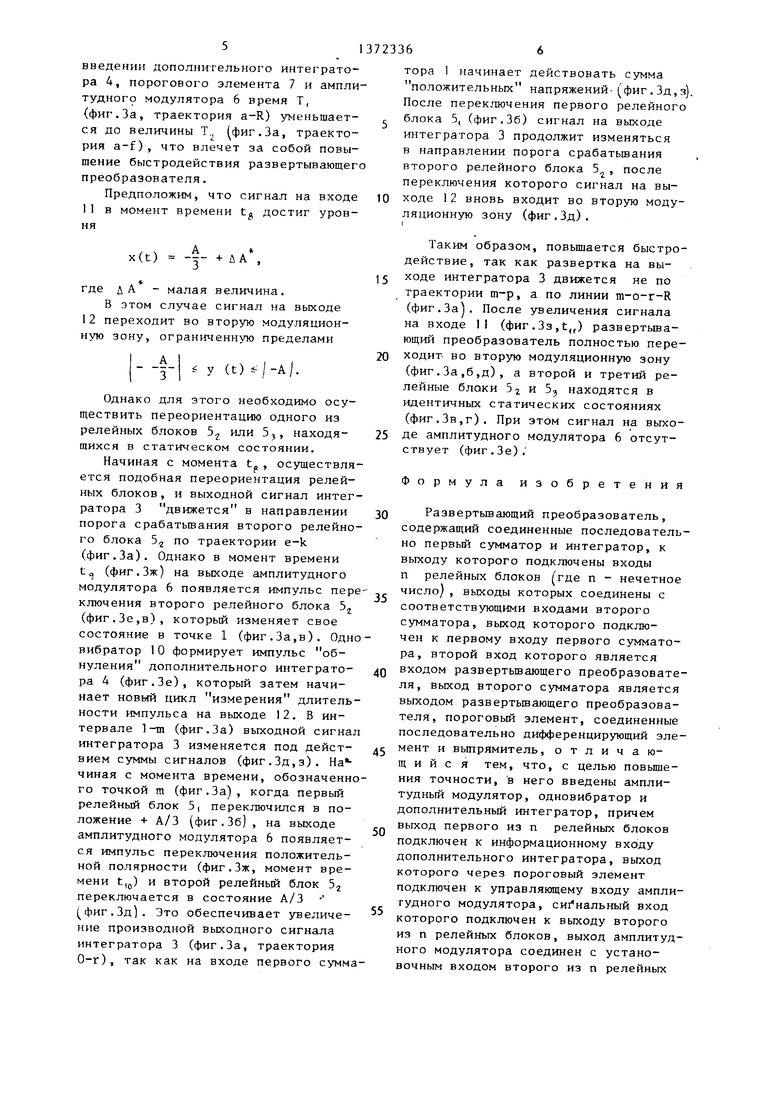

Описание работы ведется в предположении, что в развертывающем ггре- образователе использовано три релейных блока, тогда выходной сигнал каждого из которых меняется дискретно в пределах ±А/3. Второй релейный блок 5j вьшолнен двухвходовым, установочный вход предназначен для принудительного изменения состояния. На выходе дифференцирующего элемента 8 формируются импульсы малой длительности (фиг.26 ) синхронно с изменением уровня сигнала на выходе 12 (фиг.2а). Вьшрямитель 9 выполнен двухполупериодным. На выходе одно- вибратора 10 формируется импульс стабильной длительности и амплитуды (фиг.2г) синхронно с выходными импульсами вьшрямителя 9. Пороговый элемент 7 имеет зону нечувствительности с порогами срабатьшания iC. Амплитудный модулятор 6 инвертирует знак произведения входных сиг- налов и формирует импульсы, длительность которых соответствует длительности выходного сигнала порогового элемента 7, а знак определяется знаком выходного сигнала второго релейного блока Sj.

Релейные блоки 5, - 5, имеют пороги переключения f В , , ± В, , ± В соответственно, удовлетворяющие условию (фиг.За):

/±В,/. /±Вг/ /1В,/

При нулевом уровне сигнала на : входе 11 после включения второй и третий релейные блоки 5 и 5, ориентируются в противоположные по знаку состояния (фиг.Зв.г), что приводит к взаимной компенсации их выходных сигналов. В этом случае в режиме автоколебаний находится первый релейньй блок 5, (фиг.36), а второй

и третий релейные блоки 5,

и 5,

в статических и противоположных по знаку состояниях. В результате сигнал на выходе 12 дискретно изменяется в пределах первой модуляционной

зоны 1 --- (фиг.Зд).

При нулевом значении сигнала на входе 11 (фиг.Зз, t 11 ) выходной сигнал интегратора 3 имеет форму симметричной пилы (фиг.За), амплиту- да которой ограничивается порогами переключения первого релейного блока 5, . Среднее значение импульсов на выходе первого релейного блока 5, (фиг.Зб) и выходе 12 (фиг.Зд) равно нулю.

Наличие сигнала на входе 1 I (фиг .Зз, ,) приводит к изменению производной развертки на выходе интегратора 3.

В один из полупериодов автоко- лебний скорость изменения развертки на выходе интегратора 3 определяется разностью сигналов на входах первого сумматора 1, а в последующем цикле преобразования - суммой этих сигналов,

В результате среднее значение импульсов на выходе 12 достигает величины, пропорциональной уровню сигнала на входе 1 1 .

С помощью дифференцирующего элемента 8 формируются импульсы (фиг.2б синхронно с изменением уровня сигнала на выходе 12 (фиг.2а). Выпрями- тель 9 служит для выпрямления импульсов с выхода дифференцирующего элемента 8 (фиг.2в). Одновибратор 10 запускается выходным сигналом выпрямителя 9 (фиг.2г) и на его выходе формируются импульсы стабильной длительности и амплитуды. Под действием выходного сигнала одновибратора 10 происходит установка нулевых начальных условий дополнительного ин- тегратора А (фиг.Зе).

Параметры дополнительного интегратора 4 выбираются таким образом, чтобы его выходной сигнал достигал порога срабатьшания порогового эле- мента 7, начиная с некоторого критического для динамики работы значения определяемого уровнем сигнала на входе 11.

Предположим, что в момент време- ни t, сигнал на входе 11 достиг такого значения (фиг.Зз).

В момент времени t амплитуда сигнала на выходе дополнительного интегратора 4 достигает положительного порога срабатьшания порогового элемента 7 и на выходе амплитудного модулятора 6 появляется импульс отрицательной поля-рности (фиг.Зж), под

5

0

5

0 5 д

5

действием которого второй релейньп блок З принудительно переключается в отрицательное состояние (фиг.Зв).

Амплитуда сигнала на выходе 12 переходит во вторую модуляционную зону (фиг.Зд), что вызьшает рост производной выходного сигнала интегратора 3 (фиг.За). В момент времени t переключается первый релейный блок 5, (фиг.Зб), а в момент времени t - второй релейный блок 5 (фиг.Зв), и сигнал на выходе 12 становится положительньп (фиг.Зд). Таким образом, за счет принудительного переключения второго релейного блока 5(фиг.Зв, t) уменьшается время отработки входного воздействия. В интервале t выходной сигнал интегратора 3 формируется под действием суммы сигналов на входе первого сумматора I и напряжение на выходе допJлнитeльнoгo интегратора 4 не успевает достичь порога срабатьшания порогового элемента 7 (фиг.Зе).

Предположим, что в момент времени tj (фиг.Зз) сигнал на входе 11 имеет величину А/3 - дА, где uA - малая величина.

В этом случае выходной сигнал интегратора 3 (при отсутствии дополнительного интегратора 4, амплитудного модулятора 6 и порогового элемента 7 изменялся бы по траектории a-R (фиг.За,пунктир) и время отработки сигнала управления было бы недопустимо большим.

В момент времени t (фиг.3е,ж) формируются импульсы переключения второго релейного блока 52 и сигнал на его выходе меняет знак на противоположный (фиг.Зв). Перевод сигнала на выходе 12 во вторую модуляционную зону (фиг.Зд) увеличивает скорость нарастания выходного сигнала интегратора 3 (фиг.За). После переключения первого релейного блока 5, (фиг.За,б) производная напряжения на выходе интегратора 3 уменьшается (фиг.За), а после возврата второго релейного блока 52 в первоначальное (положительное) состояние (фиг.За,в) меняется знак сигнала на выходе 12 (фиг.Зд) и начинается последующий цикл развертывающего преобразования (фиг.За, траектория f-e). Таким образом, при

введении дополнительного интегратора 4, порогового элемента 7 и амплитудного модулятора 6 время Т, (фиг,За, траектория a-R) уменьшается до величины Т, фиг.За, траектория a-f) , что влечет за собой повышение быстродействия развертывающего преобразователя.

Предположим, что сигнал на входе 11 в момент времени tg достиг уровня

x(t)

-f-.AA

где дА - малая величина.

В этом случае сигнал на выходе 12 переходит во вторую модуляционную зону, ограниченную пределами

А

з

У (t) -А

Однако для этого необходимо осуществить переориентацию одного из релейных блоков Ь или 5,, находящихся в статическом состоянии.

Начиная с момента t, осуществляется подобная переориентация релейных блоков, и выходной сигнал интегратора 3 движется в направлении порога срабатьюания второго релейного блока 5 по траектории e-k (фиг,За), Однако в момент времени (фиг,3ж) на выходе амплитудного модулятора 6 появляется импульс переключения второго релейного блока 5 (фиг,3е,в), который изменяет свое состояние в точке 1 (фиг,3а,в). Одно вибратор 10 формирует импульс обнуления дополнительного интегратора 4 (фиг,3е), который затем начинает новый цикл измерения длительности импульса на выходе 12. В интервале 1-т (фиг.За) выходной сигнал интегратора 3 изменяется под действием суммы сигналов (фиг.3д,з). чиная с момента времени, обозначенно го точкой m (фиг.За), когда первый релейный блок 5, переключился в положение + А/3 (фиг.Зб), на выходе амплитудного модулятора 6 появляется импульс переключения положительной полярности (фиг.Зж, момент времени t,(j) и второй релейный блок 52 переключается в состояние А/3 (фиг.Зд). Это обеспечивает увеличение производной выходного сигнала интегратора 3 (фиг.За, траектория 0-г), так как на входе первого сумм

тора 1 начинает действовать сумма положительных напряжений- (фиг.3д,з). После переключения первого релейного

блока 5, (фиг.Зб) сигнал на выходе интегратора 3 продолжит изменяться в направлении порога срабатьшания второго релейного блока 5, после переключения которого сигнал на выходе 12 вновь входит во вторую модуляционную зону (фиг.Зд), I

Таким образом, повышается быстродействие, так как развертка на выходе интегратора 3 движется не по траектории т-р, а по линии m-o-r-R (фиг,За). После увеличения сигнала на входе II (фиг.Зз,С,) развертьша- ющий преобразователь полностью переходит во вторую модуляционную зону (фиг,За ,б,д), а второй и третий релейные блоки 5j и БЗ находятся в идентичных статических состояниях (фиг,3в,г). При этом сигнал на выходе амплитудного модулятора 6 отсутствует (фиг,3е).

Формула изобретения

Развертьшающий преобразователь, содержащий соединенные последовательно первый сумматор и интегратор, к выходу которого подключены входы п релейных блоков (где п - нечетное число), выходы которых соединены с соответствующими входами второго сумматора, выход которого подключен к первому входу первого сумматора, второй вход которого является

входом развертьшающего преобразователя, выход второго сумматора является выходом развертьшающего преобразователя, пороговый элемент, соединенные последовательно дифференцирующий элемент и выпрямитель, отличающийся тем, что, с целью повышения точности, в него введены амплитудный модулятор, одновибратор и дополнительный интегратор, причем выход первого из п релейных блоков подключен к информационному входу дополнительного интегратора, выход которого через пороговый элемент подключен к управляющему входу амплитудного модулятора, си1 нальный вход которого подключен к выходу второго из п релейных блоков, выход амплитудного модулятора соединен с установочным входом второго из п релейных

блоков, выход второго сумматора подключен к входу дифференцирующего элемента, выход выпрямителя соединен

с входом одновибратора, выход которого подключен к входу обнуления дополнительного интегратора,

Фиг 2

Авторы

Даты

1988-02-07—Публикация

1986-06-13—Подача