Bxri

i

X

fiMxaf

00

О)

ю

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный усилитель мощности | 1987 |

|

SU1510069A1 |

| Операционный усилитель с защитой выхода от перегрузки | 1981 |

|

SU1020971A1 |

| Усилитель | 1990 |

|

SU1716597A1 |

| Усилитель мощности | 1981 |

|

SU1197051A1 |

| Усилитель мощности | 1986 |

|

SU1406723A1 |

| Усилитель мощности | 1986 |

|

SU1376232A1 |

| Усилитель мощности | 1986 |

|

SU1350818A1 |

| Усилитель мощности | 1989 |

|

SU1739475A1 |

| Двухтактный усилитель мощности | 1982 |

|

SU1084957A1 |

| Усилитель мощности | 1984 |

|

SU1220105A1 |

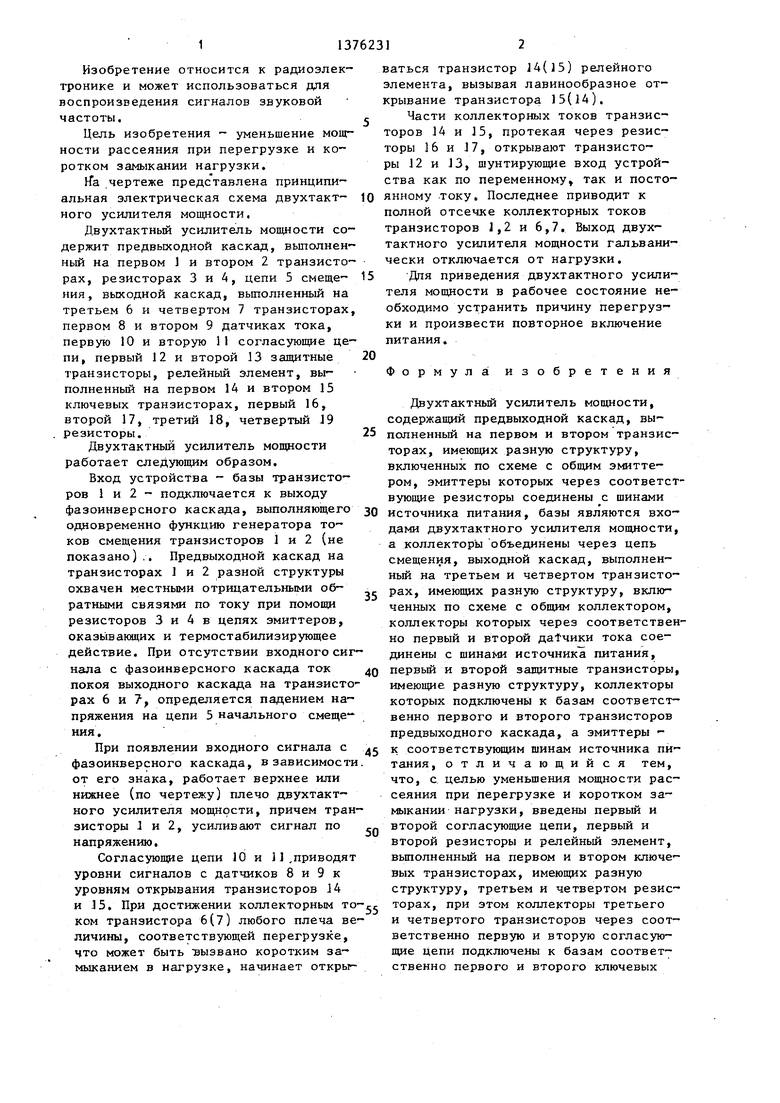

Изобретение м.б. использовано для воспроизведения сигналов звуковой частоты. Цель изобретения - уменьшение мощности рассеяния при перегруз- . ке и коротком замыкании нагрузки. У-ль содержит предвыходной каскад,выполненный на транзисторах (Т) 1 и 2, резисторах 3 и 4, цепи 5 смещения, выходной каскад, выполненный на Т 6 и 7, датчиках 8 и 9 тока, защитные Т 12 и 13. Вновь введены согласующие цепи 10 и II, резисторы 16 и 17 и релейный эл-т, выполненный на ключевых Т 14 и 15, имеющих разную структуру, резисторах 18 и 19. 1 ил.

Изобретение относится к радиоэлектронике и может использоваться для воспроизведения сигналов звуковой частоты.

Цель изобретения уменьшение мощности рассеяния при перегрузке и коротком замыкашии нагрузки.

ЬГа чертеже представлена принципиальная электрическая схема двухтактного усилителя мощности,

Двухтактньй усилитель мощности содержит предвыходной каскад, вьтолнен- ный на первом и втором 2 транзисторах, резисторах 3 и 4, цепи 5 смеще- 15 НИН, выходной каскад, выполненный на

25

30

третьем 6 и четвертом 7 транзисторах, первом 8 и втором 9 датчиках тока, первую 10 и вторую 11 согласующие цепи, первый 12 и второй 13 защитные 20 транзисторы, релейный элемент, выполненный на первом 14 и втором J5 ключевых транзисторах, первый 16,

второй 17, третий 18, четвертый J9 резисторы.

Двухтактный усилитель мощности работает следующим образом.

Вход устройства - базы транзисторов 1 и 2 - подключается к выходу фазоинаерсного каскада, выполняющего одновременно функцию генератора токов смещения транзисторов 1 и 2 (не показано) .. Предвыходной каскад на транзисторах 1 и 2 разной структуры охвачен местными отрицательньми обратными связями по току при помощи резисторов 3 и 4 в цепях эмиттеров, оказывакицих и термостабилизирующее действие. При отсутствии входного сигнала с фазоинверсного каскада ток Q покоя выходного каскада на транзисторах 6 и 7, определяется падением напряжения на цепи 5 начального смещения.

При появлении входного сигнала с фазоинверсного каскада, в зависимости от его знака, работает верхнее или нижнее (по чертежу) плечо двухтактного усилителя мощности, причем тран13762312

ваться транзистор 14(15) релейного элемента, вызывая лавинообразное открывание транзистора 15(14).

Части коллекторных токов транзисторов J4 и 15, протекая через резисторы 16 и J7, открывают транзисторы 12 и J3, шунтирующие вход устройства как по переменному так и постоянному току. Последнее приводит к полной отсечке коллекторных токов транзисторов 1,2 и 6,7. Выход двухтактного усилителя мощности гальванически отключается от нагрузки.

Для приведения двухтактного усилителя мощности в рабочее состояние необходимо устранить причину перегрузки и произвести повторное включение питания.

10

35

45

Формула изобретения

Двухтактньй усилитель мощности, содержащий предвыходной каскад, выполненный на первом и втором транзисторах, имеющих разную структуру, включенных по схеме с общим эмиттером, эмиттеры которых через соответствующие резисторы соединены с щинами источника питания, базы являются входами двухтактного усилителя мощности, а коллекторы объединены через цепь смещения, выходной каскад, выполненный на третьем и четвертом транзисторах, имеющих разную структуру, включенных по схеме с общим коллектором, коллекторы которых через соответственно первый и второй да1чики тока соединены с щинами источника питания, первый и второй защитные транзисторы, имеющие разную структуру, коллекторы которых подключены к базам соответственно первого и второго транзисторов предвыходного каскада, а эмиттеры - к соответствующим щинам источника питания, отличающийся тем, что, с цепью уменьшения мощности рассеяния при перегрузке и коротком замыкании нагрузки, введены первый и второй согласующие цепи, первый и второй резисторы и релейный элемент, выполненньй на первом и втором ключе - вых транзисторах, имеющих разную структуру, третьем и четвертом резисвисторы J и 2, усиливают сигнал по напряжению.

Согласующ ие цепи 10 и II,приводят уровни сигналов с датчиков 8 и 9 к уровням открывания транзисторов J4

и J5. При достижении коллекторным то-гг торах, при этом коллекторы третьего

ком транзистора 6(7) любого плеча величины, соответствующей перегрузке, что может быть вызвано коротким замыканием в нагрузке, начинает открыи четвертого транзисторов через соот ветственно первую и вторую согласующие Цепи подключены к базам соответственно первого и второго ключевых

5

0

0

Q

5

5

0

Формула изобретения

Двухтактньй усилитель мощности, содержащий предвыходной каскад, выполненный на первом и втором транзисторах, имеющих разную структуру, включенных по схеме с общим эмиттером, эмиттеры которых через соответствующие резисторы соединены с щинами источника питания, базы являются входами двухтактного усилителя мощности, а коллекторы объединены через цепь смещения, выходной каскад, выполненный на третьем и четвертом транзисторах, имеющих разную структуру, включенных по схеме с общим коллектором, коллекторы которых через соответственно первый и второй да1чики тока соединены с щинами источника питания, первый и второй защитные транзисторы, имеющие разную структуру, коллекторы которых подключены к базам соответственно первого и второго транзисторов предвыходного каскада, а эмиттеры - к соответствующим щинам источника питания, отличающийся тем, что, с цепью уменьшения мощности рассеяния при перегрузке и коротком замыкании нагрузки, введены первый и второй согласующие цепи, первый и второй резисторы и релейный элемент, выполненньй на первом и втором ключе - вых транзисторах, имеющих разную структуру, третьем и четвертом резиси четвертого транзисторов через соответственно первую и вторую согласующие Цепи подключены к базам соответственно первого и второго ключевых

транзисторов, коллекторы которых че-соответственно первый и второй ре- рез соответственно третий и четвертыйзисторы подключены к Коллекторам со- резисто)ы подключены к базам соответ-ответственно второго и первого ключе- ственно второго и первого ключевых ,вых транзисторов, эмиттеры которых транзисторов, причем базы первого иподключены к соответствующим шинам второго защитных транзисторов черезисточника питания.

| Патент США № 3995229,кл.ЗЗО-17, опублик | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

Авторы

Даты

1988-02-23—Публикация

1985-05-30—Подача