и

(Л

00

sj

00

00

информации о топологии сети из памяти. Устройство содержит .матрицу 1 из Рлр моделей дуг, где Р - количество вершин в моделируемой сети, причем каждая модель дуги содержит элемент И 2 и триггер 3, две группы из Р триггеров 4 и 5, группу из Р элементов ИЛИ-НЕ 6, группу из Р элементов И 7, шифратор 8, ключ 9, два элемента ИЛИ 10 и 11, элемент НЕ 12, два дешифратора 13 и 14, счечик 15, вход 16 пуска, вход 17 задания номера завершенной модели, вход 18 сигнала прерывания работы, тактовьш вход 19, выходы 20 признака разрешения пуска, информационный выход 21, выход 22 признака окончания работы. Использование графового представления сети, в котором элементарным моделям соответствуют не

77868

дуги, а вершины, позволит значительно упростить задание топологии сети, применив для реализации этой функции матрицу сети, упростить логику функционирования устройства при реализации таких функций, как отметка завершения функционирования элементарных моделей, определение элементарных моделей, допустимых для включения в текущий момент времени по условию завершенности функционирования всех предшествующих элементарных моделей, включение элементарных моделей, а также упростить формирование сигнала о завершении моделирования, что, в конечном итоге, позволяет реализовать все функции устройства прототипа при повьш1ении. быстродействия устройства и сокращении оборудования. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения максимальных путей в графах | 1984 |

|

SU1280380A2 |

| УСТРОЙСТВО ДЛЯ АНАЛИЗА СВЯЗНОСТИ ГРАФА | 1991 |

|

RU2006932C1 |

| Устройство для определения кратчайшего пути на графе | 1983 |

|

SU1134944A1 |

| Устройство для разбиения графа на подграфы | 1986 |

|

SU1332329A1 |

| Устройство для анализа параметров сети | 1986 |

|

SU1548793A1 |

| Устройство для распределения заданий процессорам | 1980 |

|

SU940164A1 |

| Устройство для исследования путей в графе | 1986 |

|

SU1348850A1 |

| Устройство для моделирования графов | 1986 |

|

SU1322306A1 |

| Устройство для исследования графов | 1987 |

|

SU1411773A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1983 |

|

SU1161951A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислительных устройств для моделирования сетевых задач. Целью изобретения является повышение быстродействия устройства за счет исключения времени считывания

1

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислительных устройств для моделирования сетевых задач.

Целью изобретения является повы- иение быстродействия устройства за Ьчет исключения времени считывания информации о топологии из блоков памяти.

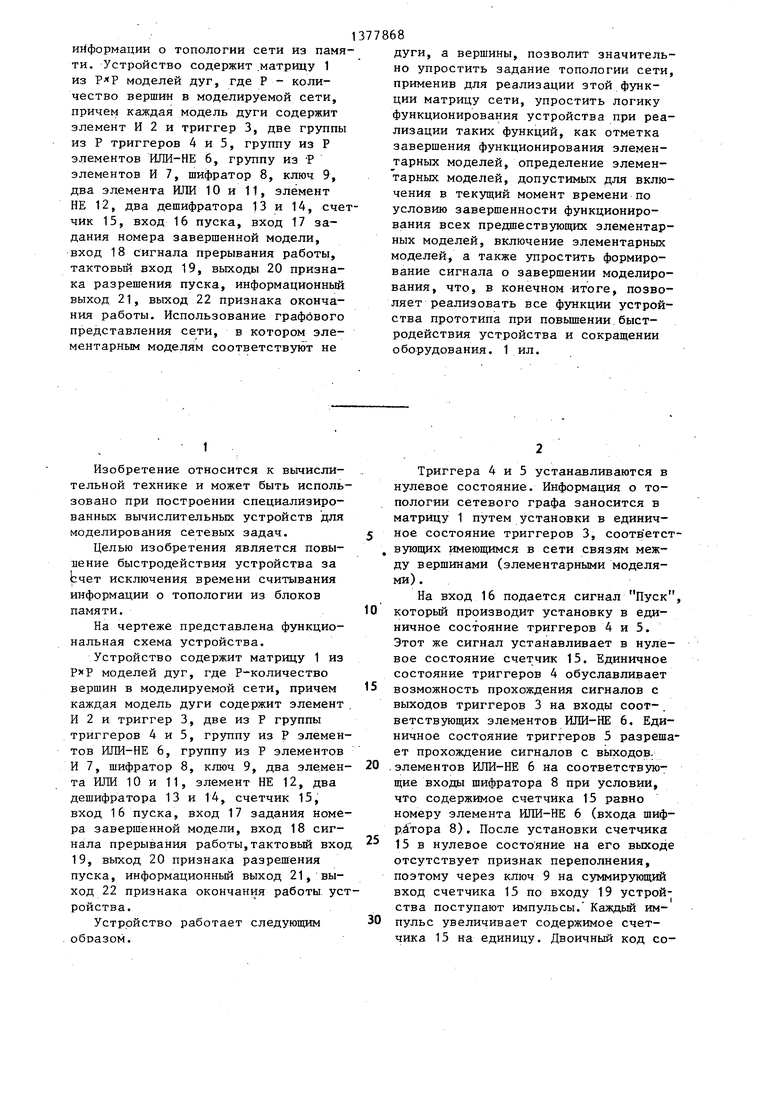

На чертеже представлена функциональная схема устройства.

Устройство содержит матрицу 1 из РхР моделей дуг, где Р-количество вершин в моделируемой сети, причем каждая модель дуги содержит элемент И 2 и триггер 3, две из Р группы триггеров 4 и 5, группу из Р элементов ИЛИ-НЕ 6, группу из Р элементов И 7, шифратор 8, ключ 9, два элемента ИЛИ 10 и 11, элемент НЕ 12, два дешифратора 13 и 14, счетчик 15, вход 16 пуска, вход 17 задания номера завершенной модели, вход 18 сигнала прерывания работы,тактовый вход 19, выход 20 признака разрешения пуска, информационный выход 21, выход 22 признака окончания работы устройства.

Устройство работает следуюш 1М образом.

Триггера 4 и 5 устанавливаются в нулевое состояние. Информация о топологии сетевого графа заносится в матрицу 1 путем установки в единичное состояние триггеров 3, соотв етст- вующих имеющимся в сети связям между вершинами (элементарными моделями) .

На вход 16 подается сигнал Пуск,

которьй производит установку в единичное состояние триггеров 4 и 5. Этот же сигнал устанавливает в нулевое состояние счетчик 15. Единичное состояние триггеров 4 обуславливает

возможность прохождения сигналов с выходов триггеров 3 на входы соот-. ветствующих элементов ШШ-НЕ 6. Единичное состояние триггеров 5 разрешает прохождение сигналов с выходов. элементов ШШ-НЕ 6 на соответствующие входы шифратора 8 при условии, что содержимое счетчика 15 равно номеру элемента ШШ-НЕ 6 (входа шиф- рДтора 8). После установки счетчика

15 в нулевое состо яние на его выходе отсутствует признак переполнения, поэтому через ключ 9 на суммирующий вход счетчика 15 по входу 19 устройства поступают импульсы. Каждый импульс увеличивает содержимое счетчика 15 на единицу. Двоичный код со3

держимого счетчика 15 преобразуется в дешифраторе 14 в сигнал на одном из его выходов. Аналогично серия из Р импульсов произведет последовательный опрос всех элементов ИШ-НЕ 6 с передачей присутствующих на их выходах единичных сигналов на соот- ветствуюшие входы шифратора 8. При появлении на выходе .какого-либо элемента И 7 единичного сигнала на выходе шифратора 8 формируется двоичный код номера элементарной модели. Этот код поступает на выход 21 устройства, который подключается ко всем элементарным моделям. При этом происходит .подготовка к включению соответствукнцей элементарной модели следовательно, по истечению одного цикла опроса будут подготовлены к включению все элементарные модели, запуск которых возможен исходя из топологии сети и текущего состояния предшествующих по связям элементарным моделям. Кроме того, единичные сигналы с выходов элементов И 7 приводят к установке в нулевое состояние соответствующих триггеров 5 исключая тем самым повторное включение допустимых элементарных моделей. При поступлении в счетчик 15 Р импульсов на его первом выходе появится, сигнал, который прекратит дальнейший опрос элементов ИЛИ-НЕ 6 Этот же сигнал через выход 20 устройства поступает на входа всех элементарных моделей и обеспечивает включение подготовленных уже моделей. При получении сигнала включения модели начинают выполнение заданных функций.

Определение номеров элементарных моделей, допустимых для включения в текущий момент времени по условию завершенности функционирования всех предшествующих по связям элементарных моделей, производится с помощью элементов ИЛИ-НЕ 6. В этом случае столбец матрицы 1, у которой все выходные сигналы элементов И 2 являются в текущий момент времени нулевыми, будет соответствовать допустимой для включения элементарной модели. Это утверждение основывается на таком построении устройства, при котором (к.м)-ая модель дуги, где , ... Р - номер строки (,...Р- номер столбца, характеризует связь .между к-й и м-й элементарными моделя778684

ми, причем к-я модель рассматривает- ся, как предшествующая. Случай отсутствия единичных сигналов на выхо- - дах всех моделей какого-либо столбца матрицы 1 соответствует случаю отсутствия предшественников у элементарной модели, соответствующей данному столбцу.

0 При завершении функционирования какой-либо элементарной модели на вхЬд 18 устройства с выхода данной модели поступает сигнал прерывания, а на вход 17 устройства выдается код

15 номера завершившейся элементарной .модели. Результатом преобразования поступившего кода в дешифраторе 13 является единичный сигнал на соответ- ствзпощем его выходе, который произ20 водит установку в нулевое состояние соответствующего триггера 4 и вычеркивание из топологии сети тех связей, в которых завершившаяся элементарная модель участвовала в роли

25 предшественника. Это осуществляется путем запрета прохождения на входы элементов ИЛИ-НЕ 6 сигналов с выходов триггеров 3 строки матрицы 1, совпадающей по номеру с завершившейся эле30 ментарной моделью. Поступивший по

входу 18 устройства сигнал устанавливает в нулевое состояние счетчик 15, в результате чего открывается ключ 9. С этого момента цикл работы устройства повторяется. При поступлении сигнала о завершении функционирования последней элементарной модели все триггеры 4 окажутся в нулевом состоянии и на выходе элемента НЕ 12 появится единичный сигнал.

35

40

Формула изобретения.

Устройство для моделирования топологии сети, содержащее два деши- дг фратора, два элемента ИЛИ и элемент НЕ, от. личающееся тем, что, с целью повышения быстродействия устройства за счет исключения времени считывания информации о топологии сети из памяти, в него введены две группы из Р триггеров, где Р-ко- личество вершин в моделируемой сети,. группа из Р элементов И, группа из Р элементов ИЛИ-НЕ, шифратор, ключ, счетчик и матрица из моделей дуг, каждая из которых содержит элемент И и триггер, выход которого подключен к первому входу элемента И той же модели дуги матрицы, вход

50

55

пуска устройства подключен к входам установки в 1 всех триггеров первой и второй групп триггеров и к первому входу первого элемента ИЛИ, вход задания номера завершенной модели устройства подключен к входу первого дешифратора, К-й выход которого (,...,) подключен к входу установки в О К-го триггера первой группы, выход которого подключен к вторым входам элементов И всех моделей дуг К-й строки матрицы и к К-му входу второго элемента ИЛИ, выход которого подключен к входу элемента НЕ, выход которого является выходом признака окончания работы устройства, выход элемента И М-й модели дуги К-й строки матрицы.подключен к К-му входу М-го элемента ИЛИ-НЕ группы, выход которого подключен к первому входу М-го элемента И группы, выход которого подключен к М-му входу шиф

Q 0

5

ратора и к входу установки в О М-го триггера второй группы, выход которого подключен к второму входу М-го элемента И группы, вход сигнала прерывания работы устройства подключен к второму входу первого элемента ИЛИ, выход которого подключен к входу установки в О счетчика, информационный выход которого подключен к информационному входу дешифратора, М-й выход которого подключен к второму входу М-го элемента И группы, тактовый вход устройства подключен к информационному входу ключа, выход которого подключен к суммирующему входу счетчика, выход признака переполнения которого является выходом признака разрешения пуска устройства и подключен к управляющему входу ключа, выход шифратора является информационным выходом устройства.

| Устройство для моделирования сетевого графика | 1977 |

|

SU686033A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования топологии сетей | 1982 |

|

SU1024930A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-28—Публикация

1986-04-07—Подача