со

00 ел

ISD

00

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении системы связи электронной вычислительной машины (ЭВМ) с удаленными источниками информации.

Целью изобретения является увеличение быстродействия устройства за счет досрочного окончания сеанса связи при передаче битовых последовательностей, заканчивающихся одинаковыми битами (цепочками «нулей или «единиц).

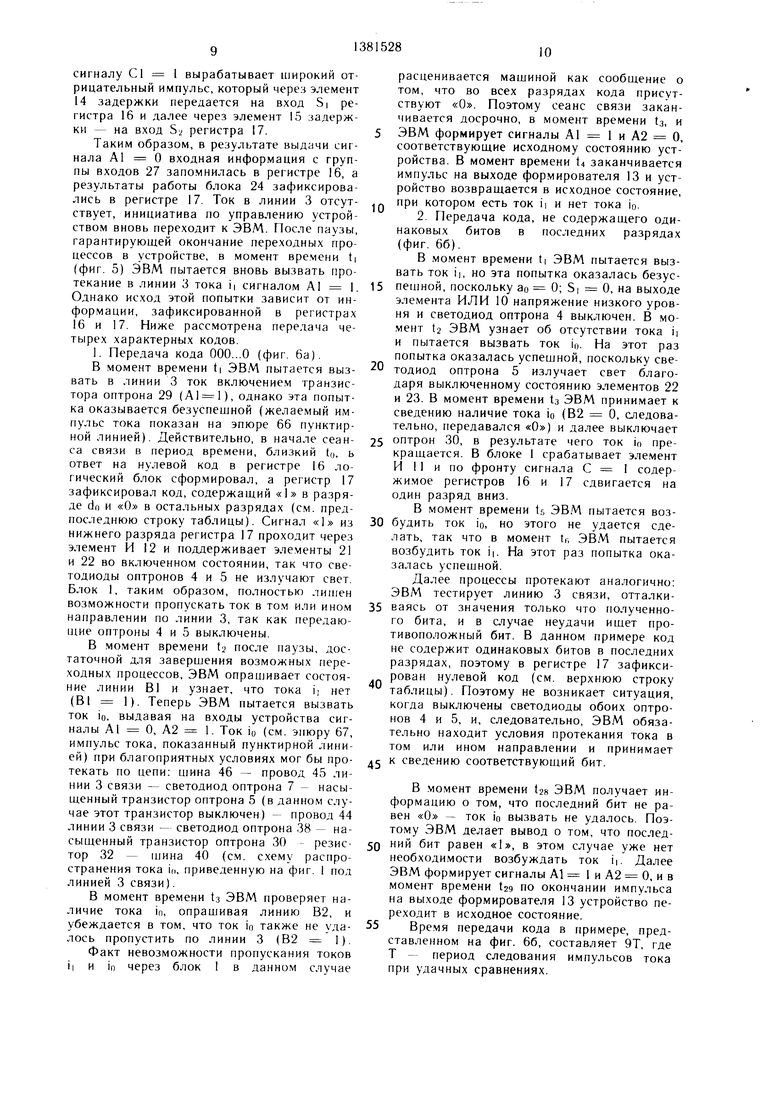

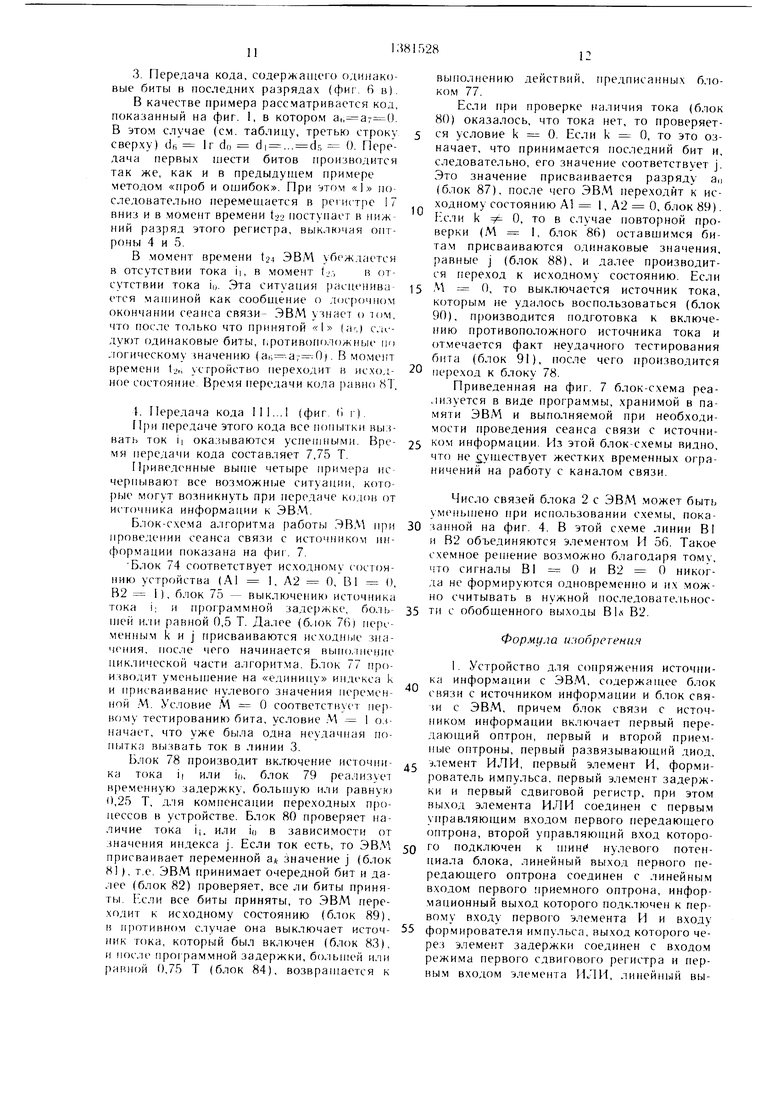

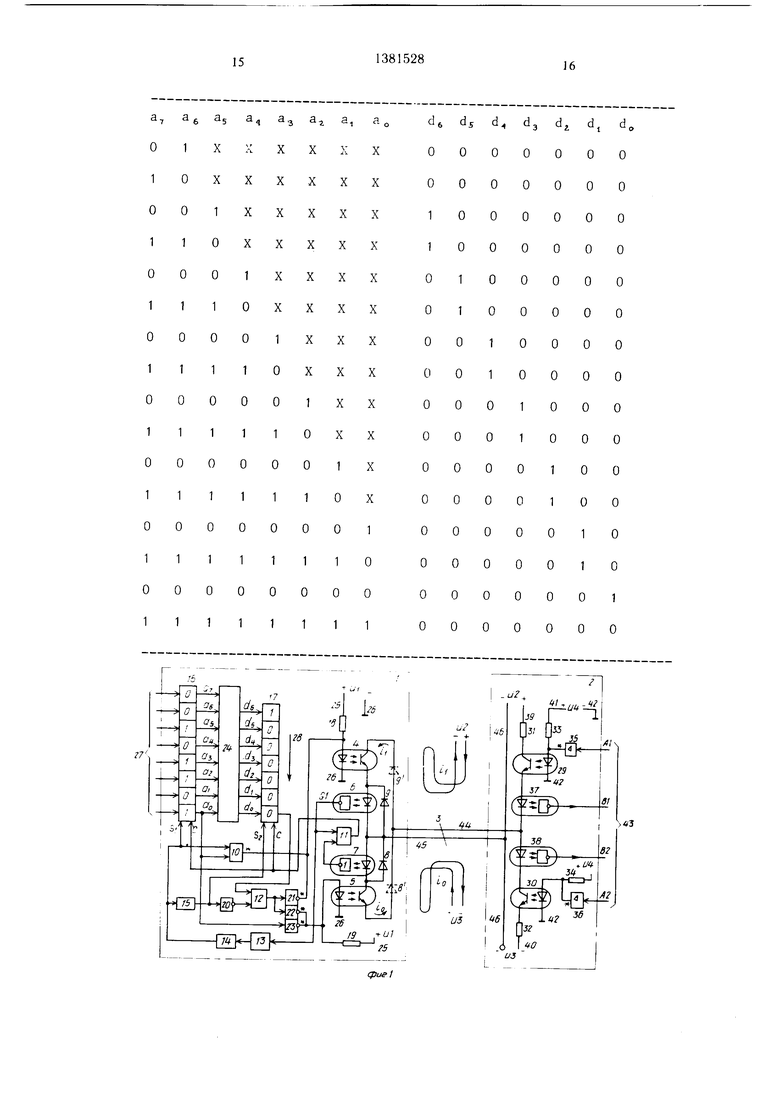

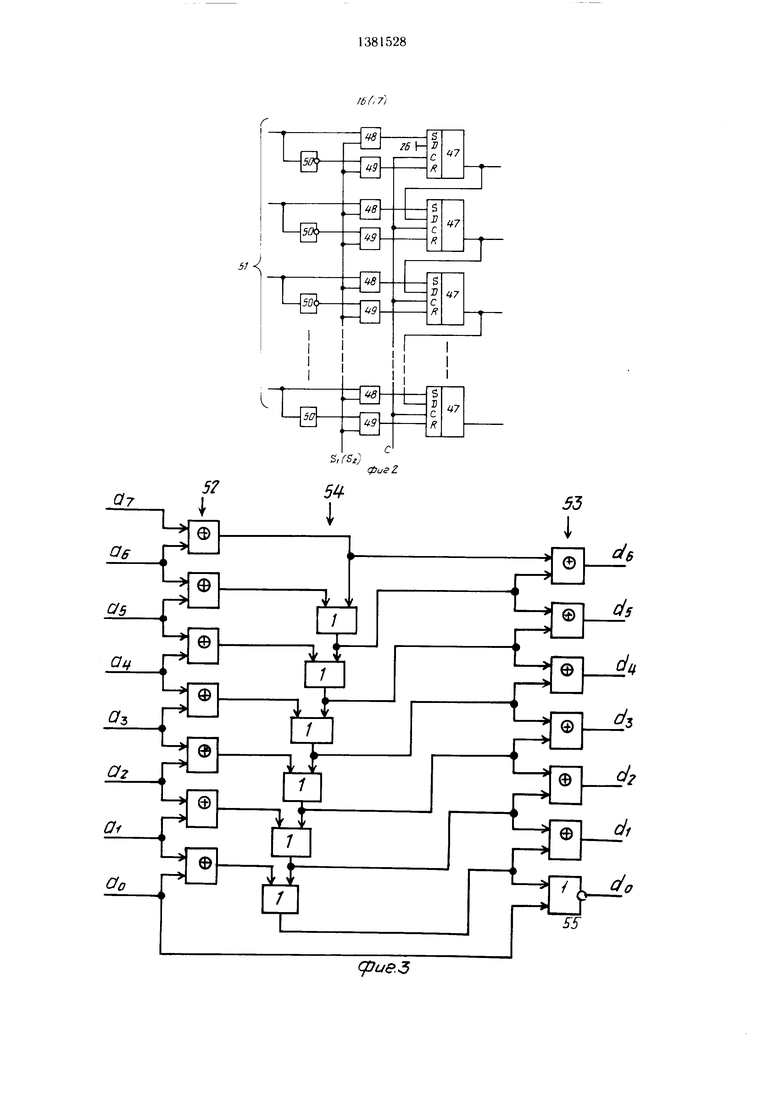

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - сдвиговой регистр; на фиг. 3 - блок деп ифрации кода; на фиг. 4 - блок связи с ЭВМ, в котором уменьшено число выходов; на фиг. 5 - временная диагра.мма начального периода сеанса связи ЭВМ с источником информации; на фиг. 6 - временные диаграммы работы устройства при передаче различных типов битовых последовательностей; на фиг. 7 - блок-схема алгоритма работы ЭВМ при проведении сеанса связи с источником информации; на фиг. 8 - временные характеристики известного и предлагаемого устройств.

Устройство для сопряжения источника информации с ЭВМ (фиг. 1) содержит блок 1 связи с источником инфор.мации и блок 2 связи с ЭВМ, соединенные двухпроводной линией 3 связи.

Блок 1 содержит первый и второй передающие оптроны 4 и 5, первый и второй приемные оптронь 6 и 7, первый и второй развязываюшие диоды 8 и 9, элемент ИЛИ К), первый и второй элементы И 11 и 12, формирователь 13 импульса, первый и второй элементы 14 и 15 задержки, первый и второй сдвиговые регистры 16 и 17, первый и второй токозадающие резисторы 18 и 19, первый- четвертый элементы НЕ 20-23, блок 24 де- П1ифрации кода.

Выход элемента ИЛИ 10 соединен с первым управляющим входом оптрона 4, соединенным через резистор 18 С шиной 25 питания. Второй управляющий вход оптрона 4 соединен с шиной 26 нулевого потенциала блока 1. Линейный выход оптрона 4 соединен с линейным входом оптрона 6. Информационный выход оптрона 6 соединен с первым входом элемента И 11 и входом формирователя 13, выход которого через элемент 14 соединен с входом режима регистра 16 и первым входом элемента ИЛИ 10. Линейный выход оптрона 6 соединен с линейным входом оптрона 7 и катодом диода 8, анод которого соединен с линейным выходом оптрона 7, информационный выход которого соединен с вторым входом элемента И 11, выход которого соедилен с входом синхронизации регистра 16. Выход младшего разряда регистра 16 соединен с вторым входом элемента ИЛИ 10. Группа 27 разрядных входов сдвигового регистра 16 является группой разрядных входов блока I устройства и соединена с группой выходов источника информации (на фиг. 1 источник информации не показан). Направление сдвига информации в регистрах 16 и 17 показано стрелкой 28.

Входы блока 24 соединены с одноименными выходами регистра 16, а его выходы - с одноименными разрядными входами регист ра 17, вход синхронизации которого соединен с выходом элемента И II, а вход режима - с выходом элемента 15 и входом элемента НЕ 20. Вход элемента 15 соединен с выходом элемента 14 задержки. Выход элемента НЕ 20 соединен с первым входом элемента И 12, второй вход которого соединен с выходом младшего разряда регистра 17. Выход элемента И 12 соединен с входами элементов 21 и 22. Выход элемента 21 соединен с выходом элемента ИЛИ 10, выход элемента 22 соединен с выходом эле0 мента 23, первым управляющим входом оптрона 5 и через резистор 19 - с шиной 25. Второй управляющий вход оптрона 5 соединен с щиной 26, вход элемента 23 соединен с вторым входом элемента ИЛИ 10. Катод

5 и анод диода 9 соединены соответственно с линейным входом и линейным выходом оптрона 6.

Блок 2 содержит первый и второй пере- даюпше оптроны 29 и 30, токозадаюшие резисторы 31-34, первый и второй усилите0 ли 35 и 36, а также первый и второй приемные оптроны 37 и 38. Линейный вход оптрона 29 через резистор 31 соединен с П1ИИОЙ 39 питания, линейный выход оптрона 29 соединен с линейным входом оптрона 37. Линейный выход оптрона 30 через ре5 зистор 32 соединен с шиной 40 питания. Выход усилителя 35 соединен с первым управляющим входом оптрона 29, соединенным через резистор 33 с шиной 41 питания. Второй управляющий вход оптрона 29 соединен с шиной 42 нулевого потенциала блока 2. Выход усилителя 36 соединен с первым управляющим входом оптрона 30, соединенным через резистор 34 с шиной 41 питания. Второй управляющий вход оптрона 30 соединен с щиной 42. Входы усили5 телей 35, 36 и информационные выходы оптронов 37 и 38 образуют группу связей 43 устройства с ЭВМ (ЭВМ на фиг. 1 не показана) и являются соответственно входами и выходами блока 2 (устройства).Линейные вход и выход оптрона 38 соединены соответ0 ственно с линейным выходом оптрона 37 и с линейным входом оптрона 30.

Первый и второй провода 44 и 45 двухпроводной линии 3 связи в блоке 1 соединены соответственно с линейным входом оптрона 4 и катодом диода 8, а в блоке 2 -

5 с линейны.м выходом оптрона 37 и щиной 46 нулевого потенциала линии.

С.двиговой регистр 16(17) (фиг. 2) содержит в каждом разряде триггер 47, элементы И 48, 49 и элемент НЕ 50. Точка объединения первых входов элементов И 48 и 49 является входом режима регистра, а точка объединения входов синхронизации триггеров 47 - входом синхронизации регистра. Триггеры 47 соединены между собой последовательно, причем D-вход триггера старшего разряда соединен с шиной 26 нулевого потенциала, что обеспечивает при сдвиге последовательное заполнение регистра нулями, начиная со старшего разряда. Входы 51 регистра в каждом разряде соединены с вторым входом злемерь та И 48 и через элемент 50 - с вторым входом элемента И 49. Выходы элементов И 48 и 49 соединены с входами установки в «1 и установки в «О соответствующих триггеров 47.

Блок 24 дешифрации кода (фиг. 3) содержит первую и вторую группы 52 и 53 сумматоров по модулю два (элементов ИСКЛЮЧАЮЩЕЕ ИЛИ), группу элементов ИЛИ 54 и элемент ИЛИ-НЕ 55. Входы элементов группы 52 являются входами блока, выходы этих элементов соединены с входами последовательно включенных элементов ИЛИ группы 54, выходы которых соединены с входами сумматоров группы 53 и первым входом элемента ИЛИ - НЕ 55. Выходы сумматоров группы 53 и выход элемента ИЛИ-НЕ 55 являются выходами блока, а второй вход элемента ИЛИ- НЕ 55 соединен с входом младшего разряда блока.

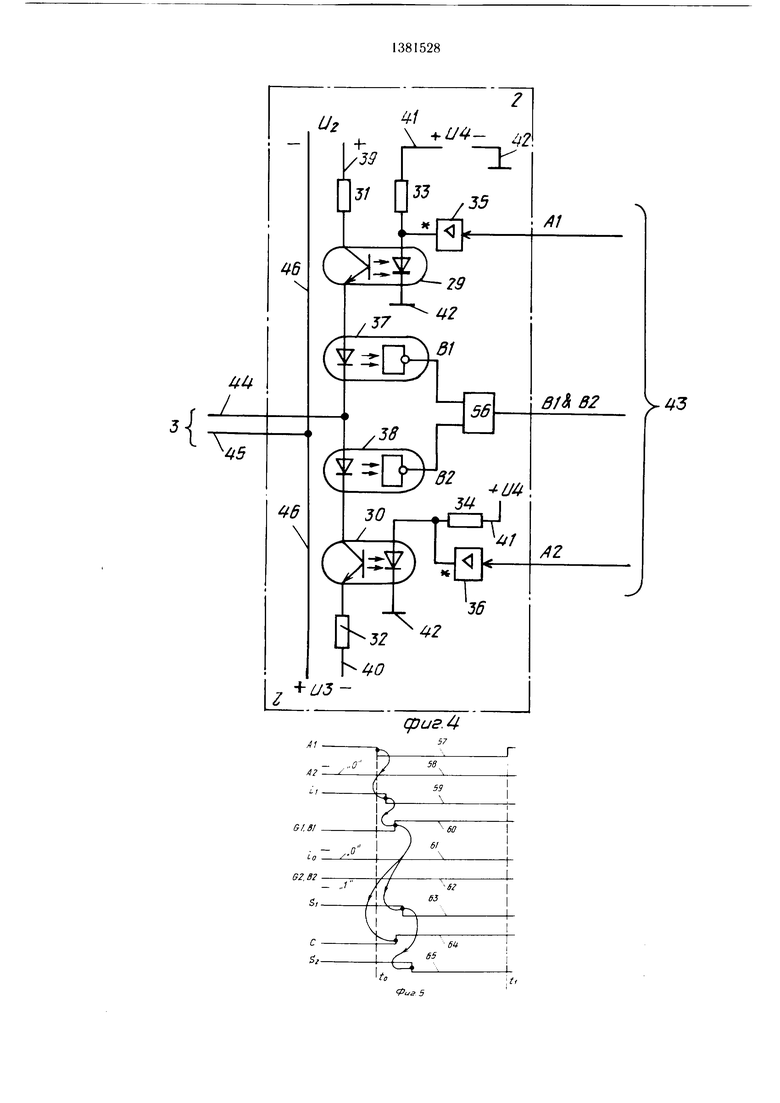

Блок 2 связи с ЭВМ (фиг. 4) дополнительно содержит эле.мент И 56, входы которого соединены с выходами оптронов 37 и 38, а выход этого элемента соединен с информационным входом ЭВМ, так что группа связей 43 блока 2 с ЭВМ содержит три (а не четыре, как на фиг. 1) линии. Остальные элементы и связи совпадают с приведенными на фиг. 1.

Эпюры 57-65 (фиг. 5) соответствуют сигналам в различных точках устройства на начальном этапе работы ЭВМ при обслуживании канала связи с источником информации. Эпюры 57 и 58 отображают сигналы А1 и А2, подаваемые со стороны ЭВМ на входы усилителей 35 и 36, эпюры 59 и 61 соответствуют токам i| и in, которые с разделением во времени протекают по линии 3 в противоположных направлениях, эпюра 60 соответствует сигналам G1 и В1 на выходах оптронов 6 и 37. Эпюра 62 соответствует сигналам G2 и В2 на выходах оптронов 7 и 38. Эпюры 63, 64 и 65 соответствуют сигналам на выходе элемента 14, выходе элемента И 11 и на выходе элемента 15.

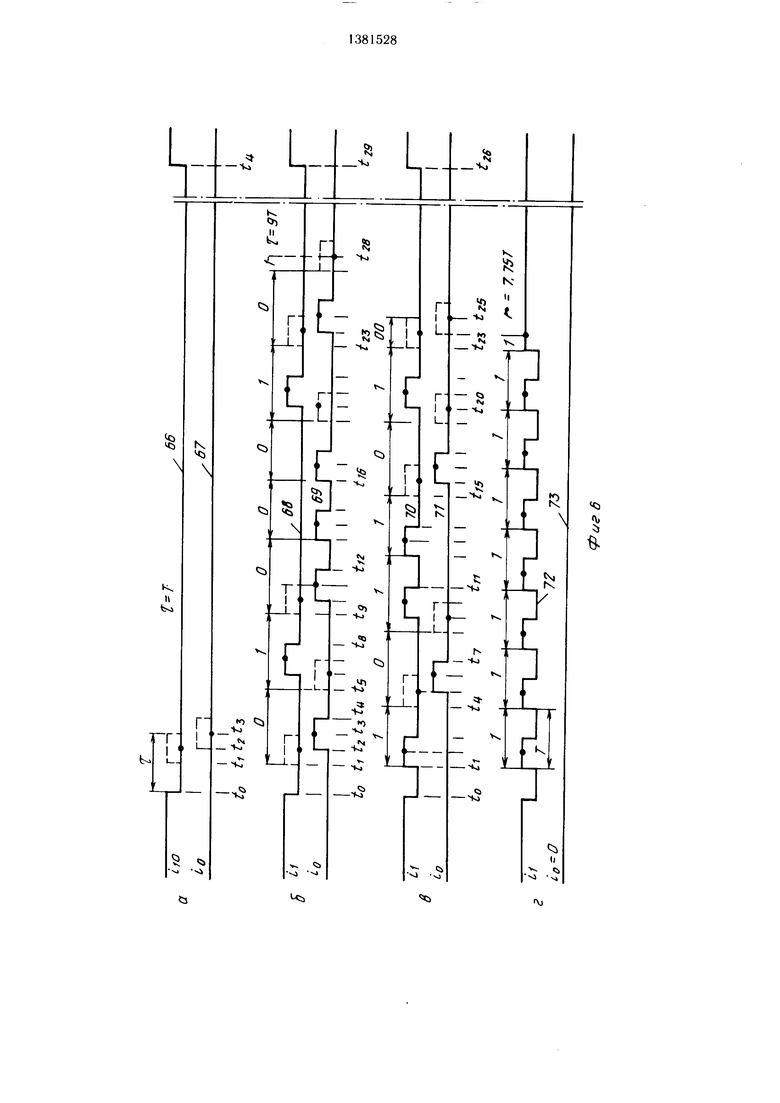

Эпюры 66 и 67, 68 и 69, 70 и 71, 72 и 73, приведенные на фиг. 6а-6г, соответствуют токам ii и if в линии 3 при передаче четырех характерных кодовых комбинаций.

Блок-схема алгоритма работы ЭВМ при проведении сеанса связи с источнико.м ин0

формации (фиг. 7) содержит блоки 74-91. Блок 74 соответствует исходному состоянию устройства, остальные блоки описывают последовательность действий, выполняемых

ЭВМ.

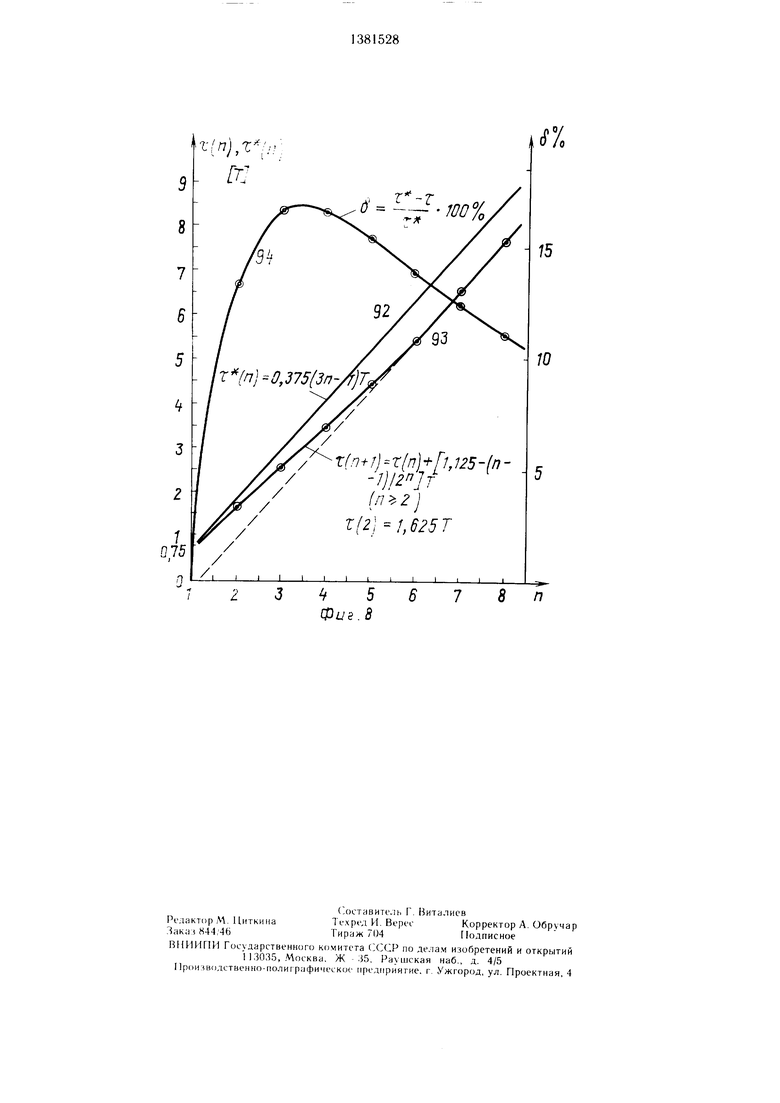

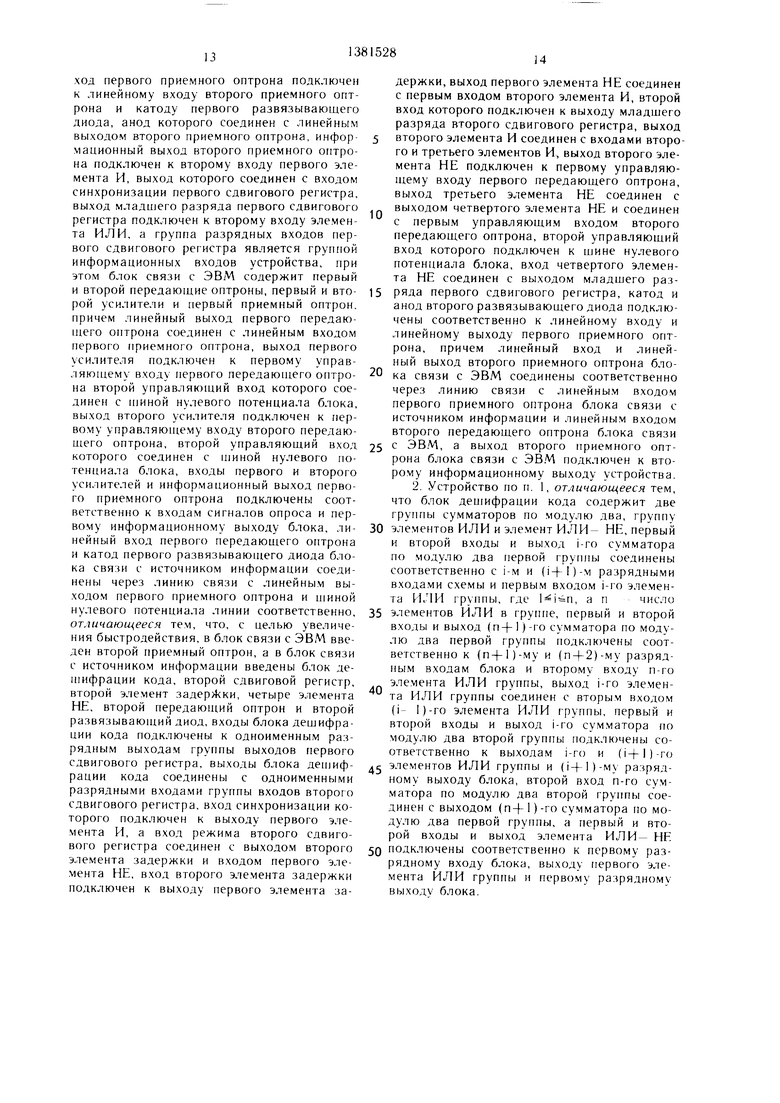

Эпюры 92 и 93 (фиг. 8) отображают зависимости среднего времени передачи кодового слова от его разрядности п. Эпюра 92 соответствует известному устройству, эпюра

Q 93 - предлагае.мому. Выигрыш во времени передачи кода (в процентах) характеризуется эпюрой 94.

Составные части устройства работают следуюшим образом.

Сдвиговой регистр 16(17) (см. фиг. 1, 2)

5 работает в двух режимах. При наличии сигнала «1 на режимном входе Si (82) регистр нечувствителен к сигналам на его входе синхронизации (С) и в его разрядах устанавливается код, поданный на его разрядные входы. В момент перехода сигнала Si(S2) из «1 в «О входной код фиксируется в регистре и в дальнейшем, при поступлении положительных перепадов напряжения по входу С, этот код последовательно сдвигается в регистре в направле5 НИИ, указанном стрелкой 28.

В примере выполнения регистра 16(17), приведенном на фиг. 2, указанные режимы реализуются элементами И 48 и 49. При Si(S2) О элементы И 48 и 49 закры0 ты и цепь последовательно включенных триггеров 47 производит сдвиг информации при каждом переходе сигнала С из «О в «I. Освободившиеся разряды заполняются «нулями. При Si (82) I элементы И 48 и 49 подготовлены к передаче входной информации

5 в триггеры 47, которые принудительно устанавливаются в нужные состояния при воздействии единичного сигнала на вход R или S. Входы R и S в стандартном D-триггере и.меют более высокий приоритет, чем вход С.

Q Поэтому при Si(S2) 1 реакция на сигнал по входу С отсутствует и регистр выполняет функции проводов, соединяющих его разрядные входы 51 с выходами.

Формирователь 13 вырабатывает на выходе отрицательный (по логическому значе5 нию) импульс при поступлении на его вход положительного фронта сигнала G1 с выхода оптрона 6. Длительность отрицательного импульса на выходе формирователя 13 выбирается большей, чем длительность одного сеанса связи с ЭВМ с источником инфор0 мации (в расчете на наихудший атучай). Эле.мент 14 задержки предотвращает возможные «гонки при совпадающих или близких по времени сигналах «защелкивания регистра 16 и управления и.м по входу С. Благодаря элементу 14 эти сигналы разне сены во времени, причем первый в сеансе связи положительный фронт сигнала синхронизации С воздействует на регистр 16 при Si l и, следовательно, теряется. Лишь пос

ле этого сигнал Si О поступает на регистр 16 с выхода элемента 14 задержки и регистр переходит в режим сдвига, ожидая следующего положительного фронта импульса С (предыдущий потерян). Элемент 14 задержки может быть выполнен, например, в виде четырех последовательно включенных элементов НЕ той же серии логических элементов, которая выбрана для реализации регистра 16.

Элемент 15 задержки компенсирует за- держку сигналов по цепи регистр 16 - блок 24 - регистр 17. В момент фор.ми- рования отрицательного фронта сигнала S| ) в регистре 16 запоминается код X, который обрабатывается блоком 24, как будет показано далее. Задержка элемента 15 такова, что сигнал Sa О поступает на регистр 17 заведомо позже, чем полезная информация из блока 24 - на его входы (с учетом необходимого запаса времени на предустановку). Регистр 17 запоминает ин- формацию со своих разрядных входов при переходе сигнала Si из «1 в «О и хранит, а затем сдвигает ее в направлении, указанном стрелкой 28.

Элемент ИЛИ 10, элементы НЕ 21-23 и усилители 35, 36 выполнены по схеме с открытым коллектором (см. обозначение «ж на фиг. 1) и предназначены для управления светодиодами передающих оптронов 4, 5, 29, 30. При подаче, например, сигнала «О на вход усилителя 35 выходной транзистор этого усилителя насыщается и щун- тирует светодиод оптрона 29, вызывая его включение и, следовательно, выключение выходного транзистора оптрона. При подаче на вход усилителя 35 сигнала «1 этот усилитель выключателя по выходу и ток через резистор 33 вызывает включение светодиода оптрона 29. Аналогично управляется свето- диод оптрона 30. Включение светодиода онт- рона 4 осуществляется при одновременном выключении элемента ИЛИ 10 (на его входах имеется по крайней мере одна ) и элемен- та 21 (на его входе «О). Аналогично включение светодиода оптрона 5 производится при одновременном выключений элементов 22 и 23.

Приемные оптроны 6, 7, 37, 38 выраба- тывают на своих выходах G1, G2, В1, В2 сигналы «О при излучении света светодиодами этих otiTpoHOB. Если светодиоды выключены, то на выходах оптронов 6, 7, 37, 38 вырабатываются сигналы «I. Диоды 8 и 9 предохраняют светодиоды оптронов 7 и 6 от воздействия напряжения обратной полярности. Эти диоды могут быть исключены из схемы, если светодиоды оптронов 6 и 7 допускают воздействие на них достаточно высокого обратного напряжения.

Транзисторы передающих оптронов 4, 5, 29, 30 находятся в режиме насыщения (с эквивалентным сопротивлением коллектор

5

0

0

5

0

5

0

эмиттер порядка 10 Ом) при одновременном выполнении двух усповий: соответствующий данному транзистору светодиод излучает свет; потенциал коллектора более положителен, чем потенциал эмиттера. Если выполнено второе ycjiOBHe (б), но не выполнено первое, то транзистор находится в высокоом- ном состоянии и его эквивалентное сопротивление равно нескольким десяткам или сотням килоом. Если не выполнено второе условие, то практически независимо от выполнения перво го условия транзистор находится в высо- коомном состоянии, хотя его эквивалентное обратное сопротивление не столь высоко, как при прямом включении, и не превышает 10 кОм (что вполне удовлетворительно). Однако при использовании передающих оптронов с пониженным обратным сопротивлением выходного транзистора следует ввести в схему развязывающие диоды 8 и 9, показанные на фиг. 1 пунктирными линиями. Эти диоды предотвращают протекание паразитного тока через транзисторы оптронов 4 и 5 при их обратном включении. Если диоды 8 и 9 исключены из схемы, то нет необходимости во введении диодов 8 и 9, поскольку функции развязывающих диодов в этом случае выполняются светодиодами оптронов 6 и 7.

Блок 24 (фиг. I, 3) анализирует код ао- а с целью выявления в нем цепочки одинаковых битов, расположенных в верхней (по схеме) части регистра 16. В примере, приведенном на фиг. 1, в верхних разрядах регистра 16 записаны два одинаковых бита: . Этот факт воспринимается блоком 24, и он фор.мирует на выходе de сигнал «1. В общем случае при Зп а„,... а разряд d, регистра 17 будет записана «1, а в остальные разряды - «О. Другими словами, в регистре 17 помечается начало «однородного конца кодового слова, записанного в регистр 16. Исключением является кодовая комбинация ... ао 1, в ответ на которую блок 24 формирует нулевой код dn-i dn-2 ... do 0.

Работа блока 24 представлена в таблице.

Знак «X в табл. 1 означает произвольное состояние («О или «1). Таким образом, в таблице перечислены все возможные кодовые комбинации в регистре 16. Например, комбинация 11000110 описывается четвертой строкой таблицы, комбинация 11101100 - щестой и т.д.

Группа 52 сумматоров (фиг. 3) выделяет во входном коде несовпадающие позиции. Группа элементов ИЛИ 54 размножает «верхнюю единицу с выходов сумматоров 52, а группа сумматоров 53 и элемент ИЛИ-НЕ 55 определяют границу между полученными группами «нулей и «единиц, т.е. производят окончательную обработку сигналов согласно таблице.

Блок 24 может быть выполнен в виде постоянного запоминающего устройства

(ПЗУ) емкостью 256 7-разрядных ячеек. Сигналы ао-а в этом случае поступают на адресные входы ПЗУ, а сигналы do-de формируются на его выходах данных. Возможно использование программируемой логической матрицы (ПЛМ) например, типа K556PTI, в качестве блока 24. При этом, как следует из таблицы, в матрице будет занято 13 (из 48) логических произведений, по числу «единиц в правой части табл. 1. Источник напряжения LI обеспечивает питание части схемы, непосредственно связанной с источником информации, в том числе питание выходных эле.ментов НЕ (инверторов) оптронов 6 и 7. Источники напряжения U2 и УЗ предназначены для задания «положительного или «отрицательного тока (i| или io) в линии связи 3 (токи i| и io никогда не текут одновременно). Эти источники, по существу, представляют собой один источник напряжения со средней точкой 46. Источник напряжения U 4 обеспечивает питание части схемы, связанной с ЭВМ, в том числе питание выходных элементов НЕ (инверторов) оптронов 37 и 38.

Использование оптронов обеспечивает гальваническую развязку линии 3 связи с источниками напряжения LI и LU и, следовательно, повьипенную помехозащищенность устройства. Линия 3 связи выполняется витой парой проводов; ее длина может достигать нескольких сотен метров.

Задача, рещаемая устройством, состоит в том, чтобы ЭВМ могла в произвольные моменты времени, по собственной инициативе, считывать инфор.мацию с входов 27, используя последовательный канал связи и асинхронный принцип обмена, без жесткой привязки к какой-либо синхронизирующей сетке. Процесс передачи кода может быть даже временно прерван в любой момент в связи с временным переходом ЭВМ к выполнению более приоритетного задания. Ограничение сверху на продолжительность сеанса связи определяется длительностью импульса на выходе формирователя 13.

Устройство работает следующим образом.

Блок 1 связи с источником информации производит последовательный сдвиг кодов, записанных в регистры 16 и 17. Если в нижнем разряде регистра 16 в некоторый момент времени присутствует «1, то блок I разрещает прохождение через него тока i. В пративном случае блок подготовлен к прохождению через него тока in, а для тока ii цепь разомкнута. ЭВМ при передаче каждого бита тестирует линию 3 связи, пытаясь возбудить ток и или in. Если удалось вызвать ток ii (io), то это означает, что передается «1 («О). Если не удалось вызвать ток i|(io), то ЭВМ пытается вызвать ток io(ii). Эта повторная попытка может оказаться успешной и ЭВМ регистрирует соответствуюп1ий бит, а информация в регистрах 16 и 17 по окончании импульса тока сдвигается на один разряд вниз. Если повторная попытка оказалась безуспешной, то ЭВМ узнает, что блок 1 неспособен транслировать через себя ток ни в том, ни в другом направлении из-за того, что в нижнем разряде регистра 17 присутствует «1. Это, в свою очередь, означает, что оставшиеся биты передаваемого кода

Q имеют одинаковые значения (противоположные только что принятому биту). Поэтому нет смысла тратить время на передачу этих одинаковых битов и сеанс связи досрочно заканчивается, а ЭВМ доопределяет недостающие биты в принятом коде нулями

5 или единицами, в зависимости от предыстории. Таким образом, среднее время передачи кода от источника информации к ЭВМ сокращается.

В исходном состоянии (с.м. фиг. 5, период времени до момента to) из выходного порта

ЭВМ на входы блока 2 поданы сигналы А и , поэтому светодиод оптро- на 29 включен, а светодиод оптрона 30 выключен, так что потенциал провода 44 более положителен, чем потенциал провода 45.

5 В блоке 1 в исходном состоянии Si Sj 1 (предыдущий сеанс связи, если он был завер- пен, отрицательный импульс на выходе формирователя 13 закончился), регистр 16 транслирует сигналы с входов 27 на свои выходы, на выходе элемента 20 поддерживается сиг0 нал «О, который запирает элемент И 12 и выключает элементы 21 и 22. Сигнал S| 1 воздействует на элемент ИЛИ 10 с открытым коллекторо.м, так что выходной транзистор этого элемента выключен. Поэтому светодиод оптрона 4 включен, транзистор этого

5 оптрона насыщен и созданы благоприятные условия для протекания тока по цепи источника напряжения U 2: тина 39 - резистор 31 - насыщенный транзистор оптрона 29 - светодиод оптрона 37 - про вод 44 линии связи 3 - насыщенный транзистор оптрона 4 - светодиод оптрона 6 - провод 45 линии связи 3 - тина 46. Этот путь условно показан на фиг. 1 над линией 3 связи. Ток через транзистор оптрона 5 близок нулю, поскольку к нему при5 ложено обратное напряжение.

Сеанс связи начинается в момент времени to (фиг. 5) по инициативе ЭВМ, которая выдает сигнал А1 О на вход усилителя 35 блока 2, что вызывает прекра0 щение тока ii в линии 3 связи из-за выключения транзистора оптрона 29. На выходах оптронов 6 и 37 формируются единичные сигналы G1 1 и 81 1 (эпюра 60). При этом срабатывает элемент И 11 и формируется положительный фронт сигнала С,

который, однако, не воздействует на состояние регистров 16 и 17, поскольку на их входах Si и S2 все еще присутствуют сигналы «1. Формирователь 13 импульса по

сигналу Cl 1 вырабатывает 1иирокий отрицательный импульс, который через элемент 14 задержки передается на вход S| регистра 16 и далее через элемент 15 задержки - на вход S-2 регистра 17.

Таким образом, в результате выдачи сигнала А1 О входная информация с группы входов 27 запомнилась в регистре 16, а результаты работы блока 24 зафиксировались в регистре 17. Ток в линии 3 отсутствует, инициатива по управлению устройством вновь переходит к ЭВМ. После паузы, гарантирующей окончание переходных процессов в устройстве, в момент времени t| (фиг. 5) ЭВМ пытается вновь вызвать протекание в линии 3 тока ii сигналом AI 1. Однако исход этой попытки зависит от информации, зафиксированной в регистрах 16 и 17. Ниже рассмотрена передача четырех характерных кодов.

1. Передача кода 000...О (фиг. 6а).

В момент времени ti ЭВМ пытается вызвать в линии 3 ток включение.м транзистора оптрона 29 (), однако эта попытка оказывается безуспешной (желаемый импульс тока показан на эпюре 66 пунктирной линией). Действительно, в начале сеанса связи в период времени, близкий to, ь ответ на нулевой код в регистре 16 логический блок сфор.мировал, а регистр 17 зафиксировал код, содержащий «1 в разряде do и «О в остальных разрядах (см. предпоследнюю строку таблицы). Сигнал «1 из нижнего разряда регистра 17 проходит через элемент И 12 и поддерживает элементы 21 и 22 во включенном состоянии, так что све- тодиоды оптронов 4 и 5 не излучают свет. Блок 1, таким образом, полностью лишен возможности пропускать ток в то.м или ином направлении по линии 3, так как передающие оптроны 4 и 5 выключены.

В момент времени 2 после паузы, достаточной для завершения возможных переходных процессов, ЭВМ опрашивает состояние линии В1 и узнает, что тока ij нет (В1 1). Теперь ЭВМ пытается вызвать ток io, выдавая на входы устройства сигналы А1 О, А2 1. Ток io (см. эпюру 67, импульс тока, показанный пунктирной линией) при благоприятных условиях мог бы протекать по цепи: шина 46 - провод 45 линии 3 связи - светодиод оптрона 7 - насыщенный транзистор оптрона 5 (в данном случае этот транзистор выключен) - провод 44 линии 3 связи - светодиод оптрона 38 - насыщенный транзистор оптрона 30 - резистор 32 - шина 40 (см. схему распространения тока id, приведенную на фиг. 1 под линией 3 связи).

В момент времени 1з ЭВМ проверяет наличие тока in, опрашивая линию В2, и убеждается в том, что ток io также не удалось пропустить по линии 3 (В2 I).

Факт невозможности пропускания токов ii и io через блок 1 в данном случае

расценивается машиной как сообшение о том, что во всех разрядах кода присутствуют «О. Поэтому сеанс связи заканчивается досрочно, в момент времени 1з, и

ЭВМ формирует сигналы А1 1 и А2 О, соответствующие исходному состоянию устройства. В момент времени t4 заканчивается импульс на выходе формирователя 13 и устройство возвращается в исходное состояние,

при котором есть ток ii и нет тока io.

2. Передача кода, не содержащего одинаковых битов в последних разрядах (фиг. 66).

В момент времени t| ЭВМ пытается вызвать ток ii, но эта попытка оказалась безус5 пешной, поскольку ао 0; S| О, на выходе элемента ИЛИ 10 напряжение низкого уровня и светодиод оптрона 4 выключен. В мо- .мент 12 ЭВМ узнает об отсутствии тока ii и пытается вызвать ток io. На этот раз попытка оказалась успешной, поскольку све0 тодиод оптрона 5 излучает свет благодаря выключенному состоянию элементов 22 и 23. В момент времени 1з ЭВМ принимает к сведению наличие тока io (В2 О, следовательно, передавался «О) и далее выключает

5 оптрон 30, в результате чего ток io прекращается. В блоке 1 срабатывает элемент И 11 и по фронту сигнала С 1 содержимое регистров 16 и 17 сдвигается на один разряд вниз.

В момент времени ts ЭВМ пытается воз0 будить ток io, но этого не удается сделать, так что в момент tr, ЭВМ пытается возбудить ток i|. На этот раз попытка оказалась успещной.

Далее процессы протекают аналогично: ЭВМ тестирует линию 3 связи, отталки5 ваясь от значения только что полученного бита, и в случае неудачи ищет противоположный бит. В данном примере код не содержит одинаковых битов в последних разрядах, поэтому в регистре 17 зафиксирован нулевой код (см. верхнюю строку таблицы). Поэтому не возникает ситуация, когда выключены светодиоды обоих оптронов 4 и 5, и, следовательно, ЭВМ обязательно находит условия протекания тока в том или ином направлении и принимает

5 к сведению соответствующий бит.

В момент времени 128 ЭВМ получает информацию о том, что последний бит не равен «О - ток io вызвать не удалось. Поэтому ЭВМ делает вывод о том, что послед0 НИИ бит равен «1, в этом случае уже нет необходимости возбуждать ток i|. Далее ЭВМ формирует сигналы А1 1 и А2 О, и в момент времени 129 по окончании импульса на выходе формирователя 13 устройство переходит в исходное состояние.

5 Время передачи кода в примере, представленном на фиг. 66, составляет 9Т, где Т - период следования импульсов тока при удачных сравнениях.

0

3. Передача кода, содержащего одинаковые биты в последних разрядах (фиг. 6 в).

В качестве примера рассматривается код, показанный на фиг. 1, в котором а,,. В этом случае (см. таблицу, третью строку сверху) dfi 1г do di... d5 0. Передача первых luecTH битов производится так же, как и в предыдущем примере методом «проб и ошибок. При «1 последовательно перемещается в регистре 17 вниз и в момент времени t92 поступает в ({иж- пий разряд этого регистра, выключая опт- рои ы 4 и 5.

В момент времени (94 ЭВМ убеждается в отсутствии тока ii, в MOMetiT (.т, к отсутствии тока ii). Эта ситуации расценивается машиной как сообщение о д()С()очном окончании сеанса связи- ЭВМ узнает о том, что после только что принятой «I (аг) с,к - дуют одинаковые биты, гфотивоположные по логическому значению (а(). В момеш времени t,, устройство переходит в исходное состояние- Время передачи кода равно 8Т.

}. Передача кода 111.,. (фиг. (i г).

П|П1 передаче этого кода все поиьггки вызвать ток ii оказываются успешными. Время передачи кода составляет 7,75 Т.

П)инеденные вьнпе четыре примера ис- черпываю все воз.можные ситуации, которые могут возникнуть при передаче кодов от HCTO4ifHKa информации к ЭВМ.

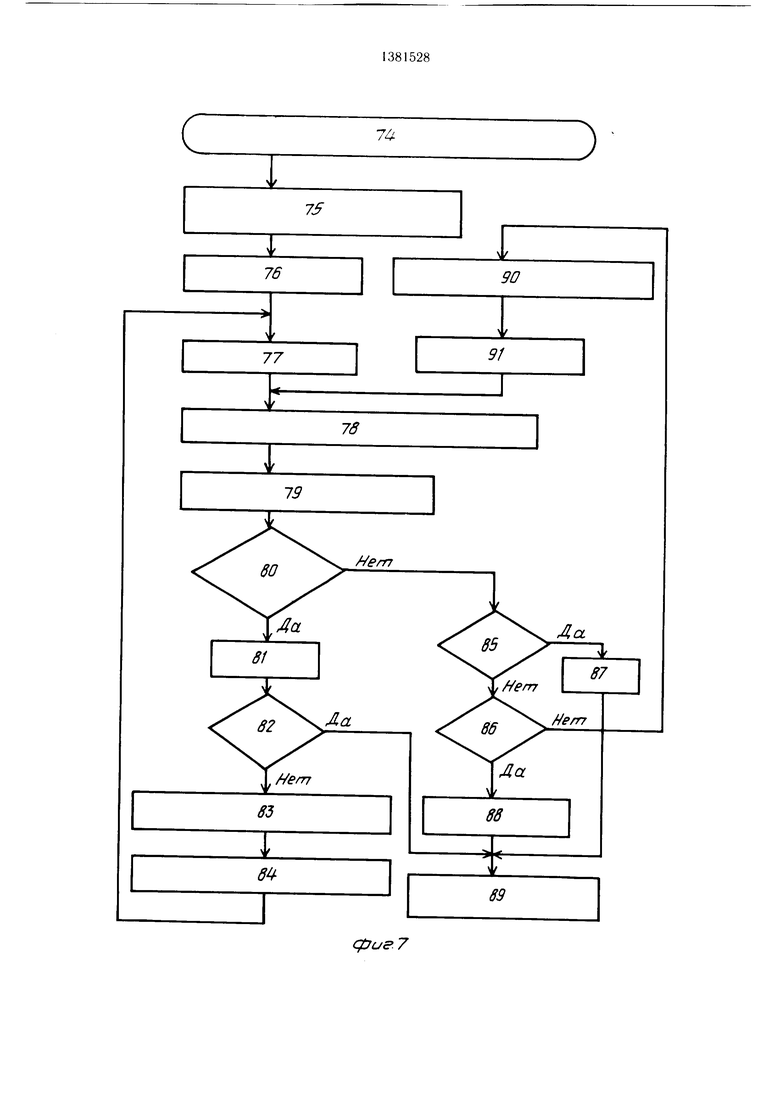

Блок-схема алгоритма работы ЭВМ при проведении сеанса связи с источником информации показана на фиг. 7.

Блок 74 соответствует исходному состоянию устройства (А1 1, Л2 О, В1 О, В2 1), блок 75 - выключению источника тока i; и програ.ммной задержке, боль- Н1ей или равной 0,5 Т. Далее (блок 76) переменным k и j присваиваются исходные значения, после чего начинается вьиюлнение циклической части алгоритма. Блок 77 производит уменьц ение на «единицу индекса k и присваивание нулевого значения переменной .М. Условие ДА О соответствует пер- Bf)My тестированию бита, условие Л 1 означает, что уже была одна неудачная по- гц.1тка вызвать ток в линии 3.

Блок 78 производит включение источника тока ii или io, блок 79 реализует в()еменную задержку, бoльцJyю или равную 0,25 Т, для компенсации переходных п)о- цессов в устройстве. Блок 80 проверяет наличие тока ii. или i() в зависимости от значения индекса J. Если ток есть, то ЭВМ присваивает переменной а значение j (блок 81), т.е. ЭВМ принимает очередной бит и далее (блок 82) проверяет, все ли биты приняты. Если все биты приняты, то ЭВМ переходит к исходному состоянию (блок 89), и противном случае она выключает источник тока, который был включен (блок 83), и после прог рам.мной задержки, большей или Равной 0,75 Т (блок 84), возвращается к

0

выполнению действий, предписанных блоком 77.

Если при проверке наличия тока (блок 80) оказалось, что тока нет, то проверяет- ся условие k 0. Если k О, то это означает, что принимается последний бит и, следовательно, его значение соответствует j. Это значение присваивается разряду аи (блок 87), после чего ЭВМ переходит к исходному состоянию А1 I, А2 О, блок 89). Если k О, то в случае повторной проверки (М 1, блок 86) оставшимся битам присваиваются одинаковые значения, равные j (блок 88), и далее производится переход к исходному состоянию. Если

5 М О, то выключается источник тока, которым не удалось воспользоваться (блок 90), п)оизводится подготовка к включению противоположного источника тока и отмечается факт неудачного тестирования бита (блок 91), после чего производится

0 переход к блоку 78.

Приведенная на фиг. 7 блок-схема реализуется в виде программы, хранимой в памяти ЭВМ и выполняемой при необходимости проведения сеанса связи с источни5 ком информации. Из этой блок-схемы видно, что не существует жестких временных ограничений на работу с кана,1ом связи.

Число связей блока 2 с ЭВМ может быть уменьшено при использовании схемы, пока0 занной на фиг. 4. В этой схеме линии В1 и В2 объединяются эле.менто.м И 56. Такое схемное решение возможно благодаря тому, что сигналы В1 О и В2 О никогда не формируются одновременно и и.х можно считывать в нужной последовате.тьнос5 ти с обобщенного выходы В 1л В2.

Формула изобретения

1. Устройство для сопряжения источника информации с ЭВМ, содержащее блок связи с источником информации и б,1ок связи с ЭВМ, причем блок связи с источником информации включает первый передающий оптрон, первый и второй приемные онтроны, первый развязывающий диод,

элемент ИЛИ, первый элемент И, формирователь импульса, первый элемент задержки и первый сдвиговой регистр, при этом выход элемента ИЛИ соединен с первы.м управляющим входом первого передаю|дего оптрона, второй управляющий вход которого подключен к шин нулевого потенциала блока, линейный выход первого передающего оптрона соединен с линейным входом первого приемного оптрона, информационный выход которого подключен к первому входу первого элемента И и входу

фор.мирователя импульса, выход которого через элемент задержки соединен с входом режима первого сдвигового регистра и первы.м входом элемента ИЛИ, линейный выход первого приемного оптрона подключен к линейному входу второго приемного оптрона и катоду первого развязывающего диода, анод которого соединен с линейным выходом второго приемного оптрона, информационный выход второго приемного оптрона подключен к второму входу первого элемента И, выход которого соединен с входом синхронизации первого сдвигового регистра, выход младшего разряда первого сдвигового регистра подключен к второму входу элемента ИЛИ, а группа разрядных входов первого сдвигового регистра является группой информационных входов устройства, при этом блок связи с ЭВМ содержит первый и второй передающие оптроны, первый и второй усилители и первый приемный оптрон, причем линейный выход первого передаю- niero онтрона соединен с линейным входом первого приемного оптрона, выход первого усилителя подключен к первому управляющему входу первого передаюп1его оптрона второй управляющий вход которого соединен с нулевого потенциала блока, выход второго усилителя подключен к первому управляю1цему входу второго передающего оптрона, второй управляющий вход которого соединен с тиной нулевого потенциала блока, входы первого и второго усилителей и информационный выход первого приемного оптрона подключены соответственно к входам сигналов опроса и первому информационному выходу блока, линейный вход первого передающего оптрона и катод первого развязывающего диода блока связи с источником информации соединены через линию связи с линейным выходом первого приемного онтрона и тиной нулевого потенциала линии соответственно, отличающееся тем, что, с целью увеличения быстродействия, в блок связи с ЭВМ введен второй приемный оптрон, а в блок связи с источником информации введены блок дешифрации кода, второй сдвиговой регистр, второй элемент зaдep kки, четыре элемента НЕ, второй передающий онтрон и второй развязывающий диод, входы блока дешифрации кода подключены к одноименным разрядным выходам группы выходов первого сдвигового регистра, выходы блока дешифрации кода соединены с одноименными разрядными входами группы входов второго сдвигового регистра, вход синхронизации которого подключен к выходу первого элемента И, а вход режима второго сдвигового регистра соединен с выходом второго элемента задержки и входом первого элемента НЕ, вход второго элемента задержки подключен к выходу первого элемента задержки, выход первого элемента НЕ соединен с первым входом второго элемента И, второй вход которого подключен к выходу младшего разряда второго сдвигового регистра, выход

второго элемента И соединен с входами второго и третьего элементов И, выход второго элемента НЕ подключен к первому управляющему входу первого передающего оптрона, выход третьего элемента НЕ соединен с выходом четвертого элемента НЕ и соединен с первым управляющим входом второго передающего оптрона, второй управляющий вход которого подключен к тине нулевого потенциала блока, вход четвертого элемента НЕ соединен с выходом младшего разряда первого сдвигового регистра, катод и анод второго развязывающего диода подключены соответственно к линейному входу и линейному выходу первого приемного оптрона, причем линейный вход и линейный выход второго приемного оптрона бло0 ка связи с ЭВМ соединены соответственно через линию связи с линейным входом первого приемного оптрона блока связи с источником информации и линейным входом второго передающего оптрона блока связи

5 с ЭВМ, а выход второго приемного оптрона блока связи с ЭВМ подключен к второму информационному выходу устройства. 2. Устройство но п. 1, отличающееся тем, что блок дешифрации кода содержит две группы сумматоров по модулю два, группу

0 элементов ИЛИ и элемент ИЛИ- НЕ, первый и второй входы и выход i-ro сумматора по модулю два первой группы соединены соответственно с i-м и (1-(-1)-м разрядными входами схемы и нервым входом i-ro элемента ИЛИ группы, где , а п число

5 элементов ИЛИ в группе, первый и второй входы и выход (п+1)-го сумматора по модулю два первой группы подключены соответственно к (п+1)-му и (п-|-2)-му разрядным входам блока и второму входу п-го элемента ИЛИ группы, выход i-ro элемен0

та ИЛИ группы соединен с вторым входом

(i- 1)-го элемента ИЛИ группы, первый и второй входы и выход i-ro сумматора по модулю два второй группы подключены соответственно к выходам i-ro и (i-|-l)-ro

элементов ИЛИ группы и (i-)-l)-My разрядному выходу блока, второй вход п-го сумматора по модулю два второй группы соединен с выходом (п+ 1) -го сумматора по модулю два первой группы, а первый и второй входы и выход элемента ИЛИ- НЕ

0 нодключены соответственно к первому разрядному входу блока, выходу первого элемента ИЛИ группы и первому разрядному выходу блока.

О 1

X X

1 О X X

XXX

о о 1 X X

X X

1

1 о X X X X

de 5 d dj d dj d,

0000000

0000000

1000000

1000000

Изобретение относится к вычислительной технике и .может быть использовано при построении системы связи ЭВМ с удаленными источниками информации. Целью изобретения является увеличение быстродействия устройства за счет «досрочного окончания сеанса связи при передаче последовательностей, заканчивающихся одинаковыми битами. С этой целью в устройстве, содержащем блок связи с источником информации, включающий первый передающий опт- рон, два приемных оптрона, первый диод, элемент ИЛИ, первый элемент И, формирователь импульса, первый элемент задержки и первый сдвиговый регистр, и блок связи с ЭВМ, включающий два передающих оптрона, первый приемный оптрон и два усилителя, в блок связи с ЭВМ введен второй прие.мный оптрон, а в блок связи с источником информации введены блок дещиф- рации кода, второй сдвиговый регистр, второй элемент задержки, четыре элемента НЕ, второй передающий оптрон и второй диод. 1 з.п. ф-лы. 8 ил. 1 табл.

1

00000

1

X X X X

001

1 1 оXXXX

о о о1XXX 1

о о оо1XX

1 1 11оXX

X

1 о X X X

1111

1

1 о X

00000001 11111110 00000000

11111111

7

0

10000 100000 010000 010000 001000 001000 000100 000100 000010 000010 000001 000000

(JJue.5

У

фиг.7

75

О

/

/

/

/

-Г(,(П

1л.2 г 12 1,625 Т

23 567

Фиг.8

8

15

10

8

п

| Устройство для сопряжения источника информации с эвм | 1984 |

|

SU1229768A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Шевкопляс Б | |||

| В | |||

| Микропроцессорные структуры: инженерные решения | |||

| М.: Радио и связь, 1986, с | |||

| , рис | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-03-15—Публикация

1986-11-17—Подача