iO Р-кан п-кан

/У

-01

/

/

(Л

гУГ

Ci

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматической регулировки усиления | 1988 |

|

SU1732428A1 |

| ИНДУКТИВНЫЙ ДАТЧИК | 2008 |

|

RU2367968C1 |

| Среднеквадратичный детектор | 1990 |

|

SU1781640A1 |

| ИЗМЕРИТЕЛЬ ВИБРАЦИИ | 2020 |

|

RU2754243C1 |

| Многоканальный регистратор среднеквадратических значений биопотенциалов | 2016 |

|

RU2623644C1 |

| Преобразователь напряжения в длительность импульсов | 1990 |

|

SU1785071A1 |

| ИЗМЕРИТЕЛЬ ВИБРАЦИИ | 2021 |

|

RU2783752C1 |

| СИСТЕМА УПРАВЛЕНИЯ ДВИГАТЕЛЕМ С ЭЛЕКТРОННОЙ КОММУТАЦИЕЙ | 1994 |

|

RU2096906C1 |

| Устройство для стабилизации переменного тока | 1990 |

|

SU1767652A1 |

| Способ фиксации базового уровня импульсного сигнала и устройство для его осуществления | 1985 |

|

SU1364014A1 |

И: обретение относится к радиотехнике. Цель изобретения - увеличение точности детектирования. Детектор содержит интегрирующий блок 1, блоки выборки-.хранения 5 и 6, вычитатель 7 и блок управления 8. Цель достигается путем обеспечения независимости коэф. передачи синхронного амплитудного детектора от величины несушей частоты и величины сдвига фаз между несуа1ей и опорной частотами. 2 ил.

фиг.

Изобретение относится к радиотехнике и предназначено для использования в радиоприемных и радиоизмерительных устройствах.

Цель изобретения - увеличение точности детектирования путем обеспечения независимости коэффициента передачи синхронного амплитудного детектора от величины несущей частоты и величины сдвига фаз между несущей и опорной частотами.

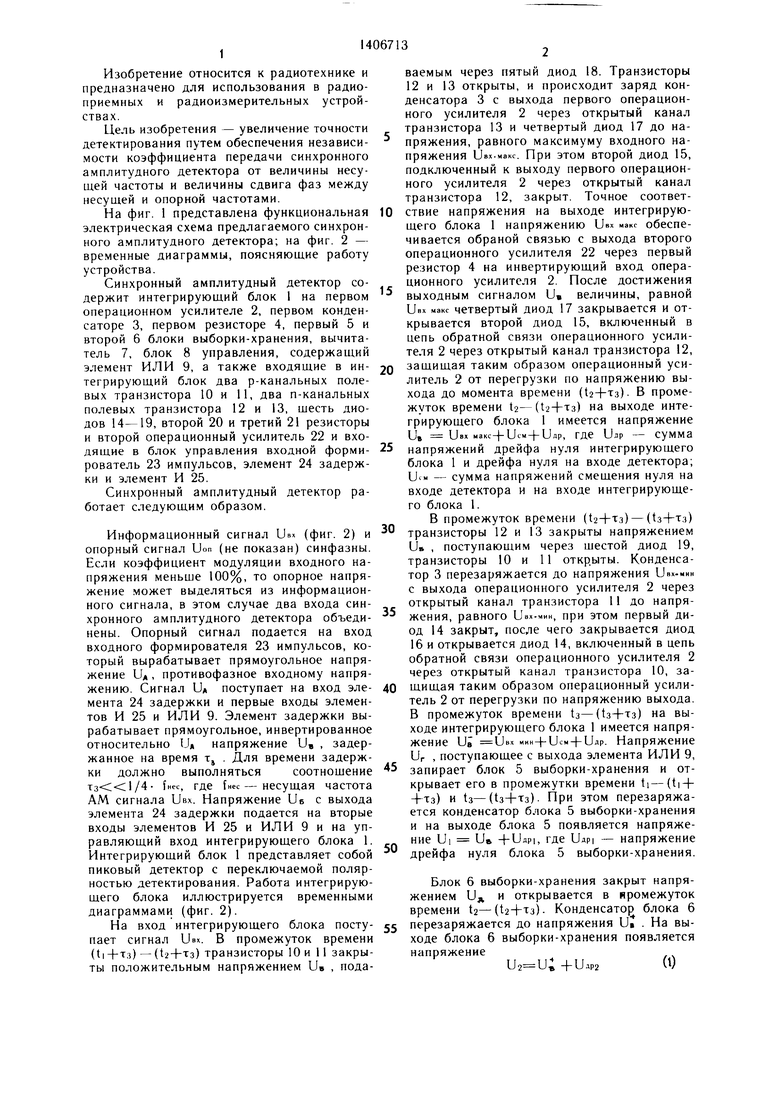

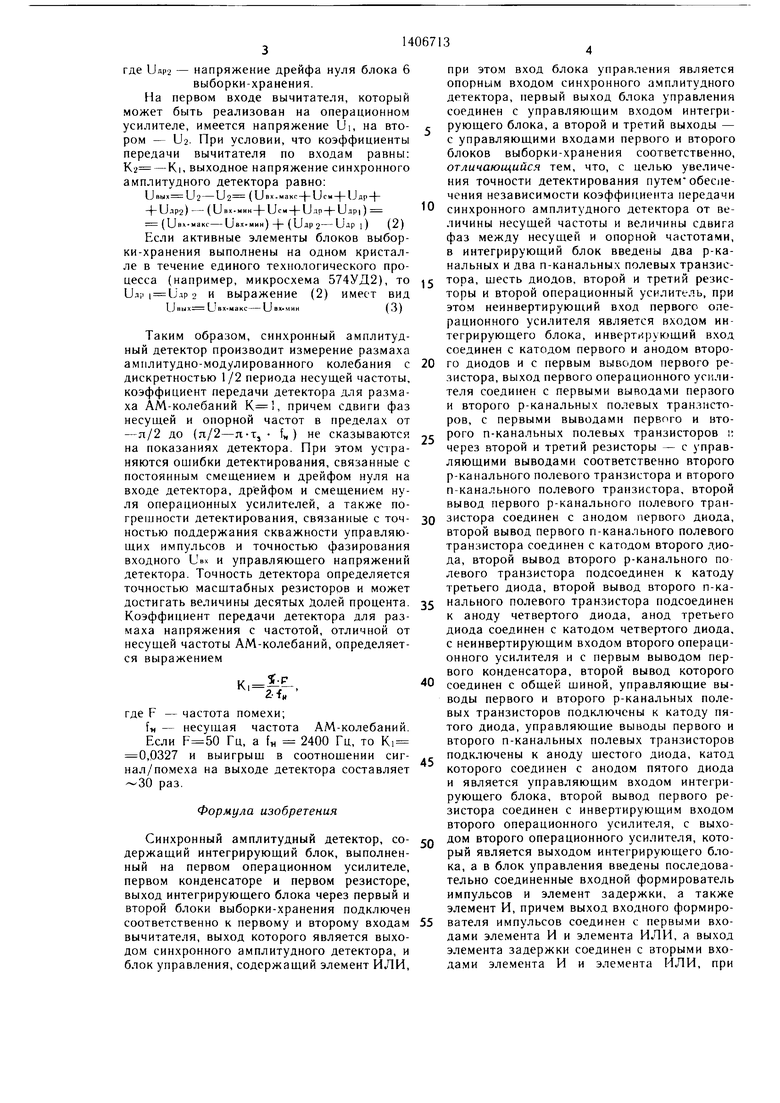

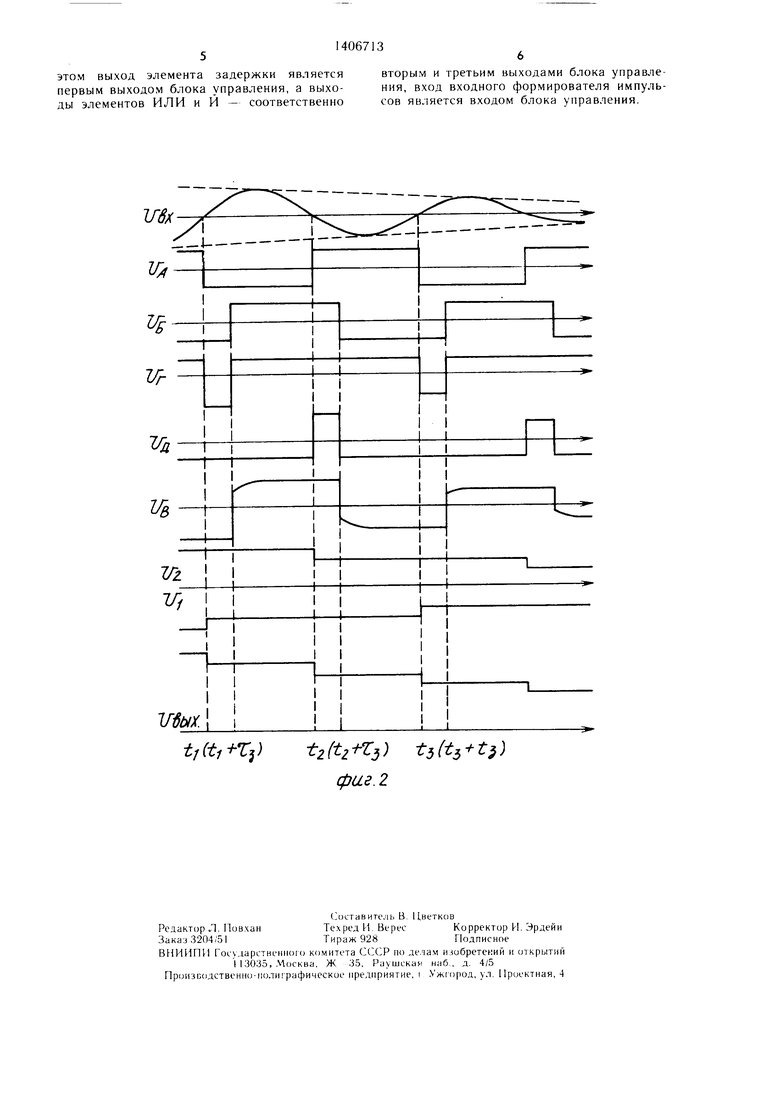

На фиг. 1 представлена функциональная электрическая схема предлагаемого синхронного амплитудного детектора; на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Синхронный амплитудный детектор содержит интегрирующий блок 1 на первом операционном усилителе 2, первом конденсаторе 3, первом резисторе 4, первый 5 и второй 6 блоки выборки-хранения, вычита- тель 7, блок 8 управления, содержащий элемент ИЛИ 9, а также входящие в интегрирующий блок два р-канальных полевых транзистора 10 и 11, два п-канальных полевых транзистора 12 и 13, щесть диодов 14-19, второй 20 и третий 21 резисторы и второй операционный усилитель 22 и входящие в блок управления входной формирователь 23 импульсов, элемент 24 задержки и элемент И 25.

Синхронный амплитудный детектор работает следующим образом.

Информационный сигнал UBX (фиг. 2) и опорный сигнал LJon (не показан) синфазны. Если коэффициент модуляции входного напряжения меньше 100%, то опорное напряжение может выделяться из информационного сигнала, в этом случае два входа синхронного амплитудного детектора объединены. Опорный сигнал подается на вход входного формирователя 23 импульсов, который вырабатывает прямоугольное напряжение UA , противофазное входному напряжению. Снгнал DA поступает на вход элемента 24 задержки и первые входы элементов И 25 и ИЛИ 9. Элемент задержки вырабатывает прямоугольное, инвертированное относительно U« напряжение UB , задержанное на время TJ . Для времени задержки должно выполняться соотнощение тз«1/4- нес, где нес - несущая частота AM сигнала UBX. Напряжение Ue с выхода элемента 24 задержки подается на вторые входы элементов И 25 и ИЛИ 9 и иа управляющий вход интегрирующего блока 1. Интегрирующий блок 1 представляет собой пиковый детектор с переключаемой полярностью детектирования. Работа интегрирующего блока иллюстрируется временными диаграммами (фиг. 2).

На вход интегрирующего блока поступает сигнал UBX. В промежуток времени (ti+тз) - (12-+-тз) транзисторы 10 и 11 закрыты положительным напряжением U , пода5

5

ваемым через пятый диод 18. Транзисторы 12 и 13 открыты, и происходит заряд конденсатора 3 с выхода первого операционного усилителя 2 через открытый канал транзистора 13 и четвертый диод 17 до напряжения, равного максимуму входного напряжения UBX.макс. При этом второй ДИОД 15,

подключенный к выходу первого операционного усилителя 2 через открытый канал транзистора 12, закрыт. Точное соответ0 ствие напряжения на выходе интегрирующего блока 1 напряжению UBX «акс обеспечивается обраной связью с выхода второго операционного усилителя 22 через первый резистор 4 на инвертирующий вход операционного усилителя 2. После достижения выходным сигналом U, величины, равной UBX макс четвертый диод 17 закрывается и открывается второй диод 15, включенный в цепь обратной связи операционного усилителя 2 через открытый канал транзистора 12,

0 защищая таким образом операционный усилитель 2 от перегрузки по напряжению выхода до момента времени (12-Ьтз). В промежуток времени t2-(12+тз) на выходе интегрирующего блока 1 имеется напряжение UB UBX MaKc-j-UcM-f-Uflp, где Uflp - сумма напряжений дрейфа нуля интегрирующего блока 1 и дрейфа нуля на входе детектора; Uf - сумма напряжений смещения нуля на входе детектора и на входе интегрирующего блока 1.

В промежуток времени ((2+тз) - (1з+тз) транзисторы 12 и 13 закрыты напряжением и , поступающим через шестой диод 19, транзисторы 10 и 11 открыты. Конденсатор 3 перезаряжается до напряжения UBX-MHH с выхода операционного усилителя 2 через открытый канал транзистора 11 до напряжения, равного UBX.мин, при этом первый диод 14 закрыт, после чего закрывается диод 16 и открывается диод 14, включенный в цепь обратной связи операционного усилителя 2 через открытый канал транзистора 10, за0 ш-ищая таким образом операционный усилитель 2 от перегрузки по напряжению выхода. В промежуток времени ta-(1з4-тз) на выходе интегрирующего блока 1 имеется напряжение UB UBX MHH-(--UcM-(-Uap. Напряжение Ur , поступающее с выхода элемента ИЛИ 9,

5 запирает блок 5 выборки-хранения и открывает его в промежутки времени ti-(ti + +тз) и {з-(ta-f-Ta). При этом перезаряжается конденсатор блока 5 выборки-хранения и на выходе блока 5 появляется напряжение Ui Ua +идр1, где идр| - напряжение дрейфа нуля блока 5 выборки-хранения.

Блок 6 выборки-хранения закрыт напряжением и и открывается в промежуток времени t2-(ta+ta). Конденсатор блока 6 5 перезаряжается до напряжения U . На выходе блока 6 выборки-хранения появляется напряжение

+идР2(О

0

5

0

где Uflp2 - напряжение дрейфа нуля блока 6

выборки-хранения.

На первом входе вычнтателя, который может быть реализован на операционном усилителе, имеется напряжение Ui, на втором - U2. При условии, что коэффициенты передачи вычитателя по входам равны: К2 - К|, выходное напряжение синхронного амплитудного детектора равно:

UBb, -U2 (Uax-MaKc-f Uc +Uдp-t- -Uдp2)-(UBx.HKH+Uc«-f-U.lp+Uip|) (ивх-макс-и х.мин)-|-(Uap 2-Uap i) (2)

Если активные элементы блоков выборки-хранения выполнены на одном кристалле в течение единого технологического про10

при этом вход блока управления является опорным входом синхронного амплитудного детектора, первый выход блока управления соединен с управляющим входом интегрирующего блока, а второй и третий выходы - с управляющими входами первого и второго блоков выборки-хранения соответственно, отличающийся тем, что, с целью увеличения точности детектирования путем обеспечения независимости коэффициента передачи синхронного амплитудного детектора от величины несущей частоты и величины сдвига фаз между несущей и опорной частотами, в интегрирующий блок введены два р-ка- нальных и два п-канальных полевых транзис20

25

30

цесса (например, микросхема 574УД2), то 5 тора, щесть диодов, второй и третий ре:1ис- ид;|| идр2 и выражение (2) имеет вид

LjBbix LJ вх-максUBX.)

Таким образом, синхронный амплитудный детектор производит измерение размаха амплитудно-модулированного колебания с дискретностью 1/2 периода несущей частоты, коэффициент передачи детектора для размаха АМ-колебаний , причем сдвиги фаз несущей и опорной частот в пределах от -л/2 до (л/2-л-т, f, ) не сказываются на показаниях детектора. При этом ycipa- няются ошибки детектирования, связанные с постоянным смещением и дрейфом нуля на входе детектора, др ейфом и смещением нуля операционных усилителей, а также по- гре1иности детектирования, связанные с точностью поддержания скважности управляющих импульсов и точностью фазирования входного UBX и управляющего напряжений детектора. Точность детектора определяется точностью масщтабных резисторов и может достигать величины десятых Долей процента. Коэффициент передачи детектора для размаха напряжения с частотой, отличной от несущей частоты АМ-колебаний, определяется выражением

If 5(-Р

.-t

где F - частота помехи;

н - несущая частота АМ-колебаний.

Если Гц, а f« 2400 Гц, то Ki 0,0327 и выигрыщ в соотношении сигнал/помеха на выходе детектора составляет -ЗО раз.

Формула изобретения

Синхронный амплитудный детектор, содержащий интегрирующий блок, выполненный на первом операционном усилителе, первом конденсаторе и первом резисторе, выход интегрирующего блока через первый и второй блоки выборки-хранения подключен

35

40

45

50

торы и второй операционный усилитель, при этом неинвертирующий вход первого операционного усилителя является входом интегрирующего блока, инвертирующий вход соединен с катодом первого и анодом второго диодов и с первым выводом первого резистора, выход первого операционного усилителя соединен с первыми выводами первого и второго р-канальных полевых транзисторов, с первыми выводами первого и второго п-канальных полевых транзисторов i; через второй и третий резисторы - с управляющими выводами соответственно второго р-канального полевого транзистора и второго п-канального полевого транзистора, второй вывод первого р-канального полевого транзистора соединен с анодом первого диода, второй вывод первого п-канального полевого транзистора соединен с катодом второго диода, второй вывод второго р-канального по левого транзистора подсоединен к катоду третьего диода, второй вывод второго п-канального полевого транзистора подсоединен к аноду четвертого диода, анод третьего диода соединен с катодом четвертого диода, с неинвертирующим входом второго операционного усилителя и с первым выводом первого конденсатора, второй вывод которого соединен с общей щиной, управляющие выводы первого и второго р-канальных полевых транзисторов подключены к катоду пятого диода, управляющие выводы первого и второго п-канальных полевых транзисторов подключены к аноду щестого диода, катод которого соединен с анодом пятого диода и является управляющим входом интегрирующего блока, второй вывод первого резистора соединен с инвертирующим входом второго операционного усилителя, с выходом второго операционного усилителя, который является выходом интегрирующего блока, а в блок управления введены последовательно соединенные входной формирователь импульсов и элемент задержки, а также элемент И, причем выход входного формиросоответственно к первому и второму входам 55 вателя импульсов соединен с первыми входами элемента И и элемента ИЛИ, а выход элемента задержки соединен с вторыми входами элемента И и элемента ИЛИ, при

вычитателя, выход которого является выходом синхронного амплитудного детектора, и блок управления, содержащий элемент ИЛИ,

при этом вход блока управления является опорным входом синхронного амплитудного детектора, первый выход блока управления соединен с управляющим входом интегрирующего блока, а второй и третий выходы - с управляющими входами первого и второго блоков выборки-хранения соответственно, отличающийся тем, что, с целью увеличения точности детектирования путем обеспечения независимости коэффициента передачи синхронного амплитудного детектора от величины несущей частоты и величины сдвига фаз между несущей и опорной частотами, в интегрирующий блок введены два р-ка- нальных и два п-канальных полевых транзис0

5

0

5 тора, щесть диодов, второй и третий ре:1ис-

5

0

5

0

торы и второй операционный усилитель, при этом неинвертирующий вход первого операционного усилителя является входом интегрирующего блока, инвертирующий вход соединен с катодом первого и анодом второго диодов и с первым выводом первого резистора, выход первого операционного усилителя соединен с первыми выводами первого и второго р-канальных полевых транзисторов, с первыми выводами первого и второго п-канальных полевых транзисторов i; через второй и третий резисторы - с управляющими выводами соответственно второго р-канального полевого транзистора и второго п-канального полевого транзистора, второй вывод первого р-канального полевого транзистора соединен с анодом первого диода, второй вывод первого п-канального полевого транзистора соединен с катодом второго диода, второй вывод второго р-канального по левого транзистора подсоединен к катоду третьего диода, второй вывод второго п-канального полевого транзистора подсоединен к аноду четвертого диода, анод третьего диода соединен с катодом четвертого диода, с неинвертирующим входом второго операционного усилителя и с первым выводом первого конденсатора, второй вывод которого соединен с общей щиной, управляющие выводы первого и второго р-канальных полевых транзисторов подключены к катоду пятого диода, управляющие выводы первого и второго п-канальных полевых транзисторов подключены к аноду щестого диода, катод которого соединен с анодом пятого диода и является управляющим входом интегрирующего блока, второй вывод первого резистора соединен с инвертирующим входом второго операционного усилителя, с выходом второго операционного усилителя, который является выходом интегрирующего блока, а в блок управления введены последовательно соединенные входной формирователь импульсов и элемент задержки, а также элемент И, причем выход входного формиро вателя импульсов соединен с первыми входами элемента И и элемента ИЛИ, а выход элемента задержки соединен с вторыми входами элемента И и элемента ИЛИ, при

этом выход элемента задержки является первым выходом блока управления, а выходы элементов ИЛИ и И - соответственно

tr( tzitz+T,,} ti(t + t}}

фаг. 2

вторым и третьим выходами блока управления, вход входного формирователя импульсов является входом блока управления.

| Синхронный детектор | 1976 |

|

SU657581A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-30—Публикация

1986-02-17—Подача