Изобретение относится к электротехнике и может быть использовано для управления транзисторшлм ин верторсм с рег улируемой частото вьколи ого напряжения, например, п системах электропринода,

LU-ль изобретения - уменьшение массы габаритс в устройства ;и1я управления иниертором путем уменьшения времени выключения трамзистороа.

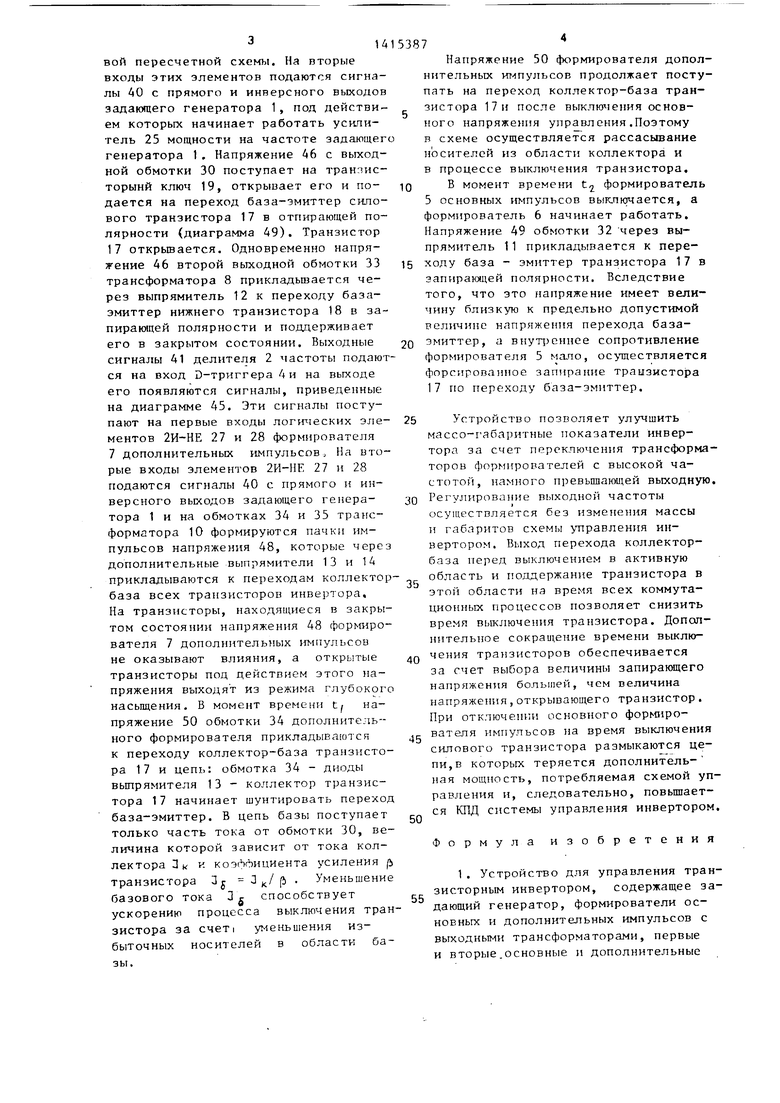

На фиг,1 показана схема устройства; на фиг.2 - временные диаграммы, поясняющие его paPoiy.

Устройство содержит задающий генератор 1, делитель 2 частоты, кольцевую пересчетн то схему 3, D-триг- гер 4, формир-)ва те ли основных 5 и 6 Л дополнительных 7 1 мпульсов уп- равлб нил с BbrxonHbiMTi трансформаторами 8-1Г), основные 11 и 12, лопол- ните-пьные 13 и 14 и нспомогательные 15 и 16 вьптрямитеш, силовые 17 и 18 и дополнительные 19 и 20 транзисторы. Количестве формирователей основных импульсов и число ячеек кольцевой пересчетной схемы определяется числом фаз 1тнт;ертора, т.е. (количеством транзисторов. Формирователь до- полн1 тельн1 гх импульсов iiMeeT число выхо/ ных обмоток, равное числу транзисторов, 1 орм;1розатели 5 и 6 основ- ньк и догк1лнительиьп импульсов выполнены на элеме 1тах 2li-}lE 21-24 и усилителях 2S и 26 мощности. Формирователь 7 всп эмогательнсгч импуль1;ов управления выполнен по такой же схеме и содержит логические элементы 27 н 28 и уси,:итель 29 мощности.

Задающий генератор 1 имеет прямой и инверсный ныходы, которые подключены к входу делителя частоты и к вторым входам логических элементов 2И-НЕ 21-24, 27 и 28. Пртем оди элемент 2И-НЕ (21, 23 и 27) каждого формирователя (5-7) подключен к прямому выходу задающего генератора, а другс)й (22, 24 и 28) к инверсному. Синхронизирующий вход кольцевой ие- ресчетной схемы 3 подключен к входу D-триггера 4 и выходу делителя 2 частоты. Кольдевая пересчетиая схема вьтолнена из отдельных ячеек, каждая из которых имеет прямой и инверсный вькоды. Прямой выход одной ячейки пстдключен к 1КМЧ1ЫМ rixoaaM Л1 гиче- ских элементов JH-iU 21 и 22 ф11рми- рователи 5 (n-Hnniiiiix импучьсмн, л

0

5

0

5

0

5

0

5

0

5

инверсный В1,гход, к первым входам ло- 1Л ческих :)лементов 2И-НЕ 23 и 24 формирователя 6. Пе;: Вые вторичные обмотки 30 и 31 транформаторов 8 и 9 формировач слей 3 и 6 через вспомогательные вьифямители 15 и 16 и дополнительные 19 и 20 транзисторы связаны с переходами база-эмиттер верхнего 17 и нижнего 18 транзисторов стойки инвертора. Вторые вторичные 32 и 33 обмотки через основные выпрямители 11 и 12 подключены к переходам база-эмиттер нижнего и верхнего транзисторов. Выходные обмотки 34 и 35 трансформатора 10, формирователя 7 дополнительных импульсов через дополнительные 13 и 14 вьп1ряму1тели связан1.1 с переходом 1 ;оллектор-база силовых транзисторов. Для исключения работы транзисторов в ин- pe(HNie в цепи коллекторов вк1;;очены силовые 36 и 37 и обратные 8 и 39 диоды.

На фиг.2 показаны: выходное напряжение 40 задающего генератора, 41 - делителя частоты; 42-44 - кольцевой перосчегной схемы; 45 - D-триггера. Ня диаграммах 46 и 47 показано напряжение на выходных обмотках формирователей основных, а на диаграмме 48 - дополнительных импульсов, суммарное напряжение управления на переходе база-эмиттер транзистора приведено на диаграмме 49. Напряжение на переходах коллектор-база транзисторов имеет шщ в соответствии с диаграммой 50.

Устройство работает следующим образом.

При подаче питающего напряжения на выходах задающего генератора 1 появляются импульсы напряжения 40 требуемой длительности, которые поступают на делитель 2 частоты. Выходные импульсы 41 делителя 2 частоты синхронизируют работу кольцевой пересчет- ной схемы 3, напряжения на прямых вь ходах ячеек кот(фой для трехфазного инвертора имеет вид в соответствии с диаграммами 42-44.

Принцип действия устройства управления инвертором рассмотрим на примере работы стойки, так как остальные стойки 11,1(чггаю. аналогично.

В момент t - (:„ на первые BxOjii) . т мч ее ких мрмелтов 2И-11Е 21 и 22 . напряжение 42 с ньгхода чг|1но 1 кольце 14

вой пересчетной схемы. На вторые входы этих элементов подаются сигналы АО с прямого и инверсного выходов задающего генератора 1, под действием которых начинает работать усилитель 25 мощности на частоте задающег генератора 1. Напряжение А6 с выходной обмотки 30 поступает на транзис- торынй ключ 19, открывает его и подается на переход база-эмиттер силового транзистора 17 в отпирающей полярности (диаграмма 49). Транзистор 17 открьюается. Одновременно напряжение 46 второй выходной обмотки 33 трансформатора 8 прикладьшается через выпрямитель 12 к переходу база- эмиттер нижнего транзистора 18 в запирающей полярности и поддерживает его в закрытом состоянии. Выходные сигналы 41 делителя 2 частоты подаются на вход D-триггера 4 и на выходе его появляются сигналы, приведенные на диаграмме 45. Эти сигналы поступают на первые входы логит 1еских элементов 2И-НЕ 27 и 28 формирователя 7 дополнительных импульсов, На вторые входы элементов 2И-НЕ 27 и 28 подаются сигналы 40 с прямого и инверсного выходов задающего генератора 1 и на обмотках 34 и 35 трансформатора 10 формируются пачки импульсов напряжения 4В, которые через дополнительные выпрямители 13 и 14 прикладываются к переходам коллектор база всех транзисторов инвертора. На транзисторы, находящиеся в закрытом состоянии напряжения 48 форьшро- вателя 7 допол}П1тельных импульсов не оказывают влияния, а открытые транзисторы под действием этого напряжения выходят из режима глубокого насыщения. В момент времени t напряжение 50 обмотки 34 дополнительного формирователя прикладываются к переходу коллектор-база транзистора 1 7 и цепь: обмотка 34 - диоды выпрямителя 13 - коллектор транзистора 17 начинает шунтировать переход база-эмиттер. В цепь базы поступает только часть тока от обмотки 30, величина которой зависит от тока коллектора Лк и коэббициента усиления (Ь транзистора 3j 3 / fi . Уменьшение базового тока 3 способствует ускорению процесса выключения транзистора за счеТ| уменьшения избыточных носителей в области базы.

7

Напряжение 50 формирователя дополнительных иг пульсов продолжает поступать на переход коллектор-база тран- зистора 17 и после выключения основного напряжения управления.Поэтому в схеме осуществляется рассасьшание носителей из области коллектора и в процессе выключения транзистора,

В момент времени t формирователь 5 основных импульсов выкпючается, а формирователь 6 начинает работать. Напряжение 49 обмотки 32 через выпрямитель 11 прикладывается к переходу база - эмиттер транзистора 17 в запирающей полярности. Вследствие того, что это напряжение имеет величину близкую к предельно допустимой величине напряже1П1я перехода базаэмиттер, а внут1)еннее сопротивление формирователя 5 ма.по, осуществляется форсированное запирание транзистора 17 по переходу база-эмиттер.

Устройство позволяет улучшить массо-г абаритные показатели инвертора за счет переключения трансформаторов формирователей с высокой частотой, намного превьш1ающей выходную,

Регулирование В1 1ходной частоты

осуществляется без изменения массы и габаритов схемы управления инвертором. Выход перехода коллектор- база перед выключением в активную область и поддержание транзистора в этой области на время всех коммутационных процессов позволяет снизить время выключения транзистора. Дополнительное сокращение времени выключения транзисторов обеспечивается за счет выбора величины запирающего напряжения большей, чем величина напряжения,открывающего транзистор. При отключении основного формирователя импульсов на время выключения силового транзистора размыкаются цепи, в которых теряется дополнитель- пая мощность, потребляемая схемой управления и, следовательно, повьщгает- ся КПД системы управления инвертором.

55

Формула изобретения

1. Устройство для управления транзисторным инвертором, содержащее задающий генератор, формирователи основных и дополнительных импульсов с выходными трансформаторами, первые и вторые.основные и дополнительные

51

вьтрямители, формирователи основных и дополнительных импульсов, первый и второй входы которых подключены к прямому и инверсному выходам задающего генератора, выходы первого и второго основных выпрямителей соединены соответственно с переходами база-эми тер верхнего и нижнего силовых транзисторов стойки инвертора, выходы дополнительных вьтрямителей подключены к переходам коллектор-база силовых транзисторов, отличающееся тем, что, с целью уменьшения массы и габаритов инвертора путем уменьшения времени выключения транзисторов, устройство снабжено делителем частоты, D-триггером,кольцевой пересчетной схемой, выполненной на ячейках с синхронизирующим входом и прямым и инверсным выходами, вспомогательным формирователем импульсов с выходным трансформатором, транзисторными ключами и вспомогательными выпрямителями, причем выходные транформаторы основных, дополнительных и вспомогательных формирователей импульсов выполнены с дополнительными обмотками, выходы задающего генератора связаны с входами делителя частоты, вькодом подключенного к синхронизирующим входам ячеек кольцевой пересчетной схемы и входу D-триггера, первый и второй входы формирователя вспомогательных импульсов соединены с прямым и инверсным выходами задающего генератора, третьи входы основного и дополнитель5387

ного формирователей импульсов подключены к прямому и инверсному выходам первой ячейки кольцевой пересчетной схемы, а третий вход формирователя вспомогательных импульсов соединен с выходом D-триггера, основные выходные обмотки трансформаторов формирователей основных и дополнительных им Q пульсов через вспомогательные выпрямители и транзисторные ключи подключены к переходам база-эмиттер силовых транзисторов, дополнительная обмотка трансформатора формирователя основных

g импульсов подключена к входу второго основного вьшрямителя, дополнительная обмотка транформатора формирователя дополнительных импульсов связана с входом первого основного вы-; прямителя, основные и дополнительные обмотки трансформатора формирователя вспомогательных импульсов соединены с входами дополнительных выпрямителей.

5 2. Устройство по п. 1, отличающееся тем, что формирователи основных, дополнительных и вспомогательных импульсов содержат два логических элемента 2И-НЕ и усилитель

0 мощности, первые входы логических

элементов 2И-НЕ образуют первые и вторые входы формирователей, вторые входы логических элементов 2И-НЕ образуют третьи входы формирователей, выходы логических элементов 2И-НЕ связаны с входами усилителей мощности, выходами соединенными с первичными обмотка- ми выходных трансформаторов.

0

5

4/

ПППППППП П П Г11 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления стойкой инвертора | 1985 |

|

SU1292141A1 |

| Устройство для управления стойкой инвертора | 1986 |

|

SU1394377A1 |

| Полумостовой инвертор | 1986 |

|

SU1325648A1 |

| Инвертор | 1981 |

|

SU1101998A1 |

| Преобразователь частоты | 1983 |

|

SU1164845A1 |

| Инвертор | 1981 |

|

SU1015476A1 |

| Стабилизированный конвертор | 1979 |

|

SU892425A1 |

| Стабилизированный инвертор | 1981 |

|

SU964908A1 |

| СТАБИЛИЗИРОВАННЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ С ЦИФРОВЫМИ МИКРОСХЕМАМИ | 1991 |

|

RU2014713C1 |

| Двухтактный инвертор | 1990 |

|

SU1746502A1 |

Изобретение относится к электротехнике и может быть использовано в стати ескпх преобразователях. Цель изобретения - уменьшение массы и габаритов инвертора. Устройство содержит задаюиип генератор 1 , подключенный к Нересчетнои схеме 3 и D- триггеру 4. Число формирователей основных 5, 6 и дополнительных 7 им- нульсов определяется числом фаз инвертера. Переключение трансформаторов В, 9, 10 осуществляется с высокой частотой, превышающей выходную. Выход перехода коллектор - база перед вк1почением в активную область и поддержание транзистора в этой области на время коммутационных процессов позволяют снизить время выключения транзистора. 1 з.п. ф-лы, 2 ил. С S (Л СП со сх Фи2.1

1

Г

, i.

шшлшмь

jy

4Hf

Iia.

I IjlJ

i-Hftr

, 1 г

.- . -.. - .

Составитель С, Белово;) -:1-М Кп

Редактор Н.Слободяннк Техред А.Краячук

Заказ 3882/53 .Тираж 665 i ojiii; CH..p

ВНИИПИ Государствеинпго кp inтeтя СССР

по делам изобретений и отк:рытяй 113035, Москва, Ж-35, Раушская нпГ., д. А/3

Iia..Ji,

I IjlJiilUji:

i-Hftr f i.

I .1

iPuz 2

KoppL/K тпр ; ; ;

| Транзисторный инвертор | 1979 |

|

SU788313A2 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Инвертор | 1981 |

|

SU1101998A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1988-08-07—Публикация

1986-04-21—Подача