4::

1чЭ f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обращения матриц | 1987 |

|

SU1527643A1 |

| Устройство для матричных операций | 1987 |

|

SU1429127A1 |

| Устройство для операции над матрицами | 1987 |

|

SU1534470A1 |

| Устройство для обращения матриц и решения систем линейных уравнений | 1987 |

|

SU1444820A1 |

| Устройство для LU-разложения матриц | 1986 |

|

SU1401478A1 |

| Устройство для вычисления собственных значений ( @ @ @ ) - матрицы | 1989 |

|

SU1721611A1 |

| Устройство для обращения плотных ( @ х @ ) матриц | 1986 |

|

SU1387013A1 |

| Устройство для вычисления деконволюции | 1987 |

|

SU1494017A1 |

| Устройство для разложения теплицевых симметричных матриц | 1990 |

|

SU1755295A2 |

| Устройство для вычисления двумерного дискретного преобразования Фурье | 1990 |

|

SU1751778A1 |

Изобретение относится к вычислительной технике и может быть использовано для обращения матриц. Цель изобретения - повышение быстродействия. Устройство содержит операционные блоки, регистры, элементы задержки. Поставленная цель достигается за счет соответствующей структурной организации устройства. 3 з.п. .ф-лы, 5 ил.

JO

О5

Изобретение относится к вычислительной технике и может быть исполь-- зёвано для обращения ()-матриц.

Цель изобретения - повьшение быстродействия устройства.

U-l) (

ЕМ /а , k4 j -.n+k а7Г-а Г a , 1 U n, k 4 П n+k

,-)

1 « 1 4П, U J 4П

35

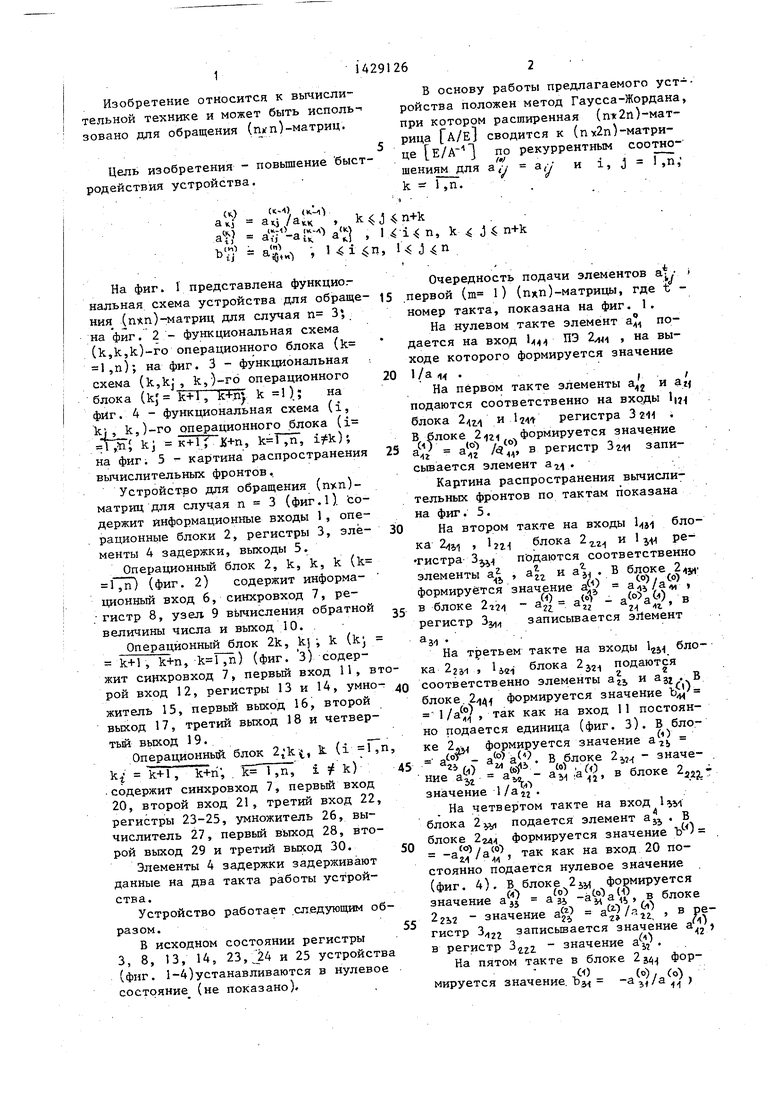

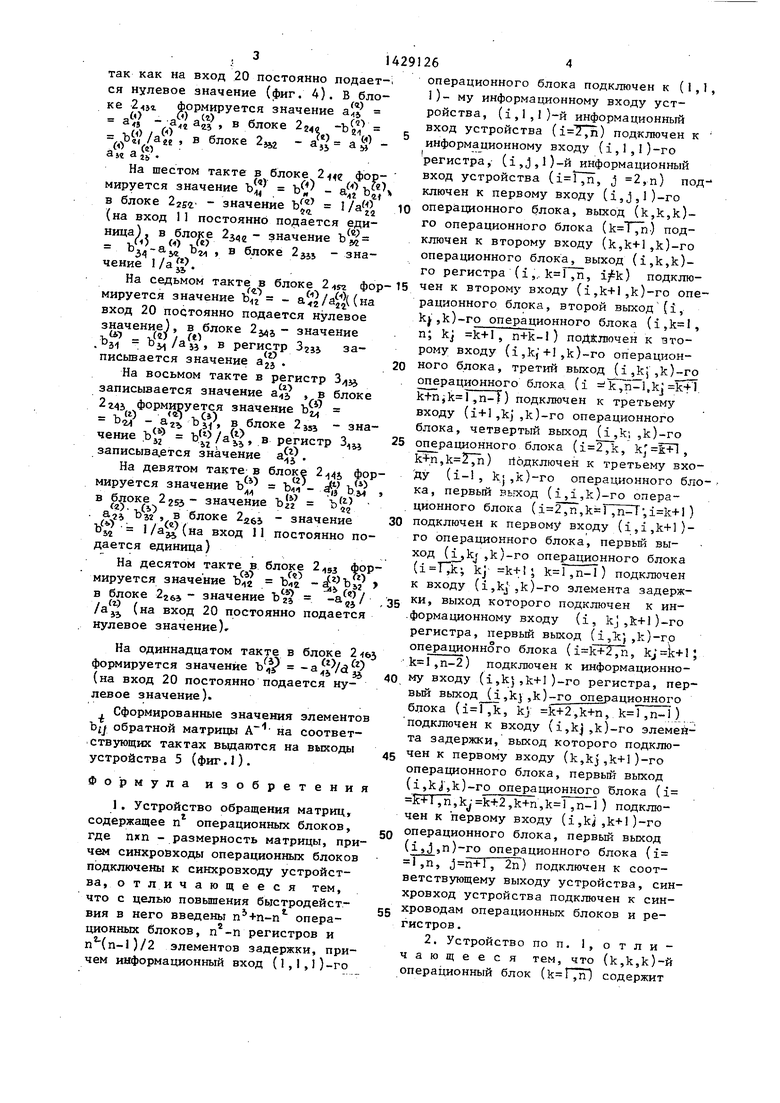

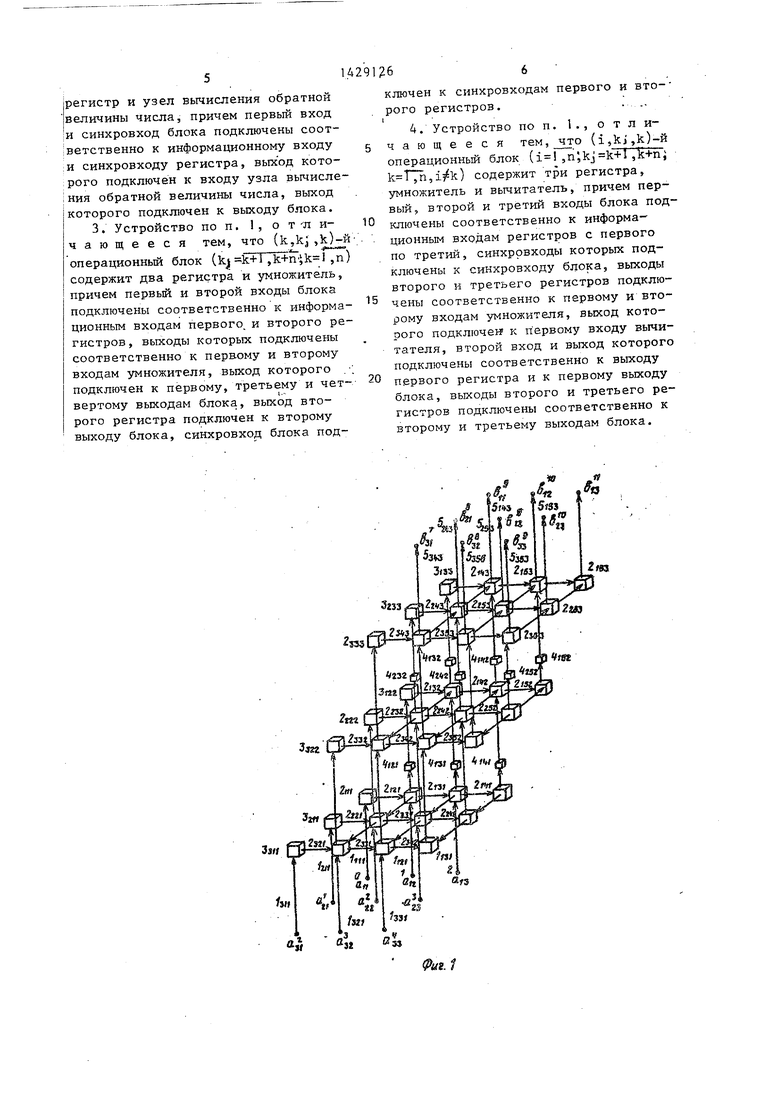

Ha фиг. I представлена функцио.- альная схема устройства для обраще- t5 ия (пкп)-матриц для случая п 3, а фиг. 2 - функциональная схема k,k,k)-ro операционного блока (k 1,п); на фиг, 3 - функциональная хема (k,kj, k,)-r6 операционного 20 лока (kj k+1, k+.ny k l); на иг. 4 - функциональная схема (i, i,k,)-ro рперационного.блока (i 1,, kj -K+i; Ji+n, ,n, ); а фиг; 5 - картина распространения 25 ычислительных фронтов,

Устройство для обращения (nicn)- атриц для случая п 3 (фиг.1). to- ержит информационные входы 1, операционные блоки 2, регистры 3, эле- 30 енты 4 задержки, выходы 5.

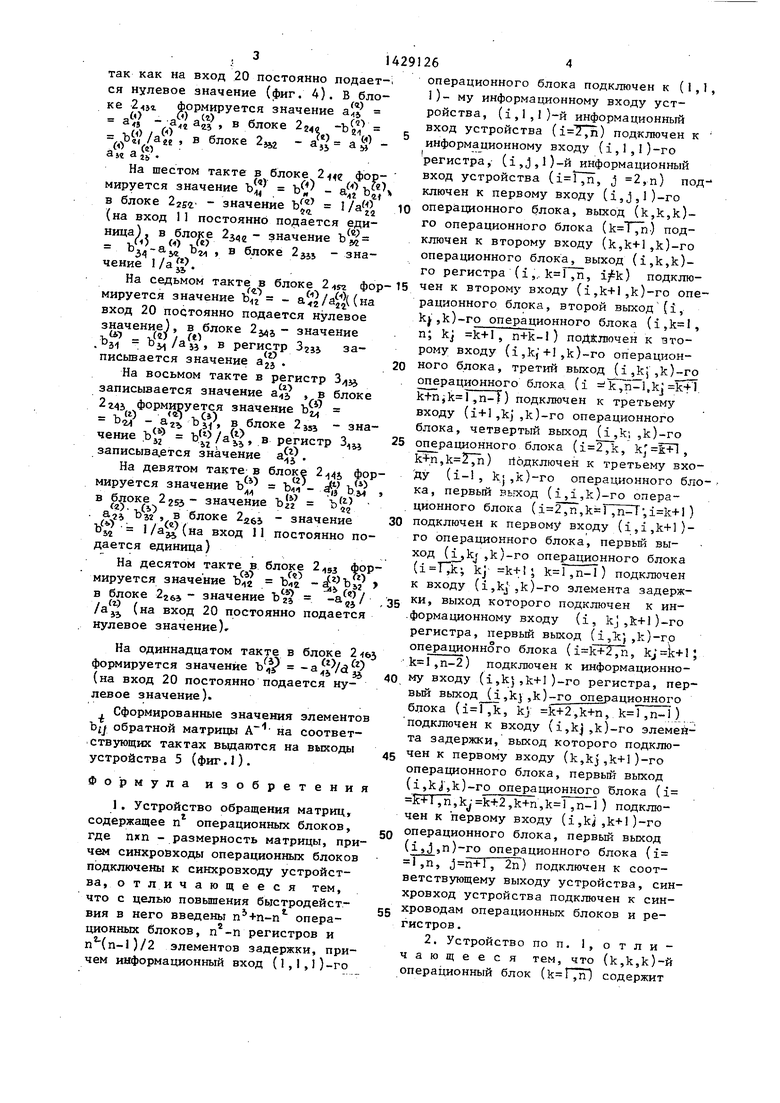

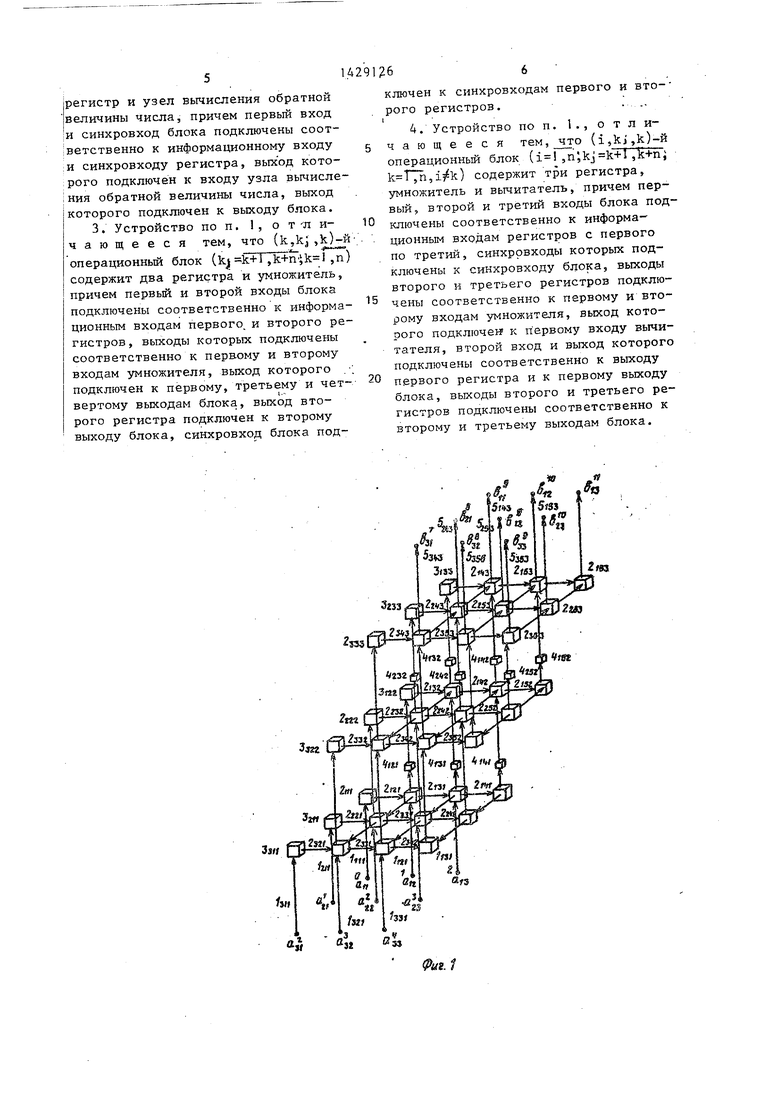

Операционный блок 2, k, k, k (k Г,n) (фиг. 2) содержит информа- ционный вход 6, синхровход 7, ре- гистр 8, узел 9 вьгчисления обратной величины числа и выход 10. .

Операционный блок 2k, kj , k (kj «3 k+1, k+n, ,n) (фиг. з) содержит сиихровход 7, первый вход 11, второй вход 12, регистры 13 и 14, умно-: Q житель 15, первьй выход 16, второй выход 17, третий вькод 18 и четвер- тьй выход 19..

Операционньй блок , k. (i l,n,

k k+1, k+ri; . k l,n, i f k) 45 содержит синхровход 7, первьй вход 20, второй вход 21, третий вход 22, регистры 23-25, умножитель 26, вычислитель 27, первый выход 28, второй выход 29 и третий выход 30. 50

Элементы 4 задержки задерживают данные на два такта работы устройства.

Устройство работает .следующим образом.55

В исходном состоянии регистры 3, 8, 13, 14, 23, J4 и 25 устройства (фиг. 1-4)устанавливаются в нулевое состояние (не показано).

перв номе

дает ходе 1/а

пода блок В бл сьюа

тель на ф

ка гист элем форм в бл рег

ка

соо

блок

1 но

ке

а

ние зна

бло бло сто (фи

зна 222,2 гис в р

мир

В основу работы предлагаемого устройства положен метод Гаусса-Жордана, при котором расширенная ()-MaT- рица ГА/Е сводится к (пу2п)-матрице E/fc l по оекуррентньм соотнощениям для а j k - ,

по рекуррентньм

fV

а

/

и

J Un,1 « 1 4П, U J 4П

5

0 5

0

«3 Q

Очередность подачи элементов первой (т 1) (пцп)-матрицы, где t - номер такта, показана на фиг. 1.

На нулевом такте элемент aj;, подается на вход 1 ПЭ 2л4 « на выходе которого формируется значение 1/а„ ., ,

На первом такте элементы , и ац подаются соответственно на входы j блока .1 и регистра Зги . В блоке 2121 формируется значение / 3°д. в регистр 3zii запи- сьюается элемент .

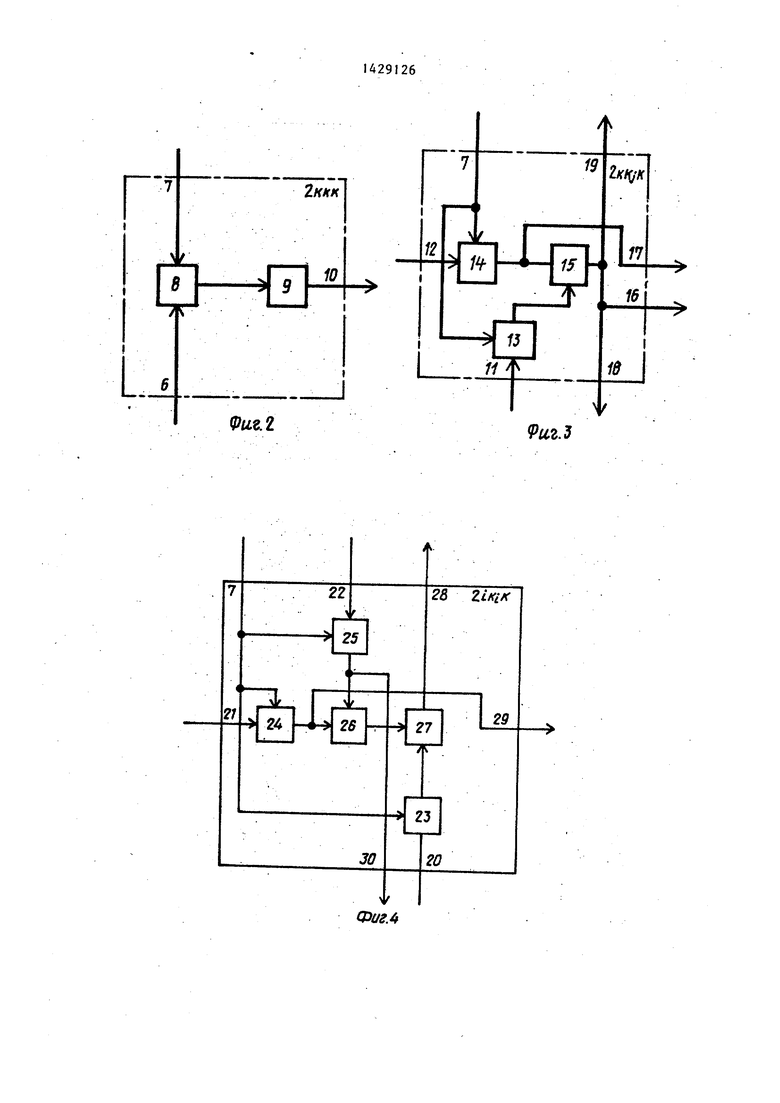

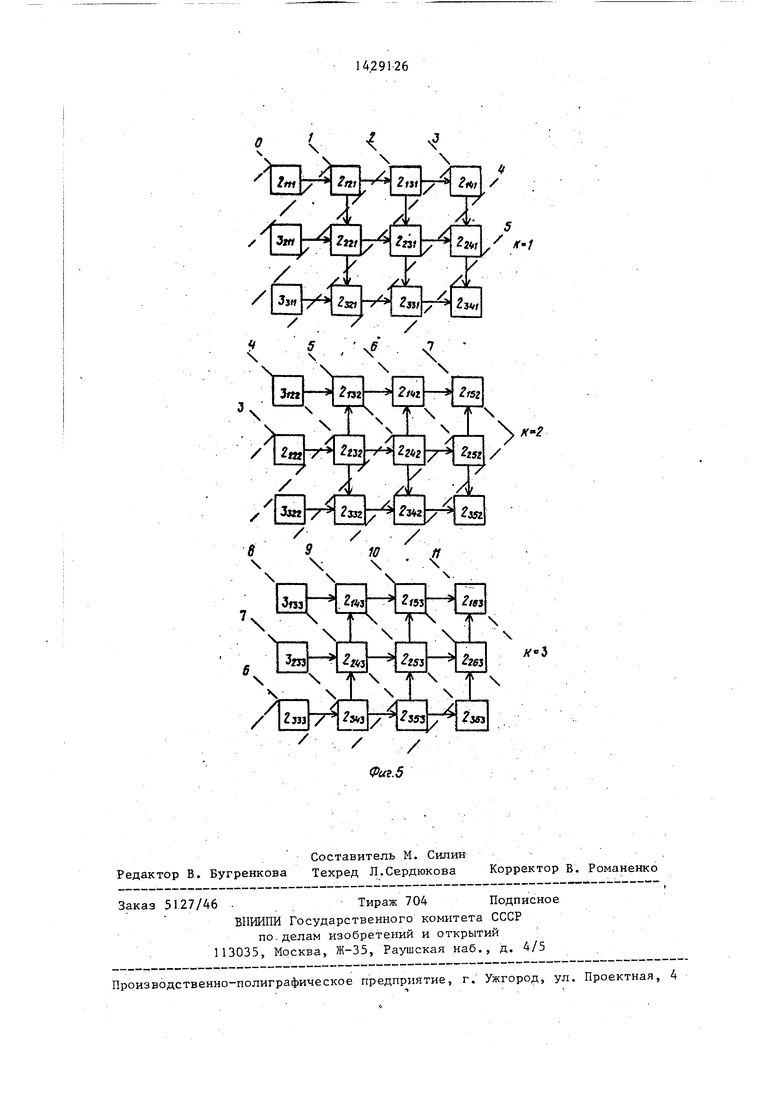

Картина распространения вычислительных фронтов по тактам показана на фиг. 5.

На втором такте на входы блока г,5т , 1гг1 блока 2 и 1 ре- гистра- подаются соответственно элементы а , а| и а . В блоке 2. формируется значение а , в блоке 2„-, - , в регистр 3j/, записывается элемент

«3

На третьем такте на входы блока 22 л , Ij2i блока 2 32 подаются

соответственно элементы а,

и аз,...В

чь блоке. формируется значение

1 , так как на вход 11 постоянно подается единица (фиг. 3). В блоке 2,j формируется значение а

)- -. «Г -ъг ..,- 51 ° 2.

а

ние значение 1 /а .

На четвертом такте на вход Ц блока 2уу, подается элемент aj , В блоке 2г4 формируется значение Ъ ) , так как на вход 20 постоянно подается нулевое значение (фиг. 4). В блоке 2jy формируется

значение а 35 , в блоке 222,2 значение а Р гистр записьшается значение ) в регистр 2.г значение , .

На пятом такте в блоке 2з формируется значение. Ъ -а,

. 3

так как на вход 20 постоянно лодается нулевое значение (фиг. 4). В блоке формируется значение аД а ; - aV,ai|. в блоке 2щ )« ° 2 - ag -

Э J« 3 2Ь

На шестом такте в блоке фор- мируется значение bv - а Ь в блоке 22Si значение 1/а

(на вход 11 постоянно подается единица) . в блоке 2з4е значение Ь Ь,.-а. Ь« . в блоке 2и. - чня -

° 23ij

чение I/aj|

На седьмом такте в блоке фор мируется значение Ь - ({на вход 20 постоянно подается нулевое значение), в блоке 2,- значение .31 - в регистр 3гji за- письюается значение

На восьмом такте в регистр записывается значение а , в блоке 2 243 формируется значение Ь Ьт - 2 в блоке 2}53 значение , в регистр

записыва.ется значение а.

Сг)

15

На девятом такте в блоке Формируется значение Ь - ь - ь м в блоке 2255- значение bi Ъ

э,2д Ьм , в блоке - значение 1/а(па вход 11 постоянно подается единица)

На десятом такте в блоке фор,Сд7 ,f« )

мируется значение 5j; ьг в блоке 22ва - значение bz i я1 /а (на вход 20 постоянно подается нулевое значение)

На одиннадцатом такте в блоке формируется значение (на вход 20 постоянно подается нулевое значение).

Сформированные значения элементов bij обратной матрицы на соответствующих тактах вьщаготся на выходы устройства 5 (фиг.1).

Формула изобретения

что с целью повьшения быстродейст-

г., г.

ВИЯ в него введены n +n-n операцмонных. блоков, п -п регистров и пМп-1)/2 элементов задержки, причем информационный вход (1,1,1)-го

91

0

5 0

5

0

5

5

5

0

264

операционного блока подключен к (1,1, 1)- му информационному входу устройства, (i,1,1 )-й информационный вход устройства (,h) подключен к информа 1ионному входу (1,1 ,1 )-го регистра , (1 ,J , 1)-и информационный вход устройства (,п, j 2,п) под- ключен к первому входу (i,j,l)-ro операционного блока, выход (k,k,k)- го операционного блока (,n.) подключен к второму входу (k,k+l,k)-ro операционного блока, выход (i,k,k)- го регистра (1,.. k ,п, ) подключен к второму входу (i,k+l,k)-ro операционного блока, второй выход (1, ky,k)-ro операционного блока (i,, п; kj k+l, n+k-1) подключен к второму входу (1 ,k, +1 ,k)-ro операционного блока, третий выход (i,ki,k)-ro операционного блока (1 - .kj k+1 ktnik l,n-l) подключен к третьему входу (1 + 1 ,1с ,k)-ro операционного блока, четвертый выход (i,ki ,k)-ro операционного блока (,k, kj Ь+1, k-l-n,,h) йодключен к третьему вхо- ду (1-1, k ,k)-ro операционного блока, первый выход (i,i,k)-ro операционного блока (,n, ,п-1 , ) подключен к первому входу (i,i,k+l)- го операционного блока, первый выход (i,kj,k)-ro операционного блока (i T7k ; kj- k+l ; ,n-l) подключен к входу (i,kj,k)-ro элемента задержки, выход которого подключен к информационному входу (1, kJ,k+l)-го регистра, первый выход (i,c),k}-ro операционного блока (,п, ,n-2) подключен к информационному входу (i,kj,k+l)-го регистра, первый выход (i,ky,k)-ro операционного блока (, kJ k+2,k+n, ,n-l подключен к входу (i,kj,k)-ro элемента задержки, выход которого подключен к первому входу (k,kj,k+l)-го операционного блока, первый выход (l,kj,k)-rp операционного блока (1 k+1, п, k; ,k+n,k 1 , n-1 ) подключен к первому входу (i,k i ,k+l )-го операционного блока, первый выход (1,J,п)-го операционного блока (1 1 ,п, 2п) подключен к соответствующему выходу устройства, син- хровход устройства подключен к син- хроводам операционных блоков и регистров.

2, Устройство по п. , отличающееся тем, что (k,k,k)-й операционный блок (,п) содержит

регистр и узел вычисления обратной величины числа, причем первый вход :и синхровход блока подключены соот- ;ветственно к информационному входу :И синхровходу регистра, выход которого подключен к входу узла вычисле- Iния обратной величины числа, выход I которого подключен к выходу блока. I 3, Устройство по п. 1 , о т -л и- |чающееся тем, что (k,kj,k)-й onерационный блок (kj k+l , 1 ,n) содержит два регистра и умножитель, причем первый и второй входы блока подключены соответственно к информа- ционньм входам первого, и второго регистров, выходы которых подключены соответственно к первому и второму входам умножителя, выход которого .; подключен к первому, третьему и чет- вертому выходам блока, выход второго регистра подключен к второму выходу блока, синхровход блока под3«,0IS

5

0

ключен к синхровходам первого и второго регистров.. , .t

/

/

У«3

| Седухин С.Г | |||

| Параллельная интерпретация прямых методов линейной алг ебры | |||

| Программирование, 1984, № 4, с | |||

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Устройство для обращения плотных ( @ х @ ) матриц | 1986 |

|

SU1387013A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-07—Публикация

1987-02-05—Подача