(Л

4

00 о: гч:) ю

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизирующий источник электропитания | 1983 |

|

SU1149355A1 |

| Релейно-импульсный стабилизатор постоянного напряжения | 1990 |

|

SU1758640A1 |

| Многофазный резонансный стабилизатор | 1989 |

|

SU1697062A1 |

| Преобразователь напряжения постоянного тока | 1984 |

|

SU1257776A1 |

| ИСТОЧНИК ПИТАНИЯ | 2011 |

|

RU2479100C1 |

| Формирователь импульсов для управления тиристорами | 1990 |

|

SU1760610A1 |

| Двухтактный преобразователь напряжения | 1980 |

|

SU982161A1 |

| Стабилизированный преобразователь напряжения | 1984 |

|

SU1233249A1 |

| СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ СЕТИ | 2010 |

|

RU2419830C1 |

| Импульсный стабилизатор постоянного напряжения | 1981 |

|

SU1001049A1 |

Изобретение относится к электротехнике и может быть использовано при разработке вторичных источников электропитания. Цель изобретения - уменьшение пульсаций выходного напряжения и повышение надежности устройства при работе в условиях воздействия дестабилизирующих факторов. Введены п D-триггеров 30-1...30-п, D-входы которых подключены к соответст- вуюшим выходам узла коммутации 10, а выходы - к соответствующим входам узлов управления 9-1...9-п, синхронизирующие входы D-триггеров подключены к вы.чоду генератора тактовых импульсов 31. 1 ил.

NJ

Изобретение относится к преобразовательной технике, может быть использовано при разработке стабилизирующих вторичных источников электропитания и является усовершенствованием изобретения по основному авт. св. № 1149355.

Цель изобретения - уменьшение пульсаций выходного напряжения и повышение надежности устройства при работе в условиях воздействия дестабилизируюш,их факторов.

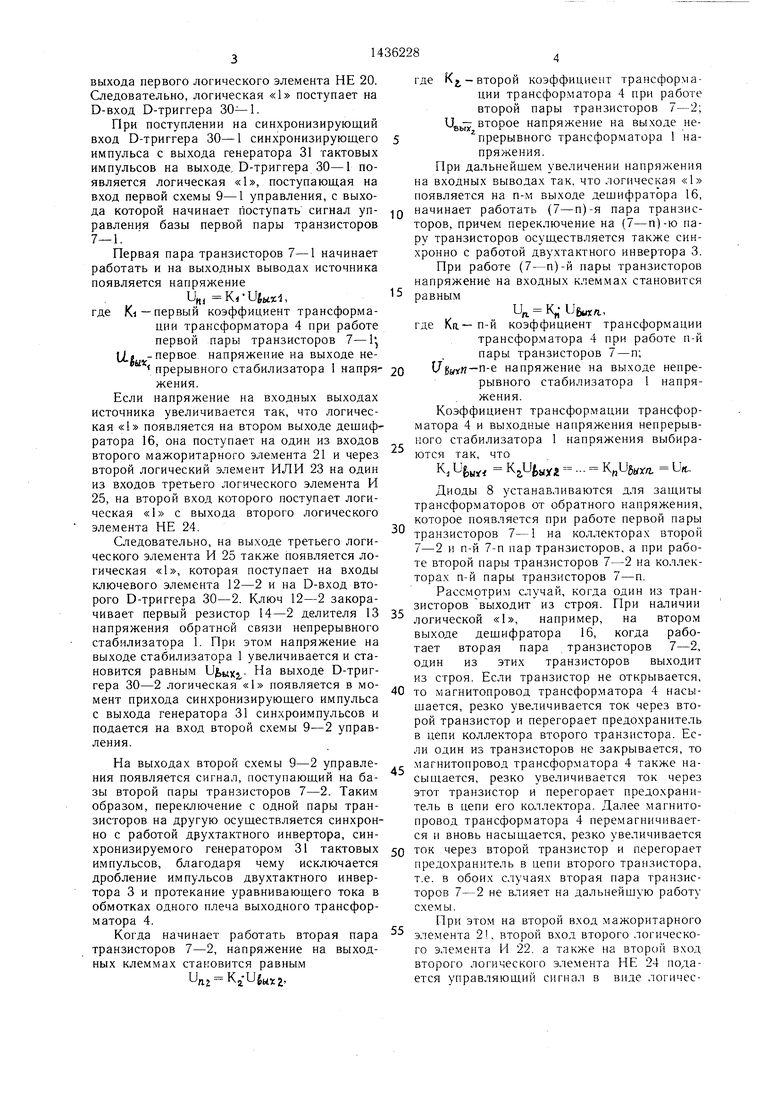

На чертеже представлена структурная схема стабилизируюшего источника электропитания.

Источник электропитания содержит непрерывный стабилизатор 1 напряжения с делителем 2 напряжения, установленный на входе двухтактного инвертора 3, выходной трансформатор 4 которого выполнен с симметричными относительно средней точки первичной обмотки отводами 5-1, 5-2, ..., 5-п, причем первые относительно средней точки отводы 5- 1 подключены к общему выводу источника 6 через коллектор-эмиттерные переходы силовых транзисторов 7-1, а другие отводы - через коллектор-эмиттерные переходы транзисторов 7-2, ..., 7-п и диоды 8, при этом управляющие переходы силовых транзисторов подключены к выходам узлов 9-1, 9-2, ..., 9-п управления. Узел 10 коммутации подключен к выходу резис- тивного делителя 11, подключенного к входным выводам источника, а выходы узла 10 коммутации соединены с соответствующими входами ключевых элементов 12-1, 12-2,..., 12-п, при этом выходы последних подключены к соответствующим выводам нижнего плеча делителя 2 напряжения обратной связи непрерывного стабилизатора 1.

Делитель 2 напряжения обратной связи содержит резистор 13 верхнего плеча и последовательно соединенные резисторы 14-1, 14-2,..., нижнего плеча.

Узел 10 коммутации содержит аналого- цифровой преобразователь 15, вход которого образует входной вывод узла коммутации, а выходы подключены к входам дешифратора 16, первый вход дешифратора 16 подключен к одному из входов первого мажоритарного элемента 17 и одному из входов первого логического элемента ИЛИ 18, выход которого соединен с одним из входов первого логического элемента И 19. Второй вход последнего через логический элемент НЕ 20 соединен с первым управляющим входом источника и вторым входом элемента 17, третий вход которого и второй вход элемента ИЛИ 18 .соединены с выходом второго мажоритарного элемента 21. Выход элемента 17 соединен с первым входом второго логического элемента И 22 и первым входом второго логического элемента ИЛИ 23. Второй вход элемента И 22 соединен с вторым управляющим

входом источника и через логический элемент НЕ 24 с первым входом третьего логического элемента И 25, второй вход которого соединен с выходом элемента ИЛИ 23. Вто- рые входы элементов 23 и 21 соединены с вторым выходом дешифратора 16.

Выход.элемента И 22 соединен с п-логи- ческим элементом ИЛИ 26, второй вход которого соединен с п-выходом дешифратора и вторым входом (2п-2) логического элемента И 27. Первый вход последнего соединен с п-управляющим входом источника и через логический элемент НЕ 28 с первым входом логического элемента И 29, второй вход которого соединен с выходом элемента

5 И 26. Выход элемента И 19 образует первый выход узла 10 коммутации и соединен с D- входом первого D-триггера, выход которого подключен к входу узла 9-1 управления, выход элемента И 25 образует второй выход

- узла коммутации и соединен с входом D второго D-триггера 30-2, выход которого подключен к входу узла 9-2 управления. Выход элемента И 29 образует п-выход узла коммутации и соединен с D-входом D- триггера 30-п, выход которого подключен

5 к входу узла 9-п управления.

Генератор 31 тактовых импульсов, выход которого соединен с синхронизирующими входами D-триггеров 30-1, 30-2,..., ЗОп и с синхронизирующими входами узлов 9-1,

0 9-2, ..., 9-п управления. Предохранители 32 включены в цепь коллекторов транзисторов 7-1, 7-2,..., 7-п.

Устройство работает следующим образом.

В нормальном режиме работы на управ5 ляющие входы источника поступает управляющий сигнал в виде логического «О.

При включении входного напряжения на выходе непрерывного стабилизатора 1 напряжения появляется стабилизированное

0 напряжение Ueuxi , поступающее на среднюю точку первичной обмотки трансформатора 4. На выходе К-разрядного аналого-цифрового преобразователя 15 устанавливается кодовая комбинация, соответствующая напряжению, поступающему с выхода делителя 11

напряжения. При использовании двоичного кода разрядность аналого-цифрового преобразователя определяется по формуле

K log2n, где п - количество симметричных отводов

Qтрансформатора 4, равное количеству выходов дещифратора 16, На одном из выходов дешифратора 16, например на первом, появляется логическая «1, которая поступает на один из входов первого мажоритарного элемента 17 и

5 через первый логический элемент ИЛИ 18 на один из входов первого логического элемента И 19, на втором входе которого присутствует логическая «I, поступающая с

выхода первого логического элемента НЕ 20. Следовательно, логическая «1 поступает на D-вход D-триггера .

При поступлении на синхронизирующий вход D-триггера 30-1 синхронизирующего импульса с выхода генератора 31 тактовых импульсов на выходе, D-триггера 30-1 появляется логическая «1, поступающая на вход первой схемы 9-1 управления, с выхода которой начинает поступать сигнал управления базы первой пары транзисторов 7-1.

Первая пара транзисторов 7-1 начинает работать и на выходных выводах источника появляется напряжение

Utti KrUj«x, где Ki-первый коэффициент трансформации трансформатора 4 при работе первой пары транзисторов 7-1

Ц« -первое напряжение на выходе не прерывного стабилизатора I напря- жения.

Если напряжение на входных выходах источника увеличивается так, что логическая «1 появляется на втором выходе дешифратора 16, она поступает на один из входов второго мажоритарного элемента 21 и через второй логический элемент ИЛИ 23 на один из входов третьего логического элемента И 25, на второй вход которого поступает логическая «1 с выхода второго логического элемента НЕ 24.

Следовательно, на выходе третьего логического элемента И 25 также появляется логическая «1, которая поступает на входы ключевого элемента 12-2 и на D-вход второго D-триггера 30-2. Ключ 12-2 закорачивает первый резистор 14-2 делителя 13 напряжения обратной связи непрерывного стабилизатора 1. При этом напряжение на выходе стабилизатора 1 увеличивается и становится равным Ufrtiixj,- выходе D-триггера 30-2 логическая «1 появляется в момент прихода синхронизирующего импульса с выхода генератора 31 синхроимпульсов и подается на вход второй схемы 9-2 управления.

На выходах второй схемы 9-2 управления появляется сигнал, поступающий на базы второй пары транзисторов 7-2. Таким образом, переключение с одной пары транзисторов на другую осуществляется синхронно с работой друхтактного инвертора, синхронизируемого генератором 31 тактовых импульсов, благодаря чему исключается дробление импульсов двухтактного инвертора 3 и протекание уравнивающего тока в обмотках одного плеча выходного трансформатора 4.

Когда начинает работать вторая пара транзисторов 7-2, напряжение на выходных клеммах становится равным n.i i ibLti

0

5

0

5

0

5

0

5

0

5

где К.-второй коэффициент трансформации трансформатора 4 при работе второй пары транзисторов 7-2; Ugj,- второе напряжение на выходе не- прерывного трансформатора напряжения.

При дальнейшем увеличении напряжения на входных выводах так, что логическая «1 появляется на п-м выходе дешифратора 16, начинает работать (7-п)-я пара транзисторов, причем переключение на (7-п)-ю пару транзисторов осуществляется также синхронно с работой двухтактного инвертора 3. При работе (7-п)-й пары транзисторов напряжение на входных клеммах становится равным

Ua K« U6Mxn,

где Ка- п-й коэффициент трансформации трансформатора 4 при работе п-й пары транзисторов 7-п; C7jgyyj7-п-е напряжение на выходе непрерывного стабилизатора 1 напряжения.

Коэффициент трансформации трансформатора 4 и вы.ходные напряжения непрерывного стабилизатора 1 напряжения выбираются так, что

К. Чы )(i. - KfjUjy. Uft.

Диоды 8 устанавливаются для защиты трансформаторов от обратного напряжения, которое появляется при работе первой пары транзисторов 7-1 на коллектора.х второй 7-2 и п-й 7-п пар транзисторов, а при работе второй пары транзисторов 7-2 на коллекторах п-й пары транзисторов 7-п.

Рассмотрим случай, когда один из транзисторов выходит из строя. При наличии логической «1, например, на втором выходе дещифратора 16, когда работает вторая пара транзисторов 7-2, один из этих транзисторов выходит из строя. Если транзистор не открывается, то магнитопровод трансформатора 4 насыщается, резко увеличивается ток через второй транзистор и перегорает предохранитель в цепи коллектора второго транзистора. Если один из транзисторов не закрывается, то магнитопровод трансформатора 4 также насыщается, резко увеличивается ток через этот транзистор и перегорает предохранитель в цепи его коллектора. Далее магнитопровод трансформатора 4 перемагничивает- ся и вновь насыщается, резко увеличивается ток через второй транзистор и перегорает предохранитель в цепи второго транзистора, т.е. в обоих случаях вторая пара транзисторов 7-2 не влияет на дальнейшую работу схемы.

При этом на второй вход мажоритарного элемента 21, второй вход второго логического элемента И 22. а также на второй вход второго логического элемента НЕ 24 подается управляющий сигнал в виде логической «1. с выхода второго логического элемента НЕ 24 на второй вход третьего логического элемента И 25 поступает логический «О, т.е. на выходе третьего логического элемента И 25 всегда присутствует логический «О. Ключ 12-2 и вторая схема 9-2 управления всегда закрыты.

Так как на входе второго мажоритарного элемента 21 присутствуют две логические «1, на его выходе также появляется логическая «1, которая поступает на третий вход первого мажоритарного элемента 17 и через первый логический элемент ИЛИ 18, первый логический элемент И 19 и D-триг- гер 30-1 на выход узла 9-1 управления.

В результате этого начинает работать первая пара транзисторов 7-1, а напряжение на выходе стабилизатора 1 напряжения равно ивых.1, т.е. устройство продолжает работать, но падение напряжения и рассеивание мощности на стабилизаторе напряжения завышены по сравнению с номинальным режимом работы.

Таким образом, использование источника позволяет уменьшить уровень пульсаций выходного напряжения и повысить надежность работы устройства в условиях воздействия дестабилизирующих факторов за счет уменьшения мощности, рассеиваемой транзисторами двухтактного инвертора 3, и за счет исключения переключения силовых транзисторов в полупериоде работы двухтактного инвертора 3.

Формула изобретения Стабилизирующий источник электропитания по авт. св. № 1149355, отличающийся тем, что, с целью уменьшения пульсаций выходного напряжения и повышения надежности работы устройства в условиях воздействия дестабилизирующих факторов, введены генератор тактовых импульсов и п D- триггеров, синхронизирующие входы которых подключены к выходу генератора тактовых импульсов, D-входы D-триггеров подключены к соответствующим выходам узла коммутации, а выходы - к соответствующим входам узлов управления.

| Стабилизирующий источник электропитания | 1983 |

|

SU1149355A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1988-11-07—Публикация

1987-04-01—Подача