Устройство относится к области :импульс юй техники и может использоваться для формирования интервалов времени в аппаратуре автоматики, телемеханики и вычислительной техники при использовании элементной базы обеспечивающей уровень логического нуля5 близкий к нулевому потенциалу, ;например, при использовании микро- I схем серии КМОП,

I Цель изобретения - повьгаение точности устройства.

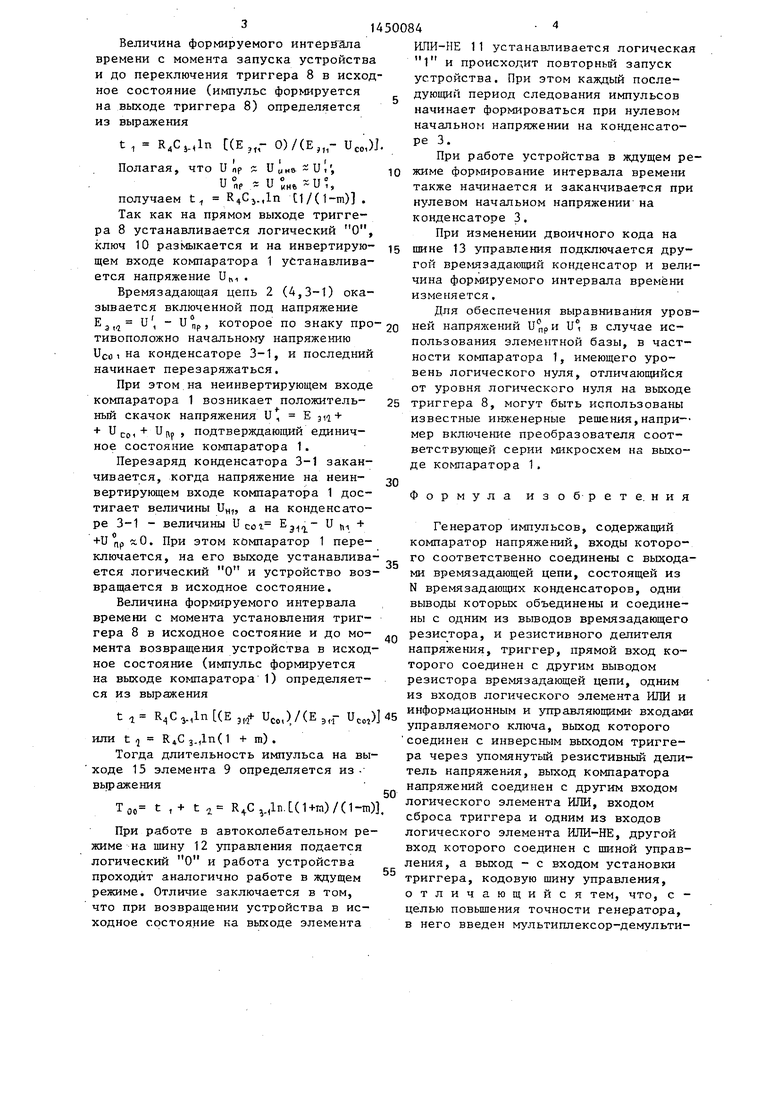

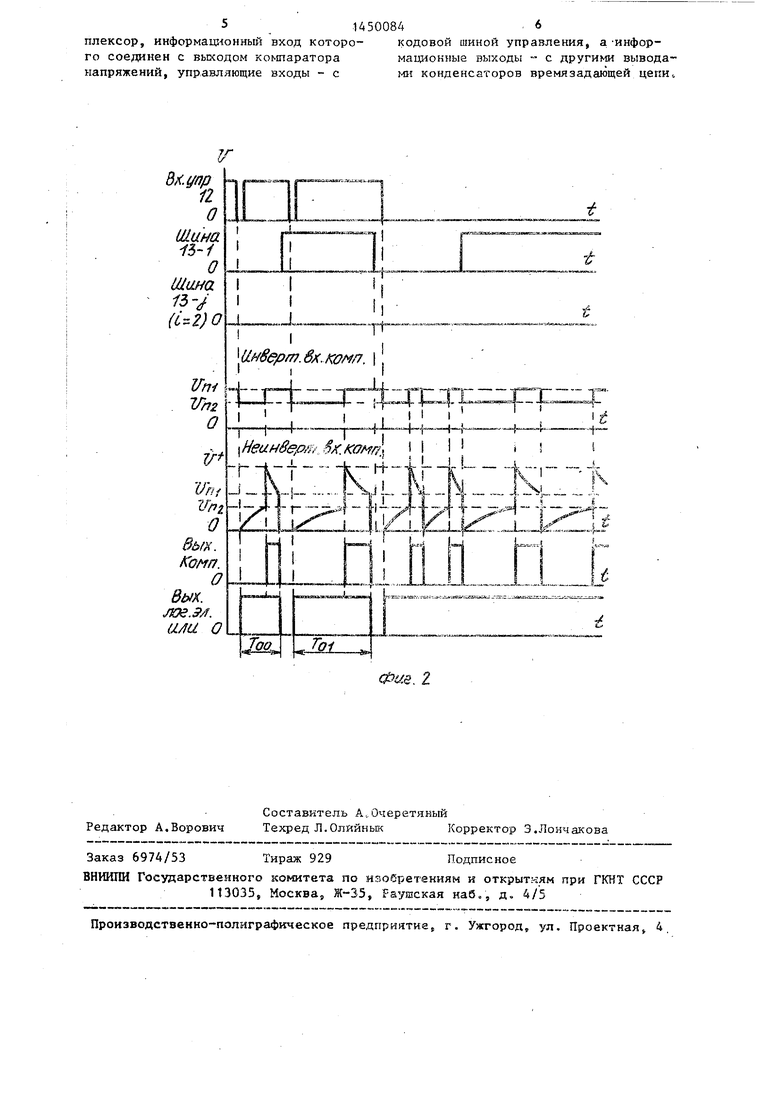

I Поставленная цель достигается за счет того, что в генератор импульсов I после поступления сигнала на кодовую I ишну управле ния выбранный ключ закк- I нут, времязадающая цепь включена j между точками с нулевыми потенциала- ми - межд.у элементами, на выходе ко- I торык установлен логический ноль, I и времязадающий конденсатор разряжен I практически до нуля. Такая ситуация может сохраняться сколь угодно долго I что не отражается на точностных ха- i рактеристиках устройства. ; На фиг, 1 представлена фукктщо- ; налъная схема генератора; на ф :г. 2 : эпюры напряжений поясняющие е:- о ра- : боту,

i Генератор импульсов содержит ком- I паратор 1 напряжений, входы которого соединены соответственно с выходами времязадающей цепи 2, состоящей из времязадающих конденсаторов 3-1+3-, одни выводы которых объединены и соединены с одним из вьшодов времяза- дающего резистора 4, и резистивного делителя напряжения 5, состоящего из резисторов 6 и 7, триггер 8, прямой выход которого соединен с другим выводом резистора 4 времязадающей цепи 2, одним из входов логического элемента ИЛИ 9 и информационным и управляющим входами управляемого ключа 10 выход которого соединен с инверсным выходом триггера 8 через упомянутый делитель 5 напряжения. Выход компара тора 1 напряжений соединен с другим входом логического элемента ИЛИ 9, входом сброса триггера 8 и одним из входов логического элемента 11 ИЛИ-Н другой вход которого соединен с шиной 12 управления, а выход - с входо установки триггера В. Кодовая шина 1 управления соединена с управляющими входами мультиплексора-демультиплек сора 14, информационный вход демуль- типлексора которого соединен с выхо

0

5

дом компаратора 1 напряжений, а информационные выходы - с други м выводами конденсаторов 3 времязадающей цепи 2. В качестве мультиплексора-де- мультип-пексора 14 может быть использована, например, микросхема 564КП1. Устройство работает следующим образом.

При работе в ждущем режиме в исходном состоянии на шине 12 управле- 1-шя установлена логическая 1, на прямом и инверсном вьпшдах триггера 8 - логические О (U р ) и 1 (ujug) соответственно, на выходах компаратора 1 и элемента ИШ1 9 логические О (U° и U°), Ключ 10 разомкнут и на инвертирующем входе компаратора 1 установлено напряжете Uf,, .

Предположим, что на шине 13 управления установлены логические О. Тогда канал Х-Х мультиплексора 14 за1угкнут и конденсатор 3-1 соединен с выходом компаратора 1.

Так как на прямом выходе триггера и выходе компаратора 1 установлены логические 0 % начельное нг.пря- жение на конденсаторе 3.-1 равно О

При поступлешш импульса (логического О) ка шину 12 управления триггер 8 устанавливается в состояниеS при котором на его прямом выходе логическая 1 (U i-,p ) & на инверсном зькоде - логический О (и °ииб) .

На управлк; нций вход ключа 10 с прямого выхода триггера 8 поступает: логическая 1, он зашатается, и на инвертирующем входе кOl iпapaтopa i устанавливается напряжение

и m(U пр - и укб) 1°ме ,

где m (R , + й.) f

сопротивления резисторов 6 и 7 делителя 5 напряжения,

Времязадающая цепь 2 (4,3 - 1) оказывается включенной под напряжение Е 3,1 и f,p - и° и конденсатор 3-1 начинает заряжаться.

Заряд конденсатора 3-1 заканчивг1- ется, когда напряжение на неинвертирующем входе компаратора 1 достигает величины и„о, а на конденсаторе 3-1- величины и с(,1 и пг U i

Компаратор 1 переключается и логическая 1 О 1 с его выхода устанавливает триггер 8 в исходное состояние.

R , R

3145

Величина формируемого интервала времени с момента запуска устройства и до переключения триггера 8 в исходное состояние (импульс формируется на выходе триггера 8) определяется из выражения

t, R,Cj.,ln C(Ej,r 0)/(Е,„- Ueo,)J.

Полагая, что U лр % , и пр и ИН6 и 1s

получаем t R4Cj.,ln 1/(1-m) . Так как на прямом выходе тригге8 устанавливается логический О,

При изменении двоичного кода на

ключ 10 размыкается и на инвертирую- ig шине 13 управления подключается друщем входе компаратора 1 устанавливается напряжение U .

Времязадающая цепь 2 (4,3-1) оказывается включенной под напряжение

Е,,. и , - и

тивоположно начальному напряжению Ucc 1 на конденсаторе 3-1, и последний начинает перезаряжаться.

При этом на неинвертирующем входе компаратора 1 возникает положительный скачок напряжения U Е 311 + + ,+ U((p , подтверждающий единичное состояние компаратора 1.

Перезаряд конденсатора 3-1 заканчивается, когда напряжение на неин- .,Q вертирующем входе компаратора 1 достигает величины UHI, а на конденсаторе 3-1 - величины Ucoi эп м + +U пр «.0. При этом компаратор 1 переключается, на его выходе устанавливается логический О и устройство возвращается в исходное состояние.

Величина формируемого интервала времени с момента установления триггера 8 в исходное состояние и до мо- .„ мента возвращения устройства в исходное состояние (импульс формируется на выходе компаратора 1) определяетгой вpe изaдaющий конденсатор и величина формируемого интервала времени изменяется.

Для обеспечения выравнивания уровлр, которое по знаку про-JQ ней напряжений и прИ U, в случае использования элементной базы, в частности компаратора 1, имеющего уровень логического нуля, отличающийся от уровня логического нуля на выходе 25 триггера 8, могут быть использованы известные инж.енерные решения, напри- мер включение преобразователя соответствующей серии микросхем на выходе компаратора 1.

Формула изобрете. кия

Генератор импульсов, содержащий компаратор напряжений, входы которого соответственно соединены с выходами времязадающей цепи, состоящей из N времязадающих конденсаторов, одни выводы которых объединены и соединены с одним из выводов времязадающего резистора, и резистивного делителя напряжения, триггер, прямой вход которого соединен с другим выводом резистора времязадающей цепи, одним из входов логического элемента ИЛИ и

35

Генератор импульсов, содержащий компаратор напряжений, входы которого соответственно соединены с выходами времязадающей цепи, состоящей из N времязадающих конденсаторов, одни выводы которых объединены и соединены с одним из выводов времязадающего резистора, и резистивного делителя напряжения, триггер, прямой вход которого соединен с другим выводом резистора времязадающей цепи, одним из входов логического элемента ИЛИ и

ся из выражения

t КцСзн1п(Е 3,xf UC.,)/(E,.- и,„,)45 информационным и управляющими- входами

управляемого ключа, выход которого

или t ,2 К4Сз.Дп(1 + т). соединен с инверсным выходом триггеТогда длительность импульса на выходе 15 элемента 9 определяется из вьфажения

50

ра через упомянутый резистивный делитель напряжения, выход компаратора напряжений соединен с другим входом логического элемента ИЛИ, входом сброса триггера и одним из входов логического элемента ИЛИ-НЕ, другой вход которого соединен с шиной управления, а выход - с входом установки триггера, кодовую шину управления, отличающийся тем, что, с - целью повышения точности генератора, в него введен мультиштексор-демультиTOO t ,+ ti R4C,.,ln.(1+ia)/(1-in)3.

При работе в автоколебательном режиме на шину 12 управления подается логический О и работа устройства проходит аналогично работе в ждущем режиме. Отличие заключается в том, что при возвращении устройства в исходное состояние на выходе элемента

ИЛИ-НЕ 11 устанавливается логическая 1 и происходит повторньй запуск

устройства. При этом каждый после- дующий период следования импульсов начинает формироваться при нулевом начальном напряжении на ковденсато- ре 3.

При работе устройства в ждущем ре- жиме фор п1рование интервала времени также начинается и заканчивается при нулевом начальном напряжении на конденсаторе 3.

При изменении двоичного кода на

шине 13 управления подключается другой вpe изaдaющий конденсатор и величина формируемого интервала времени изменяется.

Для обеспечения выравнивания уров

Формула изобрете. кия

Генератор импульсов, содержащий компаратор напряжений, входы которого соответственно соединены с выходами времязадающей цепи, состоящей из N времязадающих конденсаторов, одни выводы которых объединены и соединены с одним из выводов времязадающего резистора, и резистивного делителя напряжения, триггер, прямой вход которого соединен с другим выводом резистора времязадающей цепи, одним из входов логического элемента ИЛИ и

ра через упомянутый резистивный делитель напряжения, выход компаратора напряжений соединен с другим входом логического элемента ИЛИ, входом сброса триггера и одним из входов логического элемента ИЛИ-НЕ, другой вход которого соединен с шиной управления, а выход - с входом установки триггера, кодовую шину управления, отличающийся тем, что, с - целью повышения точности генератора, в него введен мультиштексор-демульти51450084 6

плексор, информадаонный вход которо- кодовой шиной управления, а. -инфор- го соединен с выходом компаратора мационные выходы - с другими вывода- напряжений, управляющие входы - с н конденсаторов времязадающей цепи,

| название | год | авторы | номер документа |

|---|---|---|---|

| Одновибратор | 1983 |

|

SU1138928A1 |

| Генератор импульсов | 1986 |

|

SU1411930A2 |

| Генератор импульсов | 1983 |

|

SU1140231A1 |

| Генератор импульсов | 1984 |

|

SU1173523A1 |

| Одновибратор | 1982 |

|

SU1083348A1 |

| Генератор импульсов | 1983 |

|

SU1091310A1 |

| Одновибратор | 1981 |

|

SU983988A1 |

| Генератор импульсов | 1983 |

|

SU1088101A1 |

| Ждущий генератор | 1982 |

|

SU1037418A1 |

| Импульсный генератор | 1982 |

|

SU1058033A1 |

Изобретение может быть использовано для формирования интервалов времени в аппаратуре автоматики, телемеханики, вычислительной и импульсной технике при использовании элементной базы, обеспечивающей уровень логического нуля, близкой к нулевому потенциалу, например при использовании микросхем КМОП серии. Цель изобретения - повьшение точности - достигается за счет того, что в генераторе импульсов после поступления сигнала на кодовую шину управления вы- бранньш ключ зам1снут, времязадающая цепь 2 включена между точками с нулевым потенциалом - между элементами, на выходе которых установлен логический нуль, и времязадающий резистор 4 разряжен практически до нуля. Такой режим может сохраняться сколь угодно долго, что не отражается на точности характеристик генератора. На чертеже также показаны компаратор 1 напряжений, времязадающие конденсаторы 3-1...3-N, резистивный делитель напряжения 5 на резисторах 6 и 7, триггер 8, логический элемент ИЛИ 9, управляемый ключ Ю, логический элемент ИЛИ-НЕ 11, шина 12 управления, кодовая шина 13 и демульти- плексор 14. 2 ил. г с (Л 4 СП

ии6ерт. вх.ко/,-7.

Неин8ерл/ вх.конг1,

Г

I

-1Ф1.е.г

| Одновибратор | 1981 |

|

SU983988A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Генератор импульсов | 1983 |

|

SU1140231A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-01-07—Публикация

1986-08-25—Подача