4

сд

0) со

00

Изобретение относится к цифровой вычислительной технике и может быть использовано в устройствах прерывания, мультипрограммирования и в приоритетных схемах.

Цель изобретения - повьшение быстродействия путем обслуживания запросов в режиме абсолютного приоритета.

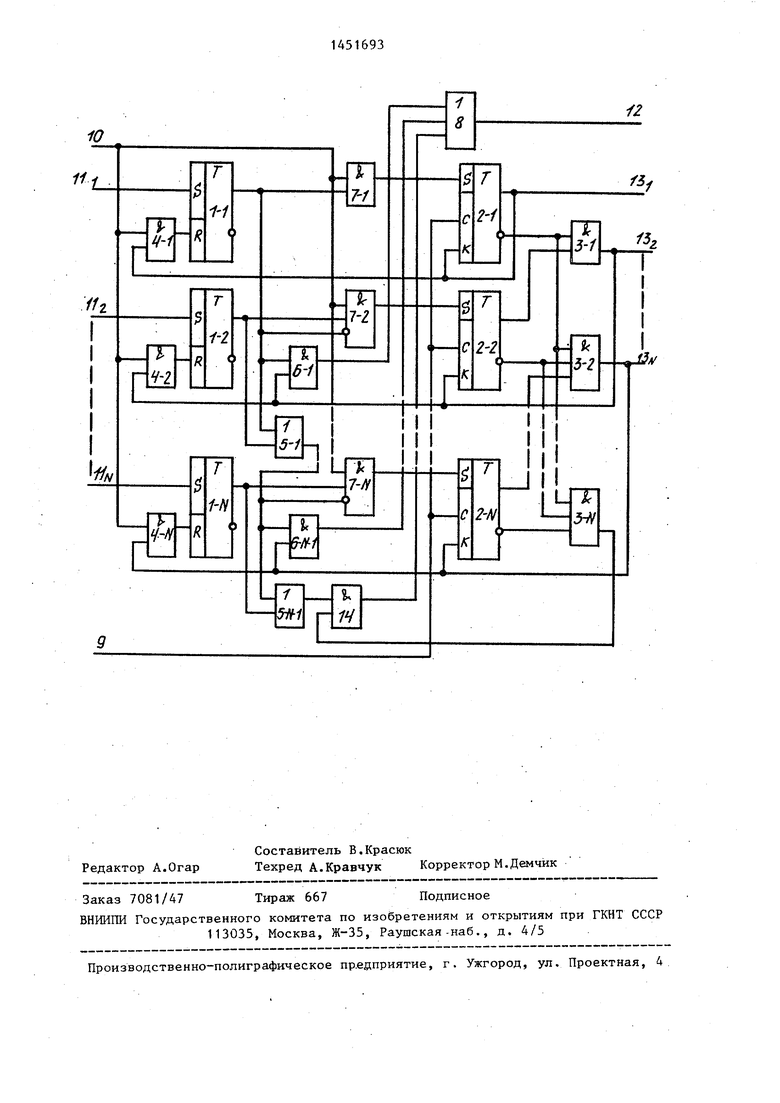

На чертеже представлена схема устройства.

Устройство содержит регистры 1 и 2, элементы И 3 и 4 групп, группу элементов ИЛИ 5, элементы И 6 и 7 групп, элемент ИЛИ 8, вход 9 записи вход 10 обнуления устройства, группу запросных входов 11, сигнальный выход 12, группу выходов 13 устройства и элемент И 14.

Устройство работает следующим образом.

В исходном состоянии при отсутствии запросов на запросных входах ,11 устройства триггеры регистров 1 и 2 находятся в нулевом состоянии. Нулевой сигнал с прямого выхода первого разряда регистра 2 подается на выход 13/ устройства, а нулевые сигналы с прямых выходов всех последующих разрядов регистра 2 через элементы И 3 поступают на входы элементов И 6, а с выходов элементов И 6 - на входы элемента ИЛИ 8, с выхода которого на сигнапьньш выход 12 устройства поступает нулевой сигнал, сигнализирующий об отсутствии запроса на запросных входах 11 устройства. С нулевых выходов всех разрядов регистра 2 на N-й элемент И 3 приходят единичные сигналы, а на

его выходе вырабатывается сигнал разрешения, поступающий на элемент И 14.

При появлении сигнала от устройства с К-м приоритетом на единичный вход 11 К-го разряда регистра 1 поступает единичньй сигнал, по которому К-й разряд регистра 1 устанавливается в .единичное состояние. Сигнал с прямого выхода К-го разряда регистра 1 проходит через цепочку элементов ИЛИ 5 и поступает на первый вход элемента И 14, на втором входе которого имеется сигнал разрешения, с выхода этого элемента на соответствующий вход элемента ИЛИ 8 поступает единичный сигнал, который по сигнальному выходу устройства

0

5

0

5

0

5

0

5

0

5

12 сообщает о наличии запроса. По этому сигналу поступает на вход 10 обнуления ответный сигнал, который, пройдя через К-й элемент И 7, поступает на единичный вход регистра 2, по которому осуществляется перезапись запроса в соответствующий разряд регистра 2. На вход (К-1)-го элемента И 3 с прямого выхода К-го разряда регистра 2 поступает единичный сигнал, на соответствующие входы всех последующих, начиная с К-го, элементов И 3 с нулевого выхода К-го разряда регистра 2 поступает нулевой сигнал, запрещающий на выходах 13 устройства с (К+1)-го по N-й появление единичного сигнала. Единичный сигнал появляется только на К-м разряде выхода 13 и на входе К-го элемента И 4, разрешая обнуление соответствующего разряда регистра 1 сигналом установки в О.

Если во время обслуживания внешнего устройства с К-м приоритетом пришел запрос с приоритетом К+1, где К+1 N, то единичный сигнал записывается в (К+1)-м разряде регистра 1. После исполнения запроса с К-м приоритетом вырабатывается единичный сигнал, поступающий на , вход 9 записи, обнуляющий К-й разряд регистра 2. Единичный сигнал на ну- левом выходе К-го разряда регистра 2 дает разрешение на (К+1-1)-й элемент И 3, цикл повторяется, и на выходе 13 устройства в (К+1)-м разряде появляется единичный сигнал.

Если во время обслуживания К-го запроса пришел запрос от устройства с приоритетом R, где R i К, то единичный сигнал записывается в R-й разряд регистра 1, с прямого выхода К-го разряда регистра 1 единичный сигнал проходит через (К-1)-й элемент ИЛИ 5 и (К-1)-й элемент И 6 на соответствующий вход элемента ИЛИ 8, с вькода которого на сигнальный выход 12 устройства поступает сигнал, сигнализирующий о наличии запроса с приоритетом R. На вход 10 обнуления поступает единичный сигнал, который записывает единичный импульс в R-й разряд регистра 2, с нулевого выхода которого нулевой сигнал запрещает выдачу единичного сигнала на выходы 13 устройства по всем разрядам с (R-(-l)-ro до N-ro до окончания обслуживания запроса с приоритетом

R, и на сигнальном выходе 12 устанавливается нулевой сигнал. Сигнал запроса с приоритетом К хранится в соответствующем разряде регистра 2.

Если в это время првдет запрос от нового внешнего устройства с приоритетом т, где m - целое положительное число и m R, то он также хранится на соответствующем триггере первого регистра 1.

После окончания работы внешнего устройства с R-M приоритетом на груп пе выходов 13 появляется сигнал, сформированный аналогичным образом в разряде, меньшем по модулю из К или т. При одновременном поступлении нескольких запросов от устройств с разными приоритетами схема формирует на группе выходов сигнал в разряде, соответствующем меньшему по модулю приоритету.

Формула изобретени

Приоритетное устройство, содержащее два М-разрядньпс регистра, первую группу из N элементов И, элемент ИЛИ, элемент И, причем единичный вход i-ro (i 1 - N) разряда первого регистра является i-м запросным входом устройства, инверсный вы ход т-го (т 1 - N - 1) разряда второго регистра соединен с т-ми входами с (га+1)-го по N-й элементов И первой группы, выход т-го элемен- та И первой группы является (т+1)-м выходом устройства, отличающееся тем, что, с целью повышения быстродействия за счет обслуживания запросов в режиме абсолютного приоритета, в него введены вторая группа из N элементов И, третья группа из N элементов И, четвертая группа из N - 1 элементов И, группа из N - 1 элементов ИЛИ, причем инверсный выход i-ro разряда второго регистра соединен с i-м входом i-ro элемента И первой группы, прямой выход j-ro разряда (j 2 - N) второго регистра соединен с j-м входом

(J - 1)-го элемента И первой группы, первые входы всех элементов И второй группы соединены с первыми вхо- g дами элементов И третьей группы и с входом обнуления устройства, выход i-ro элемента И второй группы соединен с нулевым входом i-ro разряда первого регистра, выход i-ro зле10 мента И третьей группы соединен с единичным входом i-ro разряда второго регистра, второй вход первого элемента И второй группы соединен с прямым выходом и нулевым входом пер15 вого разряда второго регистра и является первым выходом устройства, второй вход j-ro элемента И второй группы соединен с первым входом (j - 1)-го элемента И четвертой груп20 пы, с нулевым входом j-ro разряда

25

второго регистра и с выходом (j - - 1)-го элемента И первой группы, выход N-ro элемента И первой группы соединен с первым входом элемента И, прямой выход i-ro разряда первого регистра соединен с вторым входом i-ro элемента И третьей группы, причем прямой выход первого разряда первого регистра соединен с инверс- 0 ным входом второго элемента И третьей группы, с вторым входом первого элемента И четвертой группы и с пер- вьм входом первого элемента ИЛИ груп- пь1,выход К-го ( - N - 2) эле- 5 мента ИЛИ группы соединен с первым входом (К+1)-го элемента ИЛИ группы, с инверсным входом (К+2)-го элемента И третьей группы и с вторым входом (К+1)-го элемента И четвертой 0 группы, прямой выход разряда первого регистра соединен с вторым входом (j - 1)-го элемента ИЛИ группы, выход (N - 1)-го элемента ИЛИ группы соединен с вторым входом эле- 5 мента И, выход которого соединен с первым входом элемента ИЛИ, выход которого является сигнальным выходом устройства, выход т-го элемента И четвертой группы соединен с (т+1)-м 0 входом элемента ИЛИ, вход записи второго регистра соединен с входом записи устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки запросов | 1986 |

|

SU1397913A1 |

| Устройство для обслуживания запросов | 1986 |

|

SU1336000A1 |

| Устройство для обслуживания запросов | 1983 |

|

SU1124306A1 |

| Устройство для приоритетного обслуживания заявок | 1989 |

|

SU1709313A1 |

| Устройство для обслуживания запросов | 1990 |

|

SU1777140A1 |

| Устройство для обслуживания разноприоритетных групп заявок | 1990 |

|

SU1718219A2 |

| Устройство для обслуживания группы запросов | 1988 |

|

SU1562913A1 |

| Устройство приоритета | 1984 |

|

SU1249515A1 |

| Устройство циклического приоритета | 1990 |

|

SU1716516A1 |

| Асинхронное приоритетное устройство | 1986 |

|

SU1336002A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в устройствах прерывания, мультипрограммирования и в приоритетных схемах. Целью изобретения является повышение быстродействия за счет обслуживания запросов в режиме абсолютного приоритета. Приоритетное устройство содержит два регистра, группы элементов И, группу элементов ИЛИ, элементы И и ИЛИ. В устройстве применяется цепочка из элементов.И и ИЛИ, позволякщая внеочередному запросу опросить состояние выходов устройства и, если будет установлено, что приоритет нового запроса выше приоритета обслуживаемого, прервать текущее обслуживание более низкоприоритетного запроса, сохранив его в выходном регистре, и немедленно начать обслуживание нового. 1 ил.

| Асинхронное приоритетное устройство | 1983 |

|

SU1130867A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приоритетное устройство | 1984 |

|

SU1211728A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-15—Публикация

1987-06-05—Подача