4i

сд

Изобретение относится к элемента автоматики и вычислительной техники и может быть использовано з прбцизи онных радиоэлектроыньк устройствах} .преим -щественно в анапоговой и электроизмерительной технике.

Цел:ь изобретения - расширение функллиональных возможностей .операционного усилителя за счет получ ения дифференциального входа и повышения стабильности нулевого уровня.

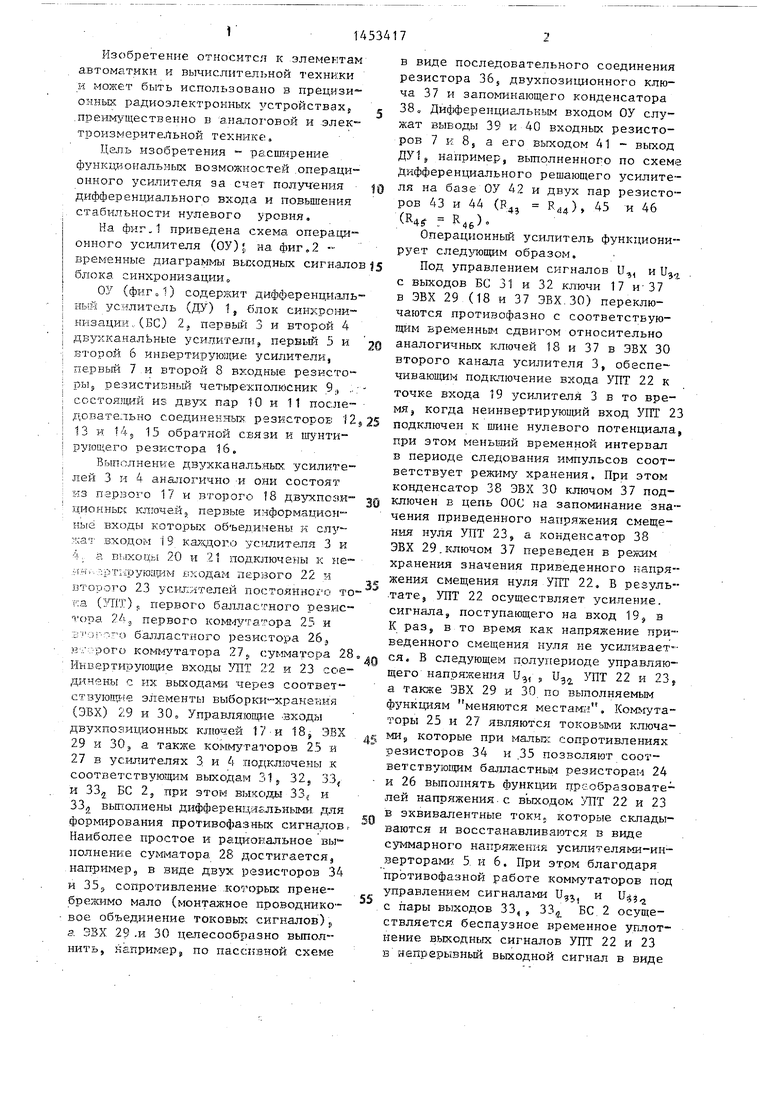

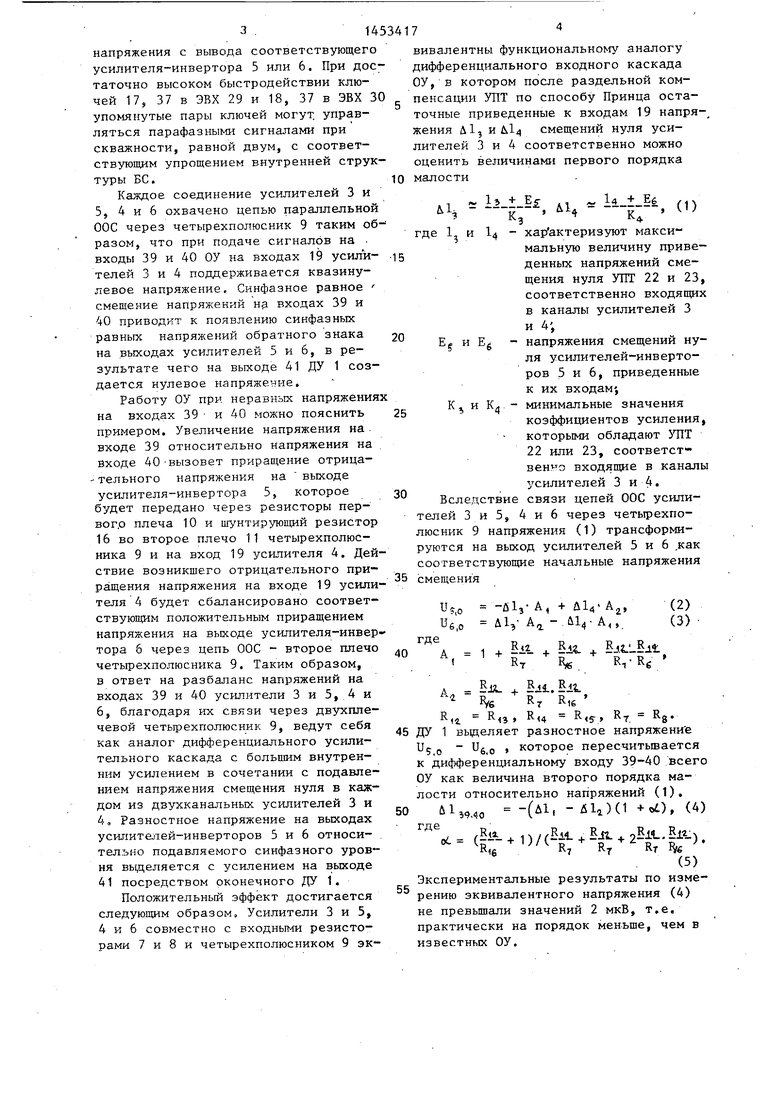

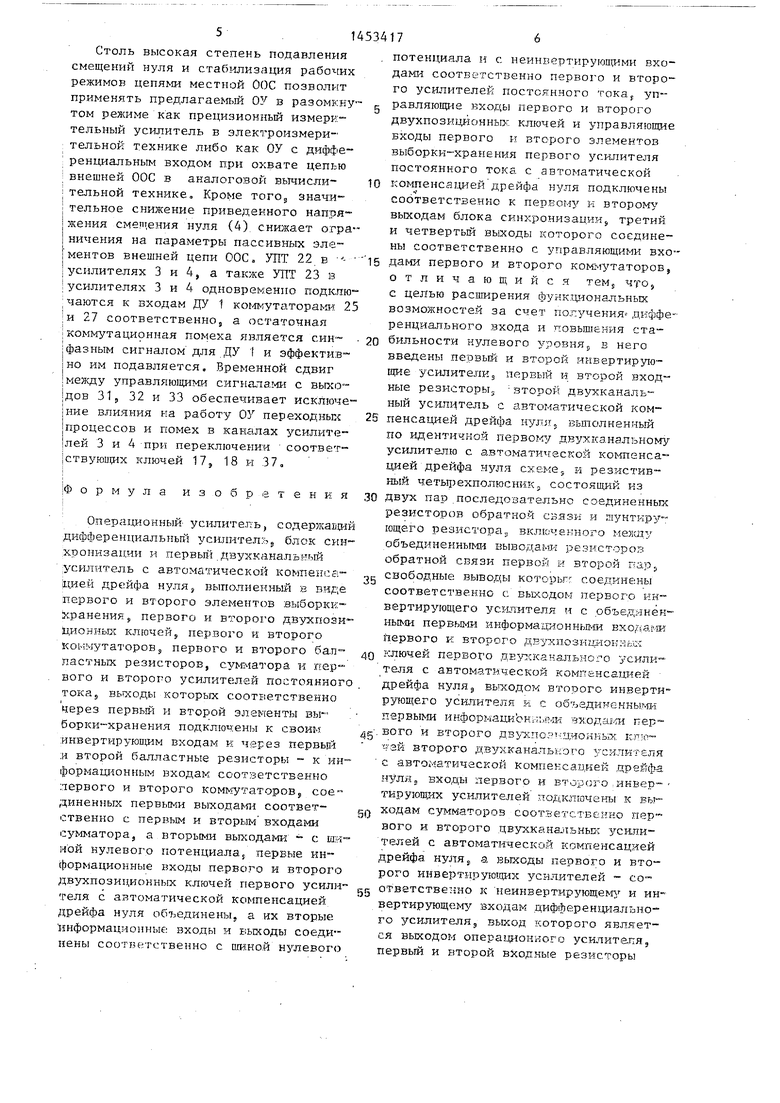

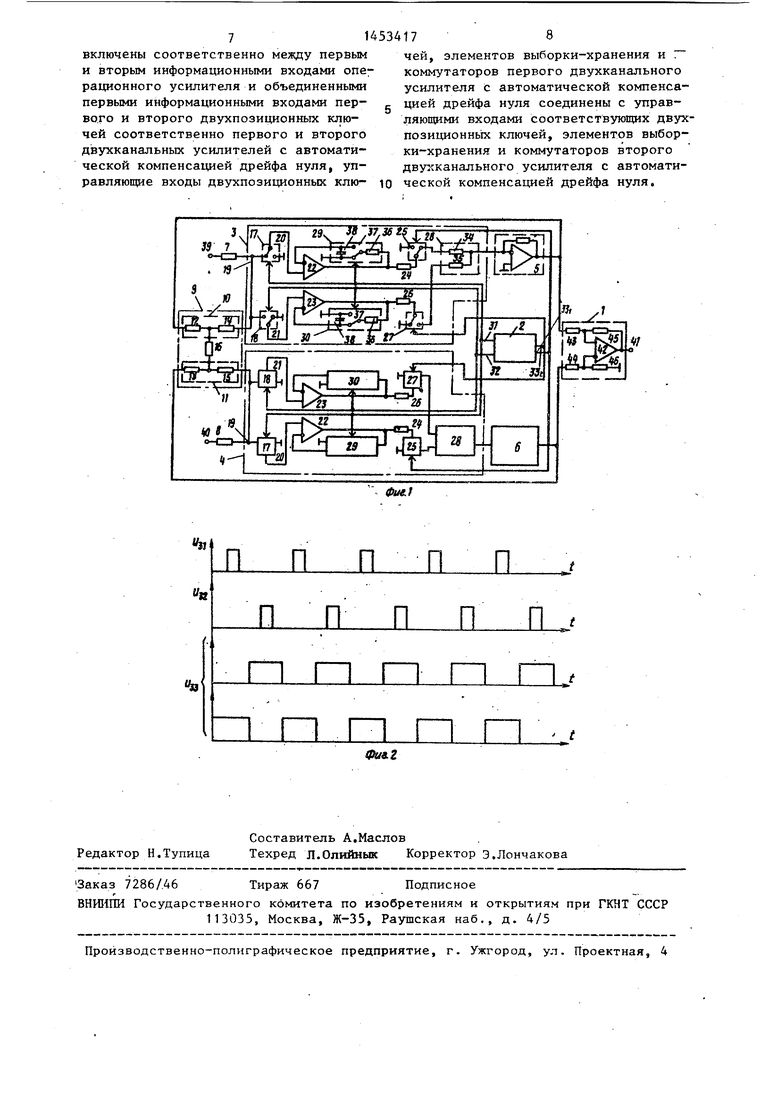

На фиг.1 приведена схема опера:ци- онного усилителя (ОУ) J, на фиг.2 - временные диаграммы выходных сигн.ало блока синхронизации

03 (фиг о 1) содержит дифференци;зль ньй усилитель (ДУ) 1, блок синхрони- низацииДБС) 2, первьш 3 и второй 4 двзосканалЬньге усилитехш, первьш 5 и второй 6 инвертирующие усилители, первьн 7 и второй 8 входные резисто- рЫу резистиЕный четырехполюсник 9, .. состоя ций из двух пар 10 и 11 последовательно соединенных резксторов 13 и t ij 15 обратной связи и шунтирующего резистора 16.

Выполнение двухканальных. усилителей 3 и 4 аналогично и они состоят из первого 17 и второго 18 двухпози- ЦИОННЬЕС ключей5 первые информационные входы которых объединены и слу- входом 19 ка;-к,цого уснлителя 3 и 4. а выходы 20 и 21 подключены к не- ия.,;-:ртирующим входам первого 22 и второго 23 yci-шителей постоянного то f;a (ЗТТГ),. первого бшшастного резистора 2Aj первого коммутатора 25 и 3Toi-nr o балластного резистора 26, :е ;::рого коммутатора 27,, сумматора 28 ИнвертируюЕще входы ЭТ1Т 22 и 23 соединены с их выходами через соответ- стзуюпцие элементы выборки-хранения (ЭВХ) 29 и 30„ Управляющие .гзходы двухпозиционных ключей 17 и 18, ЭВХ 29 и 30J а также кокгмутаторов 25 и 27 в усилителях 3 и 4 подключены к соответствующим выходам 31 32, 33, и 33 БС 2j при этом выходы 33, и 33j выполнены дифференпщгльными для формирования противофазньк сигна-лов Наиболее простое и рациональное выполнение сумматора 28 достигается, например, в виде двух резисторов 34

и 35 сопротивление .которых пренебрежимо мало (монтажное проводниковое объединение токовых сигналов),, S. ЗВХ 29 .и 30 целесообразно вьшол- нить, например, по пассивной схеме

-

25

в виде последовательного соединения резистора 36 двухпозиционного ключа 37 и запоминающего конденсатора 5 38, Ди4и|)еренциальным входом ОУ служат выводы 39 и 40 входных резисто- 7 к 8s а его выходом 41 - вьгход ДУ1 например, вьтолненного по схеме Дифференциального решающего усилите- 10 ля на базе ОУ 42 и двух пар резисторов 43 и 44 ( R), 45 и 46 .(4 R46)«

Операционный усилитель функционирует след тощим образом. 15 Под управлением сигналов U, и U,-, с выходов БС 31 и 32 ключи 17 и-37 в ЭВХ 29 (18 и 37 ЭБХ.ЗО) переключаются противофазно с соответствующим Бременньм сдвигом относительно 20 аналогичных ключей 18 и 37 в ЭВХ 30 второго канала усштителя 3, обеспечивающим подключение входа УПТ 22 к точке входа 19 усилителя 3 в то вре- мя, когда неинвертирующий вход УШ 23 подключен к шине нулевого потенциала, при этом меньший временной интервал в периоде следования импульсов соответствует режиму хранения. При этом конденсатор 38 ЭВХ 30 ключом 37 подключен в цепь ООС на запоминание значения приведенного напряжения смещения нуля УПТ 23, а конденсатор 38 ЭВХ 29.ключом 37 переведен в режим хранения значения приведенного напряжения смещения нуля УПТ 22, В резуль- тате, УПТ 22 осуществляет усиление, сигнала, поступающего на вход 19, в К раз, в то время как напряжение приведенного смещения нуля не усиливается. В следующем п.олупериоде управляющего напряжения и,, , Ug. УПТ 22 и 23, а также ЭВХ 29 и 30. по выполняемым функциям меняются местами. Коммутаторы 25 и 27 являются токовыми ключа- 45 которые при малых, сопротивлениях резисторов 34 и .35 позволяют соот- ветствуюгдим балластным резисторам 24 и 26 выполнять функции цреобразовате- лей напряжения, с в ыходом ТТТ 22 и 23 50 эквивалентные токи, которые складываются и восстанавливаются в виде cyiviMapHoro напряжения усилителями-инверторами 5. и 6. При этом благодаря противофазной работе коммутаторов под g управлением сигналами U,j, и U, с пары выходов 33, , 33 БС 2 осуществляется беспаузное временное уплот- некие выходных сигналов УПТ 22 и 23 в непрерывный выходной сигнал в виде

3 .14

напряжения с вывода соответствующего усилителя-инвертора 5 или 6. При достаточно высоком быстродействии ключей 17, 37 в ЭВХ 29 и 18, 37 в ЭВХ 30 упомянутые пары ключей могут, управляться парафазными сигналами при скважности, равной двум, с соответствующим упрощением внутренней структуры БС. Каждое соединение усилителей 3 и

5,4 и 6 охвачено цепью параллельной ООС через четырехполюсник 9 таким образом, что при подаче сигналов на . входы 39 и 40 ОУ на входах 19 усили- телей 3 и 4 поддерживается квазинулевое напряжение. Синфазное равное смещение напряжений нэ входах 39 и

40приводит к появлению синфазных равных напряжений обратного знака на вь ходах усилителей 5 и 6, в результате чего на выходе 41 ДУ 1 создается нулевое напряжение.

Работу ОУ при неравных напряжения на входах 39 и 40 можно пояснить примером. Увеличение напряжения на - входе 39 относительно напряжения на входе 40-вызовет прирап1ение отрица- - тельного напряжения на выходе усилителя-инвертора 5, которое будет передано через резисторы пер- вог.о плеча 10 и шунтирующий резистор 16 во второе плечо 11 четырехполюсника 9 и на вход 19 усилителя 4. Действие возникщего отрицательного приращения напряжения на входе 19 усилителя 4 будет сбалансировано соответствующим положительным приращением напряжения на выходе усилителя-инвертора 6 через цепь ООС - второе плечо четырехполюсника 9. Таким образом, в ответ на разбаланс напряжений на входах 39 и 40 усилители 3 и 5, 4 и

6,благодаря их связи через двухпле- чевой четырехполюсник 9, ведут себя как аналог дифференциального усилительного каскада с большим внутренним усилением в сочетании с подавлением напряжения смещения нуля в каждом из двухканальных усилителей 3 и

4, Разностное напряжение на выходах усилителей-инверторов 5 и 6 относи- тельно подавляемого синфазного уровня вьщеляется с усилением на выходе

41посредством оконечного ДУ 1. Положительный эффект достигается

следующим образом. Усилители 3 и 5, 4 и 6 совместно с входными резисторами 7 и 8 и четырехполюсником 9 эк

5 О Q

5

вивалентны функциональному аналогу дифференциального входного каскада ОУ, в котором после раздельной компенсации 5TIT по способу Принца остаточные приведенные к входам 19 напря-, жения Д1, и 1 смещений нуля усилителей 3 и 4 соответственно можно оценить величинами первого порядка малости

li + Е . «14 /ч ч

Чк7 к

где 1, и 1 - хар актеризуют максимальную величину приведенных напряжений смещения нуля УПТ 22 и 23, соответственно входящих в каналы усилителей 3 и 4;

EJ и Eg - напряжения смещений нуля усилителей-инверторов 5 и 6, приведенные к их входам , К, и К - минимальные значения

коэффициентов усиления, которыми обладают УПТ 22 или 23, соответственно входящие в каналы усилителей 3 и 4. Вследствие связи цепей ООС усилителей 3 и 5, 4 и 6 через четырехполюсник 9 напряжения (1) трансформируются на выход усилителей 5 и 6 .как соответствующие начальные напряжения смещения

U5,o -й1з- А, + Ul4 А, (2) Ufi.o ЛЦ- А, - Ul4- А,, (3)

1 + §12 L LLRat, . - R,-Rg

А RjX. + bt.Rlt % К, R R

R

r 16

R,

R, Re

11 - «S T s ДУ 1 выделяет разностное напряжений Uj p - , которое пересчитьшается к дифференциальному входу 39-40 всего ОУ как величина второго порядка малости относительно напряжений (1).

где

й1„,д -(Д1, - Л1а)(1 ), (4)

(i:; / -i -e -aVt - 5)

Экспериментальные результаты по измерению эквивалентного напряжения (4) не превьш1али значений 2 мкВ, т.е. практически на порядок меньше, чем в известных ОУ.

5

Столь высокая степень подавления смещений нуля и стабилизация рабочи режимов цепями местной ООС позволит применять предлагаема ОУ в разомкнтом режиме как прецизионный измери- тельный усилитель в элекгроизмери- тельной технике либо как ОУ с дифференциальным входом при охвате цепью внешней ООС в аналоговой вычисли- тельной технике. Кроме тогОд значительное снижение приведенного напряжения смещения нуля (4), снижает ограничения на параметры пассивных элементов внешней цепи ООС, УНТ 22 в - усилителях 3 и 4, а также УПТ 23 в усилителях 3 и 4 одновременно подключаются к входам ДУ 1 ко1-1кутаторами 2 и 27 соответственно, а остаточная коммутацирнная помеха является син- фазным сигналом для.ДУ t и эффективно им подавляется. Временной сдвиг между управляю цими сигнала с вько- дов 315 32 и 33 обеспечивает исключение влияния ка работу ОУ переходньк процессов и помех в каналах усилителей 3 и 4 при переключении соответ- ствуюи1 1х ключей 17 18 и 37,

ормула изобретения

Операционный усилитель, содержавш дифференциальный . блок синхронизации и первьй д-вухканальньш усилитель с автоматической KOMTieHcsi- Иией дрейфа нуля, выполненный в виде первого и второго элементов выборкк- гсранениЯ;, первого и второго двухпози Ционньк ключейS первого и второго коммутаторовJ первого и второго балластных резисторов, сум-матора к вого и второго усилителей постоянног тока5 выходы которых соответственно через первый и второй эле генты выборки-хранения подключены к своим инвертируюпдам входам и через первьй к второй балластные резисторы - к ин™ формащ-юнным входам соответственно лервого и второго коммутаторов, сое- диненных первьгми выходаьш соответственно с первым и вторым входами i:y№iaTopa, а вторыми выходами - с ши- нулевого потенциала/ первые кн- (()ормационные входы первого и второго двухпозиционньпх ключей первого усилителя с автоматической компенсацией дрейфа нуля объединены, а их вторые информационные входы и выходы соединены соответственно с шиной нулевого

5 0 5

5

о

потенциала и с неинвертирующими входами соответственно первого и второго усилителей постоянного тока, управляющие входы первого и второго двyxпoзигJr ioнньк ключей и управляющие входы первого и второго элементов выборки-хранения первого усилителя постоянного тока с автоматической компенсацией дрейфа нгшя подключены соответственно к первому и второму выходам блока синхронизации третий и четвертьш выходы которого соединены соответственно с управляющими входами первого и второго коммутаторов, отличающийся тем что5 с целью расширения функ.циональных возможностей за счет получения- дифференциального входа и повышения стабильности нулевого уровня,; в него введены первый и второй инвертирующие усилители3 первый и второй входные резисторы второй двухканаль- ный усапцтель с автоматической компенсацией дрейфа нуля вьшолненньгй по идентичной первому двухканальному усилителю с автоматической ког тенса- дией дрейфа нз ля схеме; и резистив- четьфехполюсниКд состоящий из двух пар .последовательно соединенных резисторов обратной связи и шунткру- ющего резистора,, вкл &чекиого мезкду объединенными выводаЕФг резисторов обратной связи первой и второй пао свободные выводы которьгг соединены соответственно с выходом первого инвертирующего усг-шителя и с .объединенными первыми информационньп4И входа ж первого к второго дву позкгшокиьс: 1шючей первого ДЕу::а ака.льного усилителя с автоматической компенсацией дрейфа нуля, выходок второго инвертирующего усилителя и с объедикенныж парными информациЬнн1,,4к зходагш пер- . вого и второго двухпо; т.гуяонкьж клю второго двухканалького усилителя с автоматической Компенсацией дрейф а нуля5 входы первого и второго л-швер- тирующих усилителей гтодклЕочены к выходам сумматороэ соотгйетственно первого и второго двухканальньп: усилителей с автоматической компенсацией дрейфа нуля, а выходы первого и второго инвертирующих усилителей - со- ответствезгно к неинвертирующенз - и ин- вертирующемз входам дифференциального усн-литешяд выход которого является выходом опаращюнкого усилитапя, первый и второй входные резисторы

714534178

включены соответственно между первым чей, элементов выборки-хранения и Г и вторым информационными входами one- коммутаторов первого двухканального рационного усилителя и объединенными первыми информационными входами пер- во.го и второго двухпозиционных ключей соответственно первого и второго двухканальных усилителей с автоматической компенсацией дрейфа нуля, упусилителя с автоматической компенсацией дрейфа нуля соединены с управляющими входами соответствующих двух позиционньЬс ключей, элементов выборки-хранения и коммутаторов второго двухканального усилителя с автоматичей, элементов выборки-хранения и Г коммутаторов первого двухканального

усилителя с автоматической компенсацией дрейфа нуля соединены с управляющими входами соответствующих двух- позиционньЬс ключей, элементов выборки-хранения и коммутаторов второго двухканального усилителя с автомати

| название | год | авторы | номер документа |

|---|---|---|---|

| Сейсмометрическое устройство | 1984 |

|

SU1278740A1 |

| Устройство выборки-хранения | 1989 |

|

SU1686481A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1065889A1 |

| ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 1987 |

|

RU1709841C |

| Устройство для интегрирования постоянного тока | 1978 |

|

SU1091183A1 |

| Усилитель постоянного тока | 1981 |

|

SU970636A1 |

| Устройство для контроля параметров элементов сложных электрических цепей | 1984 |

|

SU1290198A1 |

| Операционный усилитель | 1976 |

|

SU614442A1 |

| Усилитель постоянного тока | 1990 |

|

SU1713086A1 |

| ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ МНОГОЭЛЕМЕНТНЫХ ПАССИВНЫХ ДВУХПОЛЮСНИКОВ | 2010 |

|

RU2466412C2 |

Изобретение относится к элементам автоматики и вычислительной техники, в частности, может быть использовано в прецизионных радиоэлектронных устройствах, преимущественно в аналоговой и электроизмерительной технике. Цель изобретения - расширение функциональных возможностей операционного усилителя за счет получения дифференциального входа и повышения стабильности нулевого уровня. Для этого в операционный усилитель, сб-- держащий дифференциальный усилитель (ДУ), блок синхронизации (БС) и первый двухканальньш усилитель с автоматической компенсацией смещения нуля, состоящий из первого и второго двух- диапазонкых ключей, первого и второго усилителей постоянного тока (УПТ), двух балластных резисторов, двух коммутаторов, сумматора и двух элементов выборки-хранения (ЭВХ), причем управляющие входы ключей, ЭВХ и коммутаторов подключены к соответствующим выходам БС, введен второй двухка- нальньм усилитель, вьтолненный и подключенный аналогично первому, два усилителя-инвертора, два входньк резистора и двуплечий резистивный четырехполюсник. 2 ил. (Л

равляющие входы двухпозиционных клю- ю ческой компенсацией дрейфа нуля.

п п

п п п

«fe

п г

п п

I

| Операционный усилитель с периодической коррекцией нуля | 1983 |

|

SU1141425A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Полонников Д.Е | |||

| и др | |||

| Пути улучшения быстродействия и стабильности нуля операционных усилителей.- Измерения, контроль, автоматизация | |||

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1989-01-23—Публикация

1987-01-12—Подача