Изобретение относится к устройствам для выполнения математических операций и может быть использовано для умножения в логических узЛах информационных систем с импульсными входами и выходами.

Целью изобретения является сокращение аппаратурных затрат.

Устройство умножения троичного ко- 1 да на два вьтолнено. на шести троичных элементах, каждый из которых выполняет троичные операции, описываемые табл.

Суммирующие, входы эквивалентны вы- читакяцим входам за исключением зна- .ка выходного импульса, который является противоположным, а первый и второй суммирующие (вычитающие) ды эквиваленты между собой.

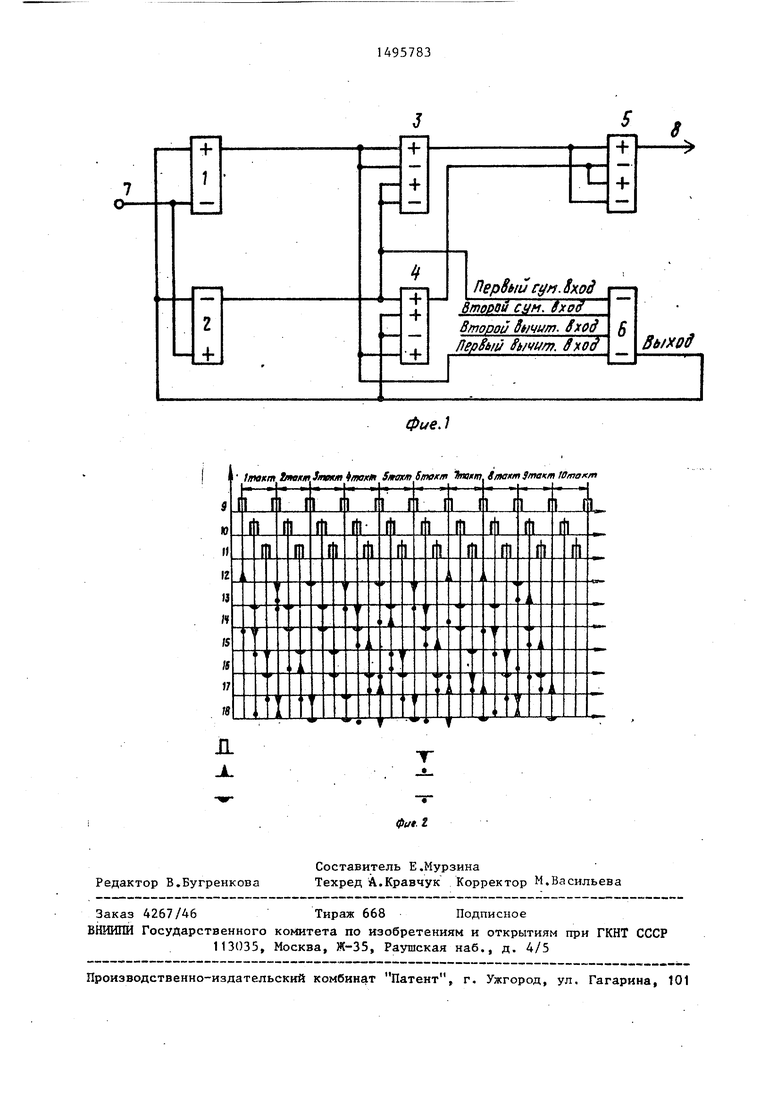

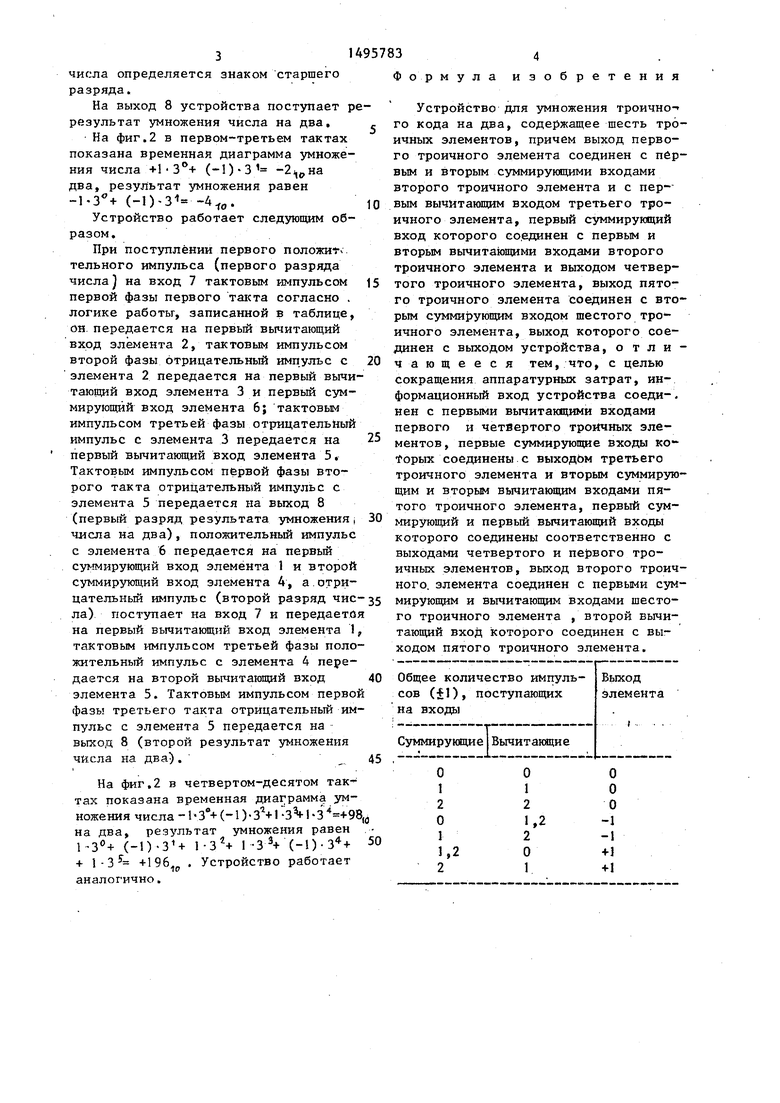

На фиг. 1 представлена схема устройства для умножения троичного кода на два; на фиг.2 - временные диаграммы его работы с условными обозначе- ниями.

Устройство для умножения троичного кода содержит шесть троичных элементов 1-6, вход 7 и выход 8 устройства.

Система тактового питания устройства - трехфазная. Тактовым импульсом первой фазы поступают положительные импульсы на вход 7 устройства, а также считывается информация с элементов 5 и 6. Тактовыми импульсами второй и третьей фаз считывается информация с элементов 1,2 и 3,4.

На фиг.2 обозначено: временные диаграммы 9-11 соответственно первой- третьей фаз тактового питания, вре .менная диаграмма 12 импульсов на входе 7 устройства; временные диаграммы 13-18 импульсов записи и считьюа- ния соответственно с элементов 1-6.

На вход 7 устройства поступает младшими разрядами вперед код в троичной системе счисления с цифрами +,0,-1 (импульсы положительной и отрицательной полярностей), где знак

(Л

с

QD &1

00 OCI

числа определяется знаком старшего разряда.

На выход 8 устройства поступает ре- результат умножения числа на два.

На фиг.2 в первом-третьем тактах показана временная диаграмма умножения числа 1 (-1)-3 -2j,pHa два, результат умножения равен -1-3% (-1)-3 .10

Устройство работает следующим образом.

При поступлении первого положит: тельного импульса (первого разряда числа на вход 7 тактовым импульсом t5 первой фазы первого тшста согласно . логике работы, записанной в таблице, он. передается на первый вычитающий вход элемента 2, тактовым импульсом второй фазы отрицательный импульс с 20 элемента 2 передается на первый вычитающий вход элемента 3 и первый суммирующий вход элемента 6; тактовым импульсом третьей фазы отрицательный импульс с элемента 3 передается на 25 первый вычитающий вход элемента 5, Тактовым импульсом первой фазы второго такта отрицательный импульс с элемента 5 передается на выход 8 (первый разряд результата умножения 30 числа на два), положительный импульс с элемента 6 передается на первый суммирующий вход элемента 1 и второй суммирующий вход элемента 4, а.отриФормула

изобретения

Устройство для умножения троично- го кода на два, содержащее шесть троичных элементов, причем выход первого троичного элемента соединен с первым и вторым суммируищими входами второго троичного элемента и с пер- вым вычитающим входом третьего троичного элемента, первый суммирующий вход которого со.единен с первым и вторым вычитающими входами второго троичного элемента и выходом четвертого троичного элемента, выход пятого троичного элемента соединен с вторым суммирующим входом шестого троичного элемента, выход которого соединен с выходом устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, информационный вход устройства соеди-. нен с первыми вычитающими входами первого и четвертого троичных элементов , первые суммирующие входы ко topbix соединены с выходЬм третьего троичного элемента и вторым суммирующим и вторым вьиитающим входами пятого троичного элемента, первый суммирующий и первый вычитающий входы которого соединены соответственно с выходами четвертого и первого троичных элементов, выход второго троичного, элемента соединен с первыми сумго троичного элемента , второй вычитающий вход которого соединен с выходом пятого троичного элемента.

цательный импульс (второй разряд чис-35 мирующим и вычитающим входами шесто- ла) поступает на вход 7 и передаетоя на первый вычитакяций вход элемента 1, тактовым импульсом третьей фазы положительный импульс с элемента 4 передается на второй вычитающий вход 40 элемента 5. Тактовым импульсом первой фазы третьего такта отрицательный импульс с элемента 5 передается на вьпсод 8 (второй результат умножения Числа на два). 45

На фиг.2 в четвертом-десятом тактах показана временная диаграмма умножения числа -1-3 +(-1)

на два, результат умножения равен (-1)-3U 1 (-1)-3 + + 1-3 +196. . Устройство работает

50

10

1495783

Формула

изобретения

Устройство для умножения троично- го кода на два, содержащее шесть троичных элементов, причем выход первого троичного элемента соединен с первым и вторым суммируищими входами второго троичного элемента и с пер- вым вычитающим входом третьего троичного элемента, первый суммирующий вход которого со.единен с первым и вторым вычитающими входами второго троичного элемента и выходом четвертого троичного элемента, выход пятого троичного элемента соединен с вторым суммирующим входом шестого троичного элемента, выход которого соединен с выходом устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, информационный вход устройства соеди-. нен с первыми вычитающими входами первого и четвертого троичных элементов , первые суммирующие входы ко topbix соединены с выходЬм третьего троичного элемента и вторым суммирующим и вторым вьиитающим входами пятого троичного элемента, первый суммирующий и первый вычитающий входы которого соединены соответственно с выходами четвертого и первого троичных элементов, выход второго троичного, элемента соединен с первыми суммирующим и вычитающим входами шесто-

го троичного элемента , второй вычитающий вход которого соединен с выходом пятого троичного элемента.

мирующим и вычитающим входами шесто-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения троичного кода на два | 1988 |

|

SU1689944A1 |

| Устройство для умножения троичного кода на два | 1987 |

|

SU1587495A1 |

| Реверсивный счетчик импульсов | 1985 |

|

SU1324109A1 |

| Реверсивный счетчик импульсов | 1985 |

|

SU1266000A1 |

| Дешифратор | 1986 |

|

SU1361724A1 |

| Дешифратор | 1986 |

|

SU1345352A1 |

| Дешифратор троичного кода 1,0,1 | 1983 |

|

SU1106015A1 |

| Дешифратор | 1983 |

|

SU1119167A1 |

| Преобразователь троичного кода 1,0,1 в двоичный код | 1982 |

|

SU1078423A1 |

| Реверсивный счетчик импульсов | 1986 |

|

SU1383496A1 |

Изобретение относится к устройствам для выполнения математических операций и может быть использовано для умножения в логических узлах информационных систем с импульсными входами и выходами. Цель изобретения - сокращение аппаратурных затрат. Новым в устройстве для умножения троичного кода на два является уменьшение количества троичных элементов, на которых построено устройство (шесть элементов вместо восьми). 2 ил. 1 табл.

аналогично.

фие.1

| Реверсивный счетчик импульсов | 1985 |

|

SU1266000A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Троичный сумматор | 1983 |

|

SU1137461A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-23—Публикация

1987-08-11—Подача