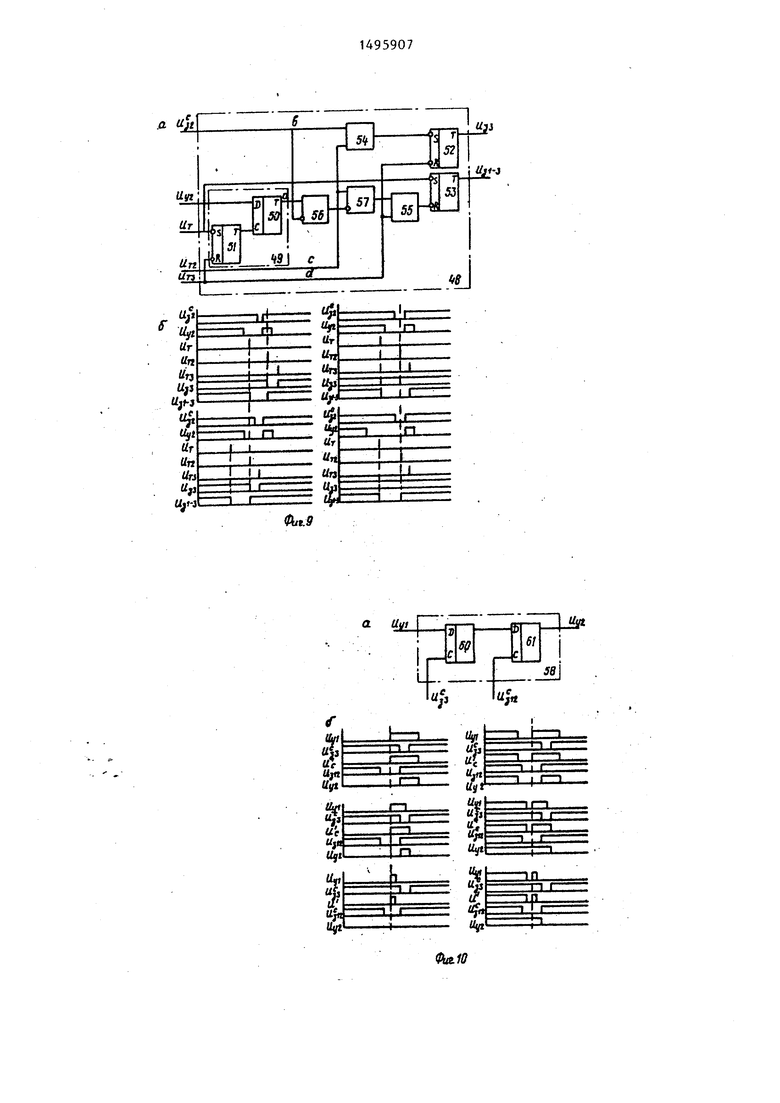

теля управляемых временных интервалов запрета (а) и временные диаграммы, поясняющие его работу (б); на фиг. 10 - схема первого ограничителя временных интервалов (а) и временные диаграммы, поясняющие его работу (б); на фиг, 11 - схема второго ограничителя временных интервалов

диненных коммутирующего дросселя 14 и коммутирующего конденсатора 15. Выводы цепочки подключены к точкам соединения анодных групп распределительных тиристоров с катодами коммутирующих тиристоров 12 и 13, аноды которых соединены с общей точкой трехфазного шунтирующего ключа 5.

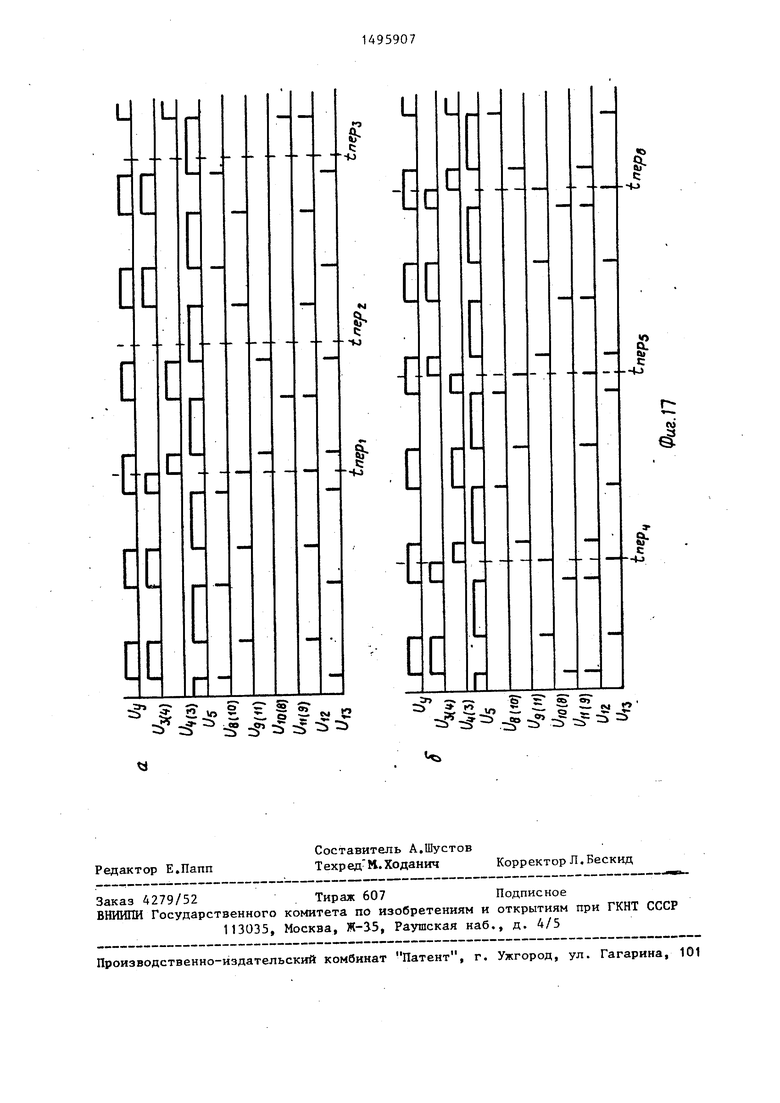

(а) и временные диаграммы, поясняющие-ю Преобразователь включает также уст- его работу (б); на фиг. 12 - 16 а, ройство 16 управления тиристорами, б, в - временные диаграммы, поясняющие работу преобразователя; на фиг. 17 - временные диаграммы, поясимеющие вход аналогового управляющего сигнала UE,XV входы сигналов режима и дх Л8 число которых соответст

диненных коммутирующего дросселя 14 и коммутирующего конденсатора 15. Выводы цепочки подключены к точкам соединения анодных групп распределительных тиристоров с катодами коммутирующих тиристоров 12 и 13, аноды которых соединены с общей точкой трехфазного шунтирующего ключа 5.

Преобразователь включает также уст- ройство 16 управления тиристорами,

имеющие вход аналогового управляющего сигнала UE,XV входы сигналов режима и дх Л8 число которых соответст

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь однофазного переменного напряжения в переменное | 1981 |

|

SU1001372A1 |

| Преобразователь п-фазного переменного напряжения в переменное | 1980 |

|

SU919029A1 |

| Тяговый преобразователь постоянного напряжения в трехфазное переменное | 1987 |

|

SU1554095A1 |

| Тяговый преобразователь постоянного напряжения в трехфазное переменное | 1989 |

|

SU1690137A1 |

| Устройство для управления регулируемым преобразователем переменного напряжения в переменное | 1990 |

|

SU1739452A1 |

| Регулятор трехфазного переменного напряжения | 1980 |

|

SU917187A2 |

| Преобразователь постоянного напряжения в многофазное переменное | 1977 |

|

SU780125A1 |

| Преобразователь переменного напряжения в постоянное | 1988 |

|

SU1577020A1 |

| Тиристорный преобразователь @ -фазного переменного напряжения в @ -фазное переменное | 1980 |

|

SU955439A1 |

| Однофазный регулятор переменного напряжения | 1981 |

|

SU1064395A1 |

Изобретение относится к электротехнике и может быть использовано в системах бесперебойного электропитания при решении задач быстродействующего бесконтактного перевода электропитания с одной сети на другую, стабилизации, регулирования, симметрирования и коммутации трехфазных переменных токов и напряжений. Целью изобретения является повышение быстродействия и надежности работы преобразователя, что достигается выполнением трехфазного шунтирующего ключа в виде трех вентильных ключей, которые состоят из встречно-параллельно включенных тиристора и диода, один из выводов каждого из которых объединен в общую точку, соединенную с анодами тиристоров, а устройство управления тиристоров снабжено совместителем импульсных сигналов. Переключение силовых ключей производится без промежуточных коммутаций шунтирующего ключа, сокращается время перевода питания с одной электросети на другую и уменьшаются потери энегии, которые связаны с этими коммутациями. 17 ил.

няющие работу формирователя распреде-15 вует числу входных команд режима рабоТЫ и дкл А и оТК л и ВКЛ в ОТКА Б

лительных сигналов.

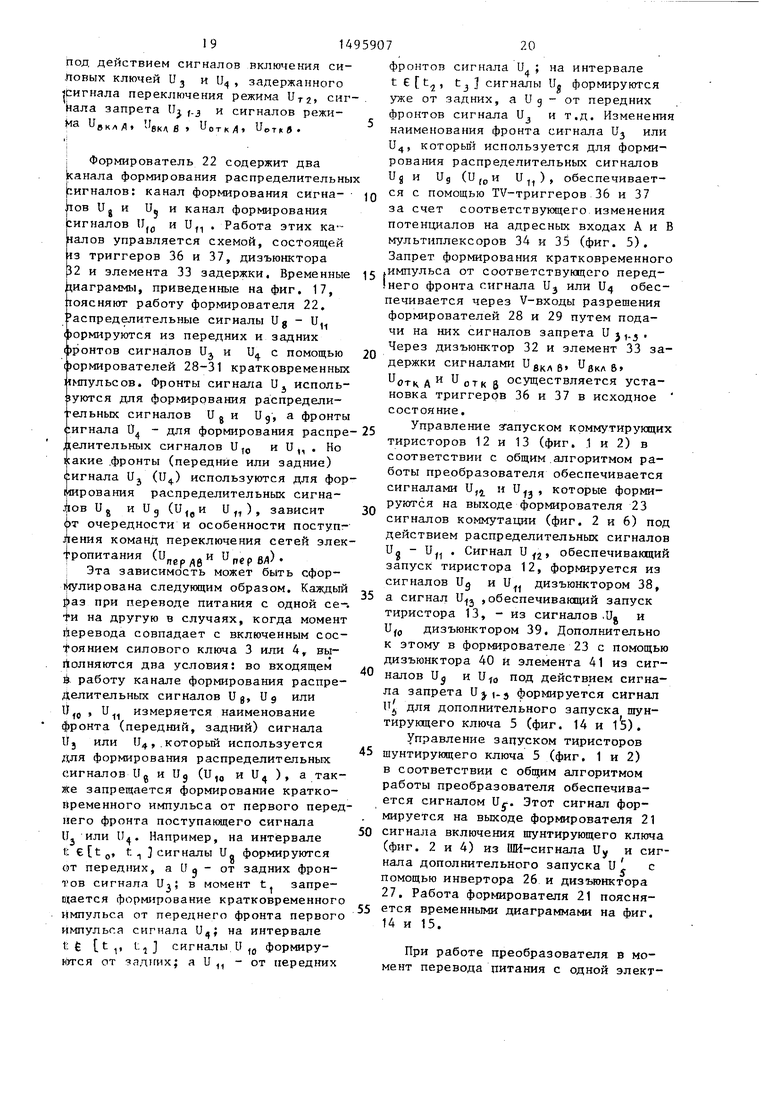

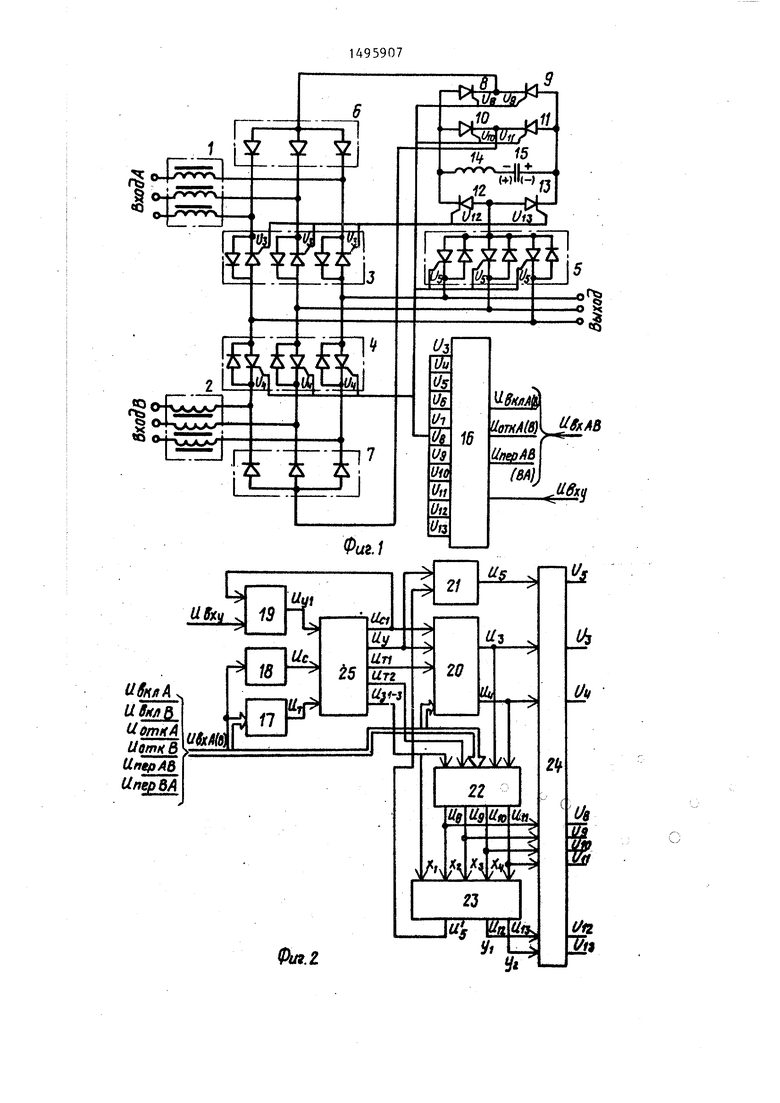

Преобразователь трехфазного переменного напряжения в переменное для систем бесперебойного электропитания (фиг. 1) содержит демпфирующие дроссели 1 и 2, включенные со стороны входных выводов, силовые ключи 3 и 4, составленные из трех пар встречно параллельно соединенных силовых диода и тиристора, каждый из которых включен последовательно между одной из групп входных выводов и выходными выводами преобразователя. Трехфазный шунтирующий диодно-тиристорный ключ 5 выполнен в виде трех ключей из встречно-параллельно включенных диода и тиристора, один из выводов каждого из которых, связанный с катодом |диода., объединен в общую точку, а дргой вывод, связанньн с анодом диода, объединен в общую точку, а другой вывод, связанный с анодом диода, подключен к соответствующему выходному выводу преобразователя. Распределительные вентильные блоки 6 и 7 состоят из трех распределительных диодов, аноды которых соединены между собой, а катод каждого из которых соединен с катодом тиристора силового ключа, связанного с входным выводом одной из фаз соответствующей сети электропитания. Распределительные тиристоры 8-11 соединены в Две параллельно включенные полумостовые цепи. Точка соединения катодов тиристоров 8 и 9, а также точка соединения катодов тиристоров 10 и 11 подключены к анодным группам распределительных вентильных блоков 6 и 7, а также и точка соединения анодов тиристоров 9 и 11 подключены к катодам соответствую1дих коммутирующих тирис- {торов 12 и 13. Коммутирующая цепочка состоит из последовательно соевует числу входных команд режима рабоТЫ и дкл А и оТК л и ВКЛ в ОТКА Б

пер Лв и „ер вд I И

и

Uc, и

Uo, Uc

и

гз

(, UTJ Ug, Ug,

ЧИСЛО которых

числу тиристоров, которые соединены с управляющими электродами соответ- .ствующих тиристоров.

Устройство 16 управления тиристорами (фиг, 2) составлено из формирователя 17 сигнала переключения режима, число входов которого соответствует числу входных команд переключения режима работы, задающего генератора 18 синхроимпульсов и щиротно- импульсного модулятора 19, выходы которых соединены с соответствующими входами устройства 16. Устройство 16 соедержит также следующие формирователи: . формирователь 20 сигналов включения силовых ключей, имеющего выходы по числу силовых ключей, связанные с управляющими электродами тиристоров этих ключей, вход широтно-им- пульсного сигнала Uy, адресные входы, связанные с входами сигналов режима устройства 16, и два.тактовых входа; формирователь 21 сигнала включения шунтирующего ключа, вьтолненный в виде дизъюнктора, которьй имеет liHBepc- ный вход пшротно-импульсного сигнала, соединенного с аналоговым входом формирователя 20, и прямой вход| формирователь 22 распределительных сигналов, имеющий сигнальные входы, соединенные с выходами формирователя 20 сигналов включения силовых ключей, входы сигналов режима, соединенные с соответствующими входами устройства 16, вход запрета, вход задержанного сигнала переключения режима и вьпсодь, по числу распределительных тиристоров 8-11, связанные с управляющими электродами этих тиристоров; формирователь 23 сигналов коммутаций,

имеющий сигнальные входы по числу распределительных тиристоров, соединенные с соответствующими выходами формирователя 22, вход запрета и выходы по числу коммутирующих тиристоров, связанные с управляющими электродами этих тиристоров с помощью формирователя 24 импульсов запуска

15

тиристоров, через который выходы фор- ю ° входе U и выходе Uj формирог

соответственно.

Формирователь 22 распределительных сигналов (фиг. 5) содержит два формирователя 28 и 29 кратковременных импульсов из положительных перепадов входного сигнала, снабженные V-входами разрешения, которые объединены и образуют вход запрета (Uj .3) формирователя 22, и два фор-г мирователя 30 и 31 кратковременных импульсов из отрицательных фронтов входного сигнала, входы каждой из пар формирователей 28, 30 и 29, 3.1 которых соединены с сигнальными вхомирователей 20-23 связаны с управляющими электродами тиристоров. Кроме того, устройство 16 включает совместитель 25 импульсных сигналов, имеющий входы .широтно-импульсного управляющего сигнала, синхроимпульсов и «сигнала переключения режима, соединенные соответственно с вькодами .модулятора 19, задающего генератора 18 и формирователя 17 сигнала переключения режима, выход широтно-импульсного сигнала, соединенный с со- ответствунлцими входами формирователя 20. и формирователя 21, выход импульсов синхронизации, соединенный с тактовым входом модулятора 19 и с первым тактовым входом формирователя 20, два выхода задержанных сигналов переключения режима, первый из кото рых соединен с вторым тактовым входом формирователя 20, а второй соеди- .нен с входом задержанного сигнала формирователя 22, и выход сигнала .запрета, соединенный с входом запрета формирователя 22 и входом запрета формирователя 23.

Формирователь 17 сигнала переключения режима выполнен в виде дизъюнк- тора, число входов которого соответствует числу входных команд переклю- чения режима работы Ungp дв пер ВА

20

30

35

40

:и

от к А

-отк 6«

25 дами Пз и и., дизъюнктор 32, один , из входов которого подключен непосредственно к входу сигналов режима UBKA я (6) а другой подключен через элемент 33 задержки к входу сигналов режима иЬткд(в) Д мультиплексора 34 и 35, через которые выходы формирователей 28, 30 и 29, 31 связаны с выходами и g, U 9 и U ,о U,., форми-г рователя 22 в соответствии с логическими выражениями FO A B-DOvA-Bx , F1 A-B-DO vA-B .D1, где FO и |F1 - сигналы на выходах мультиплексо- ipoB 34 и 35, DO и D1 - на информаци- оиных, .а А и В - адресных входах этих мультиплексоров. Формирователь 22 содержит также два TV-триггера 36 и 37, выходы которых соединены с адресными входами А и В мультиплексоров 34 и 35 в соответствии с логическими выражениями для первого мульти- плексора А Q , В Q,; для второго мультиплексора А , В Q j, где QI Q2 выходы триггеров 36 и 37 соответственно. Информационные Т-рхо- ды триггеров 36 и 37 соединены с BXQ- дом задержанного сигнала переключения режима , управляющие, V-входы каждого из триггеров 36 и 37 соединены с сигнальными входами Uj и U формирователя 22, а R-входы уставки исходного состояния триггеров 36 и 37 соединены с выходом дизъюнктора 32,

Формирователь 20 сигналов включения силовых ключей выполнен в виде демультиплексора (фиг. 3), имеющего выходы FO, F1 по числу силовых ключей, информационный вход X, служащий входом широтно-испульсного сигнала и,(,адресные входы А, В, С, D, Е, F по числу входных команд режима работы и в(5л л, UOTKA, в UOTKB hep/lB UnepBA и Два тактовых динамических входа СО С1, первьм из которых СО включен на выход импульсов синхронизации совместителя, а второй из которых С1 соединен с первым вы- ходом задержанных сигналов переключения режима совместителя 25.

Формирователь 21 сигнала включения шунтирующего ключа (фиг. 4) состоит из инвертора 26 и дизъюн тора 27, соединяющих входы и выход формирователя в соответствии с логическим выражением а + b с, где а, Ь, с - значения сигнала на инверсном входе широтно-импульсного сигнала Uy, пря0

5

0

5 дами Пз и и., дизъюнктор 32, один , из входов которого подключен непосредственно к входу сигналов режима UBKA я (6) а другой подключен через элемент 33 задержки к входу сигналов режима иЬткд(в) Д мультиплексора 34 и 35, через которые выходы формирователей 28, 30 и 29, 31 связаны с выходами и g, U 9 и U ,о U,., форми-г рователя 22 в соответствии с логическими выражениями FO A B-DOvA-Bx , F1 A-B-DO vA-B .D1, где FO и |F1 - сигналы на выходах мультиплексо- ipoB 34 и 35, DO и D1 - на информаци- оиных, .а А и В - адресных входах этих мультиплексоров. Формирователь 22 содержит также два TV-триггера 36 и 37, выходы которых соединены с адресными входами А и В мультиплексоров 34 и 35 в соответствии с логическими выражениями для первого мульти- плексора А Q , В Q,; для второго мультиплексора А , В Q j, где QI Q2 выходы триггеров 36 и 37 соответственно. Информационные Т-рхо- ды триггеров 36 и 37 соединены с BXQ- дом задержанного сигнала переключения режима , управляющие, V-входы каждого из триггеров 36 и 37 соединены с сигнальными входами Uj и U формирователя 22, а R-входы уставки исходного состояния триггеров 36 и 37 соединены с выходом дизъюнктора 32,

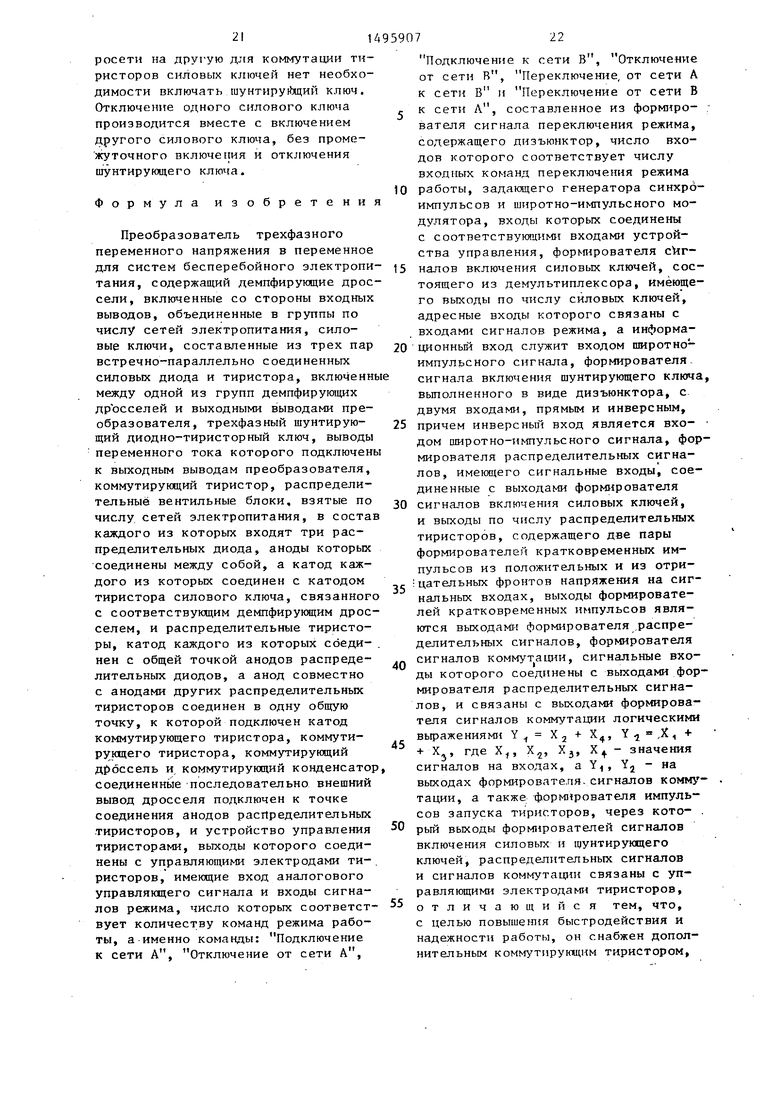

Формирователь 23 сигналов коммутации (фиг, 6) содержит дизъюнкторы 38

5 I

0

5

7Т49

и 39 по числу коммутирующих тиристоров, через которые входы Ug - U формирователя 23 связаны с его выходами и и, в соответствии с логическими вьфажениями Y ., Х + Х, Y,j X , + Хз где Xi, Х-2, Хд, Х - значения сигналов на входах и„ , U, и,д , и , а Y, и, Y - выходах U,. и соответственно, дизъюнктор 40 и элемент 41 запрета, через которые сигнальные входы U и U,o и вход запрета U . формирователя 23 связаны с его дополнительным выходом и в соответствии с логическим вы- ражением Y (X + Х) , где Х2 и Xj - значения сигналов на сигнальных входах Ug и и jg , на входе запрета Ui ,j , Yj - на дополнительном выходе и соответственно.

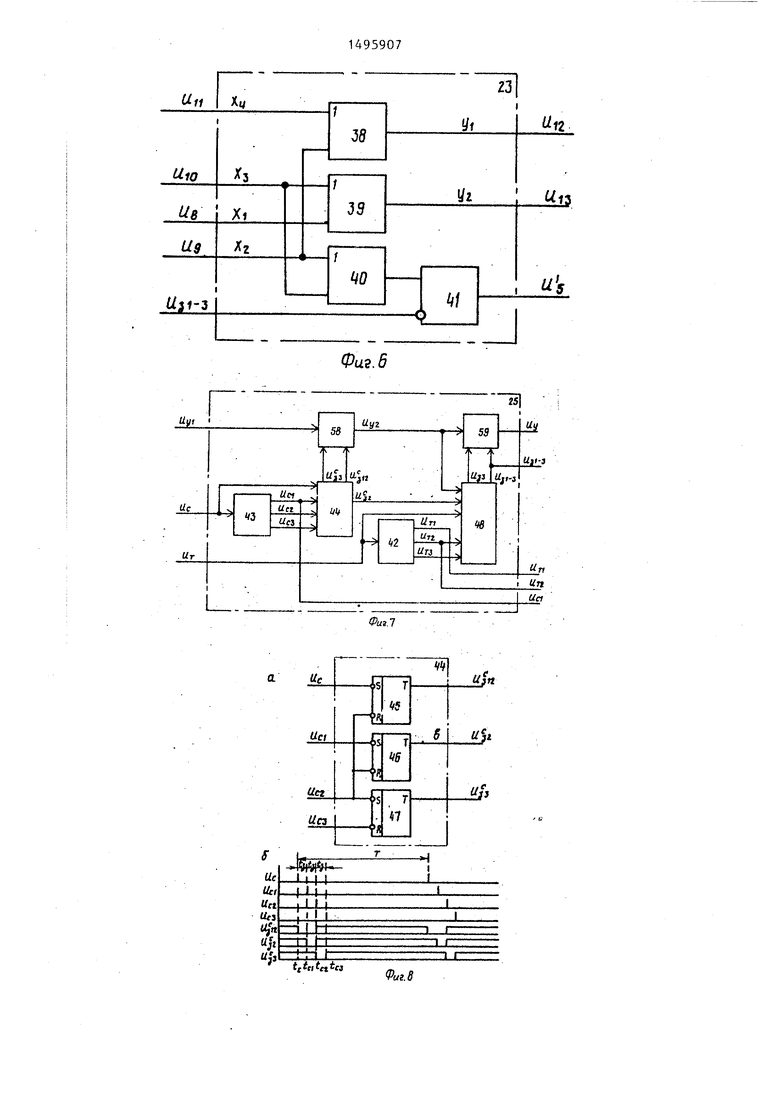

Совместитель 25 импульсных сигналов (фиг, 7) содержит трехсекцион- ный элемент 42 задержки, вход которого образует вход сигнала переключения режима и преобразователя-сов- местителя 25, а выходы первой и второй секций - два выхода задержанных сигналов переключения режима U-, и UT, трехсекционньй элемент 43 задержки синхроимпульсов, вход которог образует вход синхроимпульсов U совместителя 25, а выход первой секции - выход импульсов синхронизации Uci формирователь 44 временных интервалов запрета. Формирователь 44 (фиг. 8) состоит из трех RS-триггеров 45-47. S- и R-входы первого триггера 45 соединены соответственно с входом синхроимпульсов Uj совместителя 25 и с выходом и второй секции элемента 43 задержки, S- и R-входы второго триггера 46 соединены соответственно с выходами U,, и Uc2 первой и второй секций этого элемента.43.. S- и R-входы третьего

триггера 47 соединены соответственно с выходами и и U, второй и третьей секций этого же элемента 43. Совместитель 25 содержит также формирователь 48 управляемых временных интервалов запрета (фиг. 7), состоящий (фиг. 9) из узла 49 задержки, включающего синхронньй D-триггер 50 и RS-триггер 51, Q-выход которого соединен с С-входом синхронизации D-триггера 50, а S- и R-входы которого соединены соответственно с входом сигнала переключения режима U совместителя 25 и выходом третьей

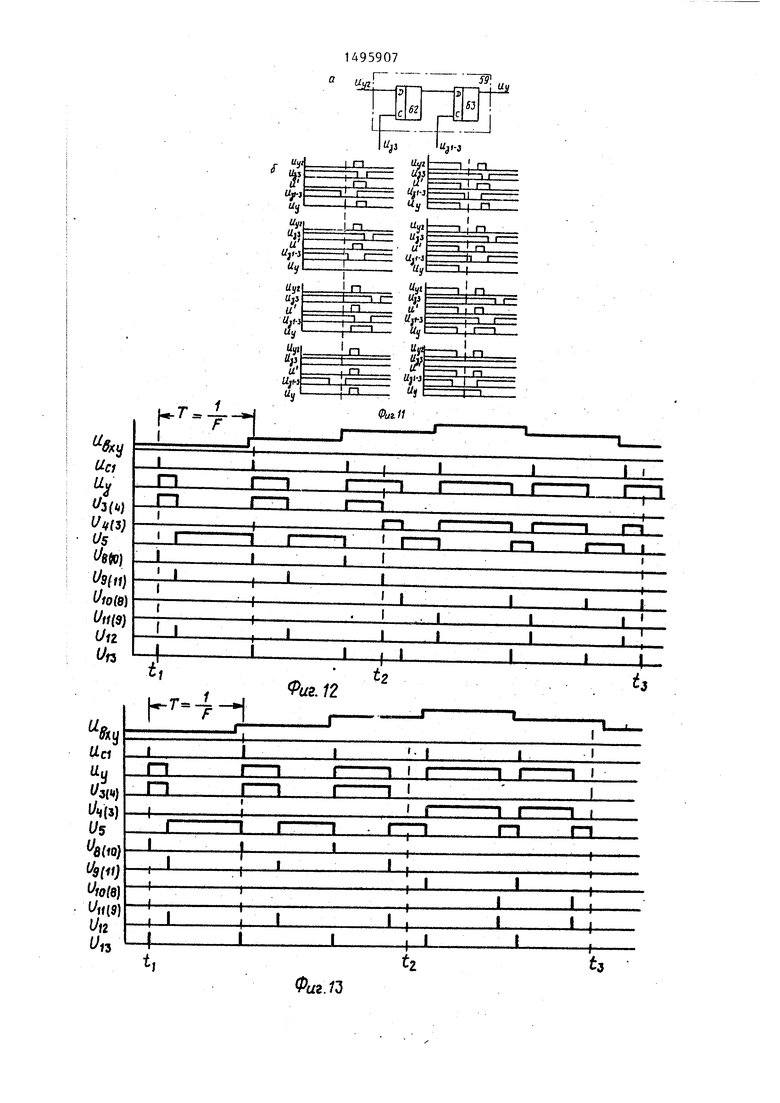

секции элемента 42 задержки, и из двух RS-триггеров 52 и 53, S-вход триггера 52 связан с выходом триггера 46 и выходом второй секции UT элемента 42 задержки через конъюнктор 54, а R-вход соединен с выходом третьей секции U f элемента 42 задержки. Выход второго триггера 53 соединен с выходом сигнала запрета U совместителя 25, его S-вход соединен с входом сигнала переключения режима UT и совместителя 25,. а его R-вход подключен на выход дизъюнктора 55. На выходе дизъюнкто- ра 55 через два элемента 56 и 57 запрета формируется сигнал в соответствии с логическим выражением а-Ь .с + d, где а; Ъ, - сигналы на выходах D-триггера 50, триггера 46, второй и третьей секций элемента 42 задержки соответственно. Кроме того, совместитель 25 содержит два каскадно включенных ограничителя временных интервалов 58 и 59 (фиг. 7), каждьш из которых состоит (фиг. 10 и 11) из двух синхронных D-триггеров 60,и 61 а также 62 и 63, соединенны по схеме двухразрядного сдвигающего регистра с., двумя раздельными тактовыми С-входами так, что С-вход синхронизации каждого из триггеров 60 и 61, а также 62 и 63 представляет отдельньм тактовый вход соответственно U яз и , и 13 f-3 ограничителей 58 и 59 временных интервалов, сигнальный вход Uy. первого из огра- ничителей 58 служит входом широтно-. импульсного управляющего сигнала, а выход второго ограничителя 59 - выходом щиротнр-ийпульсного-сигнала совместителя. Выход Uyj первого ог- раничит еля 58 (фиг. 7) соединен с сигнальным входом U vi второго огра- ни 1ителя 59 и сигнальным входом D- триггера 50 формирователя 48 (фиг.9) Первый и второй тактовые входы U t

Сf

к и первого ограничителя 58 соединены соответственно с выходами триггеров 47. и 45 формирователя 44 (фиг. 8), а первый и второй тактовые входы и J и и |, {-3 второго ограничителя 59 (фиг. 10) соединены (фиг.7) соответственно с выходами триггеров .52 и 53 формирователя 48 (фиг. 9).

Устройство работает следующим образом.

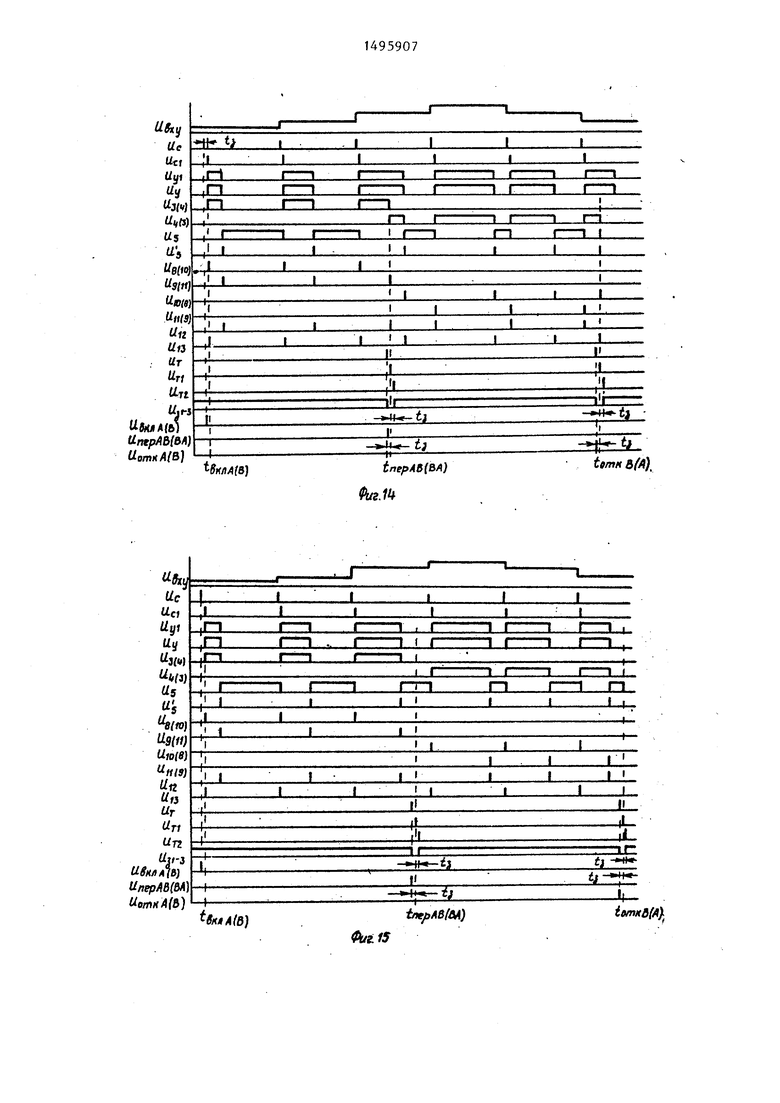

Для подключения электроприемника, например, к сети электропитания А

(В),(фиг. 1) в момент времени t (фиг. 12 и 13) включаются тиристоры силового ключа 3 (4) и тиристоры 8, 13 (10, 13). При этом выходные выводы преобразователя подключаются к е;го входу А (В), а крммутирукяций конденсатор 15 заряжается до полярности, указанной на фиг. 1 без скобок. Его заряд проходит по цепи, включающей коммутирующий дроссель 14,тиристор 8 (10), диоды распределительного вентильного блока 6 (7), демпфирующий дроссель 1 (2), сеть электропитания А (В), диоды силового ключа 3 (4), диоды шунтирующего ключа 5, тиристор 13. При подключенном электропрйемнике возможны различные режимы работы преобразователя:.широт но-импульсное регулирование (ШИР) выходных напряжений, перевод электропитания с одной сети электропитания на другую и наоборот, отключение электроприемника от обеих сетей.

Режим ШИР осуществляется за счет периодического отключения электро- приемника с последующим его подключением на регулируемые отрезки времени. Подключение электроприемника, например, к сети А (В) и его отключение от сети А (В) производится с помощью силового ключа 3 (4). При каждом отключении от сети электроприемник замыкается накоротко птунти- рукндим ключом 5 для замыкания реактивных токов. На выходе преобразователя формируются напряжения, имеющие регулируемые паузы, длительность которых определяется сигналом управления и (фиг. 12 и 13), поступающим на входы формирователей 20 и 21 (фиг. 2). В режиме ШИР тиристоры в каждом из силовых ключей 3(4) и 5 включаются одновременно путем подачи на них импульсов запуска U j (U) .и Uj (фиг. 12 и 13), формируемых .устройством 16 управления (фиг. 1).

При включении тиристоров ключа 3 (4) электроприемник оказывается подключенным к сети А (В). Выключение тиристоров ключа 3 (4) осуществляется с помощью принудительной коммутации. Для этого с них снима- ются импульсы запуска и подаются на тиристоры трехфазного шунтирующего ключа 5, распределительный тиристор 9 (11) и коммутирующий тиристор 12 (фиг. 12 и 13). Принудительная коммутация происходит при протекании

импульса тока коммутации за счет пе резаряда коммутирующего 1 онденсдто- ра 15 по цепи: распределительный тиристор 9 (11), диоды распределительного вентильного блока 6 (7), диоды силового ключа 3 (4), диоды трехфазного шунтирующего ключа 5, коммутирующий тиристор 12, коммутирующий

O дроссель 14. При протекании этого импульса тока на открытых диодах силового ключа 3 (4) падает напряжение, которое оказывается приложенным к тиристорам ключа 3 (4) в обрат ном

5 (запирающем) направлении. Под действием этого обратного напряжения происходит выключение (запирание) тиристоров; силового ключа 3(4) . При этом короткое замыкание сети электропитания не

0 развивается благодаря наличию демпфирующих дросселей. Процесс коммутации длится время, достаточное для выключения этих тиристоров. При этом коммутирующий конденсатор 15 переза5 ряжается до полярности, указанной

на фиг. 1 в скобках, при которой протекает последующая коммутация.

В режиме ШИР каждый раз при вы- 0 ключении тиристоров силового ключа 3 (4) включается трехфазный шунтирующий ключ 5, которьй создает цепь для протекания реактивных токов электроприемника. Выключение тиристоров 5 шунтирующего ключа 5 также,осущест- вляется с помощью принудительной коммутации. Для этого с них снимаются импульсы запуска и подаются на распределительный тиристор 8 (10) и ком- 0 мутирующий тиристор 13 (фиг. 12 и

13). Принудительная коммутация происходит за счет протекания импульса тока коммутации в ходе Лерезаряда коммутирующего конденсатора 15 по 5 цепи: коммутирукщий дроссель 14, распределительный тиристор 8 (10), диоды распределительного вентильного блока 6 (7), диоды силового ключа 3 (4), диоды трехфазного шунтирующе- го ключа 5, коммутирующий тиристор 13. При протекании импульса тока коммутации через диоды ключа 5 тиристоры этого ключа выключаются под дей- .ствием обратного напряжения, равно- :го падению напряжения на открытых диодах. Процесс коммутации длится время, достаточное для вьпслючения этих тиристоров. При этом коммутирующий конденсатор 15 перезаряжается

П149

до полярности, указанной На фиг. 1 без скобок,

В режиме перевода питания с одной электросети на другую, например, с сети А (В) на сеть В (А) в момент t,, а также при отключении электро-1

приемника.

например, в момент

tj воз

можны два случая. В первом случае (фиг, 12) момент перевода (или отключения) питания совпадает с включенным состоянием силового ключа 3 (4) и требуется выключение тиристоров ключа 3 (4) с включением тиристоров ключа 4 (3). Во втором случае (фиг. 13) момент перевода (или отключения) не совпадает с включенным состоянием силового ключа 3 (4) и коммутатдая тиристоров силовых ключей не требуется. Выключение ти- ристоров силового ключа 3 (4) в режиме перевода (или отключения) питания осуществляется в помощью принудительной коммутации одновременно с включением тиристоров силового ключа 4 (3). 25 представлена на фиг, 2, Работа всего

Принудительная коммутация тиристоров силового ключа 3 (4) в этот момент осуществляется также путем подачи импульсов запуска на распределительный тиристор 9 (11) и коммутирующий тиристор 12 (фиг, 12). В результате.- после перезаряда коммутирующего конденсатора 15 по цепи: разпределитель ньй тиристор 9 (11), диоды распределительного вентильного блока 6 (7), диоды силового ключа 3 (4), диоды . шунтирующего ключа 5, коммутирунзщий тиристор 12, коммутирующий дроссель 14 электроприемник переключается на сеть В (А) (или отключается). Существенным отличием такого перевода питания с одной электросети на другую является прямое переключение силовых ключей 3 (4) без промежуточного включения шунтирующего ключа 5, Возможность такого перевода и обеспечивает достижение цели изобретения.

После перевода питания на сеть В (А) режим ШИР осуществляется также путем периодического отключения электроприемника от сети на регулируемые отрезки времени. Подключение электроприемника к сети и его отключение от сети в этом случае производится с помощью силового ключа 4 (3). При отключении от сети электроприемник замыкается накоротко шунтирующим ключом 5. Принудительная коммутация тиристороп силового ключа 4 (3) осу

j 0

2

ществляется путем подачи импульсов запуска на распределительный тиристор 10 (8) и коммутирующий тиристор 13 (цепь перезаряда конденсатора 15: тиристор 10 (8), диоды вентильного блока 7 (6), диоды силового ключа 4 (3), диоды шунтирующего ключа 5, тиристор 13, дроссель 14), а принудительная коммутация тиристоров шунти- рукщего ключа 5 осуществляется путем подачи И : ульсов запуска на распре- делительньй тиристор 11 (9) и комму- тирующий тиристор 12 (цепь перезаряда конденсатора 15: тиристор 11 (9), диоды вентильного блока 7 (6), диоды силового ключа 4 (3), диоды шунтирующего ключа 5, тиристор 12, дроссель 14) .

Включение тиристоров во всех режимах работы и в нужной последовательности и очередности осуществляется с помощью устройства 16 управления тиристорами, блок-схема которого

0

5

0

5

0

5

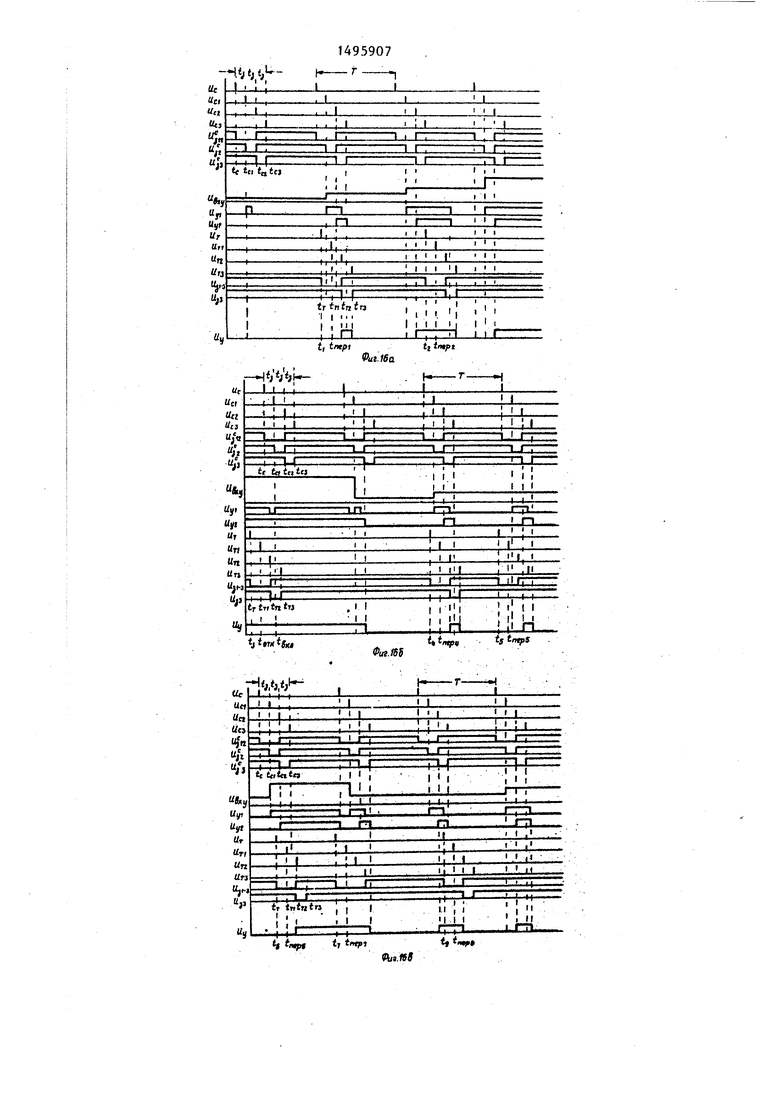

преобразователя синхронизируется двумя независимыми последовательностями: синхроимпульсов и и сигналив переключения режима U (фиг. 14 и 15). Последовательность синхроимпульсов и формируется на выходе задающего генератора 18 (фиг. 2) , при поступлении на его вход любого из сигналов команды включения на сеть А (В) Л{6) Сфиг. 14 и 15). Сигналы переключения режима U формируются с помощью формирователя 17 (фиг. 2) логическим сложением сигналов команд переключения сетей электропитания Uf,(6fl) отключения электроприемника и (j д(,.(фиг. 14 и 15). Синхроимпульсы Ue и сигналы переключения режима U. формиру отся независимо друг от.друга; их взаимное расположение зависит Лишь от моментов появления команд режима работы и в общем случае может быть произвольным. Поэтому интервал между импульсами в общем случае может оказаться меньше длительности коммутационных процессов в узле коммутации, J4TO делает невозможным вьтолнение команд в этих случаях или приводит к срыйу коммутации,, т.е. снижению Надёжности всего устройства.. Для обеспечения надежной работы преобразователя во всех случаях добиваются такого согласования синхроимпульсов и сигналов переключения режима, при

Котором интервалы между началом, соседних коммутаций не могут стать меньшими, чем длительность коммутационных процессов. Это вьгполняется с помощью совместителя 25 импульсных сигналов (фиг. 2). Совместитель 25 сопряжен с модулятором 19, который преобразует аналоговый сигнал U.j в широтно-импульсный (ШИ) управ ляющий сигнал V (фиг. 2). На выходах совместителя 25 формируются задержанные сигналы переключения режима U , и ШИ-сигнал U,, опреде- .ляющие моменты включения тиристоров 8-13, а также сигнал запрета U j . , служащий для обеспечения работы других узлов устройства 16 (фиг. 14 и 15). Совместитель 25 работает таким образом (фиг, 7), что при поступле- НИИ на его входы импульсных сигналов IIj. , и и и у, они преобразуются в импульсные сигналы Uj, UT,, U и и„, которые отличаются от исходных тем, что минимальньм интервал между любыми их фронтами во всех случаях ограничивается на заданном уровне (фиг. 16), которьш выбирается не меньше длительности коммутационных процессов во всех режимах работы.

Совместитель 25 (фиг. 7) согласо- вьтает три импульсных сигнала Uc, Hf, и у. Синхроимпульсы DC с помощь трехсекционного элемента 43 задержки последовательно сдвигаются на равные отрезки времени t,, в результате чег на выходе элемента 43 формируются три последовательности задержанных .синхроимпульсов Uc, , Uci J Ucjj опре-. деляющих границы трех интервалов запрета (И : , tc, ,, H jEttj.,, tcsJ (фиг. 16). Таким образом, после каждого синхроимпульса Up в пределах любого периода синхронизации Т последовательно выделяются три интервала запрета И f, И , И . С помощью этих импульсов, поступающих на входы форш-грователя 44 временных интервалов запрета (фиг. 7), формируются три системы импульсов запрета U,j, , и j, (фиг. 8 и 16), для которых в пределах периода синхронизации Т справедливы вьфажения: , ГО, ,, t,J;

U, t, r Г t- 4- 1

1, t t, tc2

;

го, t .,, 1г |i, t t,

О, t с t

1,

С2

ci

сз

-сз

; .

Эти импульсы используются для ограничения минимума временных интервалов в ШИ-сигнале U... Импульсы U. сVgJ

и и J ,2 поступают на тактовые входы первого ограничителя 58 временных интервалов, на сигнальный вход которого подается ПИ управляющий сигнал

и

V1

(фиг. 7 и 10).

Q 5 g 5 о

0

Управляющий ШИ-сигнал U, фдрми- руется на выходе модулятора 19 таким образом, что каждый его положительный фронт совпадает с появлением задержанного синхроимпульса Uci, а отрицательный фронт появляется с задержкой от положительного на время , пропорциональное значению аналогового управляющего сигнала к у (Фиг. 2 и 14). При малых значениях аналогового сигнала Ujxy длительность импульса ilM-сигнала U у (U )i 0) мала, а при юольших его значениях пауза ШИ-сигна- ла и vy, (и, 0) может оказаться меньше длительности коммутационных , цессов в узле коммутации. Такие ситуации ис ключаются с помощью ограничителя 58 интервалов (фиг. 7 и 10). В нем из ШИ-сигнала U vi с помощью импульсов запрета Uj.3 и U i.,, формируется ШИ-сигнал U yj, который отличается от исходного тем, что минимальный интервал между любыми его перепадами во всех случаях ограничивается на заданном уровне t, (фиг. 10). Если пределы изменения аналогового сигнала U,, ограничены так, что длительность импульса или паузы ШИ-сигнала U 4,1 не достигает значений, меньших, чем длительность коммутационных процессов, то необходимость в использовании ограничителя 58 интервалов отпадает (фиг. 7 и 10). Временные диаграммы, приведенные на фиг. 10, поясняют работу ограгичителя 58 интервалов при всех возможных режимах. Импульсы и паузы на его сигнальном входе U,,, , длительность которых меньше интервала запрета t,, ликвидируются или заполняются на его выходе Uy благодаря свойству синхронных D-триг- геров: с появлением напряжения на С-входе синхронизащ«1 D-триггера 60 (61) напряжение Q , действовавшее непосредственно перед этим на его

15

сигнальном входе, передается на выход D-триггера Uyj ; при отсутствии напряжения на С-входе синхронизации на выходе D-триггера сохраняется установленное значение напряжения. В связи с этим D-триггер -60 оказывает влияние на ШИ-сигнал U „ лишь в тех случаях, когда отрицательный фронт иш-сигнала U, попадает в интервал запрета U,. В этих случаях указанный фронт задерживается D-триггером 60 до окончания интервала и (в этом случае импульс расширяется). Б остальных случаях D-триггер 60 влияния не оказывает. В результате на его вькоде образуется ШИ-сигнал U , поступающий на сигнальньй вход D- триггера 61 (фиг. 10). Далее во всех случаях, когда в интервал запрета ,, t.2(Фиг. 8 и 16) попадает только положительный фронт Ш-сигнала U (фиг. 1C), этот фронт задерживается D-триггером 61 до окончания интервала И, (импульс сжимается) . Если в интервал И,, попадает сначала положительный фронт ШИ-сигнала u ,а затем и следующий за ним отрицательный фронт, то состояние D-триггера 61 на интервале И. j не изменяется (заполняется короткая пауза). В результате на выходе D-триггера 61 образуется ШИ- ,сигнал и у, с ограничением минималь- ного интервала между его любыми перепадами. Однако ограничитель 58 интервалов (фиг. 7 и 10) не исключает возможности сближения перепадов ШИ- сигнала и vjj с сигналами команд переключения режима UT- (фиг. 16) на интервал, меньший чем длительность процессов коммутации в узле коммутадаи. Такие ситуации исключаются с помощью ограничителя 59 временных инте{5валов (фиг. 7 и 11) В нем из ШИ-сигнала и ,,2 формируется ШИ-сигнал и,, который отличается от исходного тем, что минимальный интервал между любыми его фронтами и сигналами команд переключения, режима во всех случаях ограничивается на заданном уровне t j. Достигается это следующим образом.

Сигналы команд переключения режима U последовательно сдвигаются на р.авные отрезки времени t с помощью трехсекционного элемента 42 задержки (фиг. 7). В результате на его выходе формируются три последовательности задержанных сигналов переклю149590716

чения U|-, , UTI тз определяющих границы трех интервалов запрета:

Hr,,, .,, Н eftri, tT3 (фиг. 16).

Таким образом, после каждого си нала команды переключения U посл д вательно выделяются три интервал запрета И|1 , ИJ.2, . С помощью э 10 сигналов и импульсов U/, U, в фо мирователе 48 управляемых временны интервалов запрета (фиг. 7) формир ются две системы импульсов запрета

Ug. 1-3 нбобходи

5 мые для работы ограничителя 59 интервалов. Ограничитель 59 работает так же, как и ограничитель 58. Его работа поясняется временными диагр мами, приведенными на фиг. 11. Во

20 всех случа:ях, когда на интервале з прета Uj.3 на С-Ёходе синхронизации D-триггера 62 напряжение отсутству ет и в интервал запрета Uj. попада только отрицательный фронт ШИ-сигн

25 ла Uyj, этот фронт задерживается

D-триггером 62 до окончания интерв ла И г. j (импульс расширяется). В ос тальных случаях D-триггер 62 влиян не оказывает. Б результате на его

30 выходе образуется ШИ-сигнал U ,пос тупающий на сигнальный вход D-триг гера 63 (фиг. 11). Далее во всех случаях, когда на интервале отсутс вия напряжения на С-входе синхрони зации D-триггера 63 (U . 0) по ляется только положительный фронт ШИ-сигнала U , этот перепад задерживается D-триггером 63 и его сост ние на указанном интервале не изме ется (ликвидируется короткий импул Если в этот интервал попадает снач ла отрицательный фронт ШИ-сигнала и , а затем и следующий за ним его положительньй фронт, то состояние ,D- pиггepa 63 на указанном интерва

5 также не изменяется (заполняется к роткая пауза), В отличие от огран чителя 58 на входы рассма . (риваемого ограничителя 59 поступаю управляемые импульсы запрета И,.

50 (фиг, 7, It и 16), параметры к торых определенным образом зависят от взаимного расположения синхроим пульсов Ug; и сигналов команд перек чения режима и.

55 Эта зависимость заключается в с дующем (фиг. 16), На любом интерва между смежными командами переключе ния режима сигнал Uj. О в момен

40

Hr,,, .,, . eftri, tT3 (фиг. 16).

Таким образом, после каждого сигнала команды переключения U после- д вательно выделяются три интервала запрета И|1 , ИJ.2, . С помощью этих сигналов и импульсов U/, U, в формирователе 48 управляемых временных интервалов запрета (фиг. 7) формируются две системы импульсов запрета

Ug. 1-3 нбобходи5 мые для работы ограничителя 59 интервалов. Ограничитель 59 работает так же, как и ограничитель 58. Его работа поясняется временными диаграммами, приведенными на фиг. 11. Во

0 всех случа:ях, когда на интервале запрета Uj.3 на С-Ёходе синхронизации D-триггера 62 напряжение отсутству-, ет и в интервал запрета Uj. попадает только отрицательный фронт ШИ-сигна5 ла Uyj, этот фронт задерживается

D-триггером 62 до окончания интервала И г. j (импульс расширяется). В остальных случаях D-триггер 62 влияния не оказывает. Б результате на его

0 выходе образуется ШИ-сигнал U ,поступающий на сигнальный вход D-триггера 63 (фиг. 11). Далее во всех случаях, когда на интервале отсутствия напряжения на С-входе синхронизации D-триггера 63 (U . 0) появляется только положительный фронт ШИ-сигнала U , этот перепад задерживается D-триггером 63 и его состояние на указанном интервале не изменяется (ликвидируется короткий импульс). Если в этот интервал попадает сначала отрицательный фронт ШИ-сигнала и , а затем и следующий за ним его положительньй фронт, то состояние ,D- pиггepa 63 на указанном интервале

5 также не изменяется (заполняется короткая пауза), В отличие от огран - чителя 58 на входы рассмат- . (риваемого ограничителя 59 поступают управляемые импульсы запрета И,.,

0 (фиг, 7, It и 16), параметры которых определенным образом зависят от взаимного расположения синхроимпульсов Ug; и сигналов команд переключения режима и.

5 Эта зависимость заключается в следующем (фиг. 16), На любом интервале между смежными командами переключения режима сигнал Uj. О в моменты

0

времени t 6 t , t },если вьтолня- ется условие

Т7

t

С1

ci J

в противном случае на всем интервале между смежными командами переключения режима этот импульс отсутствует, т.е. Ji3 Сигнал U, ,..j О на интервале времени , tj, т.е.

ГО, t , t

|i, t

T5J;

гз.

(1)

если одновременно выполняются два условия

.

О

t

(2)

С1

-с-г

,

случае Uj.,.j О на интер

г 1

. т.е.

и.

0. t eft,, 31-э- ii, . t,J.

(3)

Такая зависимость импульсов запрета

и

5 VV

и

З-э

от взаимного расположения синхроимпульсов DC и сигналов команд переключения режима U. обеспечивает вьтолнение ограничителем 59 (фиг. 7 и 11) своих функций,« а именно ограничение минимального интервала между любыми перепадами ШИ- U,,J и сигналами команд переключения режима и т на установленном уровне t4 во всех возможных случаях. Управляемые импульсы запрета , 1-3 удовлетворяющие указанным требованиям, формируются в формирователе 48 управляемых временных интервалов запрета (фиг. 7 и 9). Временные диаграммы, приведенные на фиг. 9, поясняют работу этого формирователя 48. Импульс запрета Ui Формируется Она вькоде триггера 52, если импульс

30

35

40

45

и

т-г

поступает на его S-вход, что в

ШИ-сигнал Uy с его информационного входа,X подается на выход U (фиг. 3), если на любой из его адресных входов А, F поступает сигнал режима работы Ug д или- в А « Если сигнал режима работы g или Upjgp g поступит на любой из адресных входов С, Е, то ШИ-сигнал Uy с инЧ формационного входа X подается на выход и. Но эти включения ШИ-сигнала Ну на выход и2 или } осуществляются- лишь в момент поступления сигналов и(.,или U т- на соответствующий тактовый вход СО или С1 формирователя 20.. При этом тактовый вход СО определяет прохождение сигнала на выход с адресных входов А и С,, а тактовый вход С1 - с адресных входов Ё и F. Если сигнал режима работы UOTK л или о поступает на любой из адресных входов В и D, прохождение ШИ-сигнала U блокируется и бн не проходит ни на од ин из выходов

т.е. t.eCtd, tcl(фиг. 9 и 16).

свою очередь благодаря действию

койъюнктора 54 возможно, если 0,50 формирователя 20. Работу этого формирователя 20 поясняют и временные диаграммы (фиг. 14-16).

Управление запуском распределительных тиристоров 8-11 (фиг. 1 и 2) в соответствии с общим алгоритмом работы преобразователя (фиг. 12 -15) обеспечивается формирователем 22 распределительных сигналов (фиг, 2 и 5)

го. Импульс запрета U ,.jформируется на,

выходе триггера 53 с помощью импульсов и и и,, поступающих на его входы во всех случаях, когда на его R-вход не приходит импульс и. Если импульс и проходит, то импульс иI,. 5 сокращается, т.е. соответ10

15

0

5

0

5

0

5

ствует вьфажению (3). Если импульс и не проходит, то импульсу U -з соответствует выражение (1). Прохож-г дение импульса и т 2 на R-вход триггера 53 оказывается возможным при выполнении условий (2), что обеспечивается логической схемой, состоящей из соответственно соединенных триггеров 50 и 51, а также элементов 56 и 57.

Управление силовыми ключами 3 и 4 (фиг. 1) обеспечивается с помощью формирователя 20 сигналов включения силовых ключей, на выходах которого формируются сигналы Uv, и U Этими сигналами через формирователи 24 импульсов запуска включаются тиристоры ключей 3 и 4 (фиг. 2). Сигналы и 2 и и формируются из ШИ-сигнала и у путем его переключения на выход Uj под действием импульсных сигналов Uc, , U-rt и сигналов режима UgxAB

(ивклД(в) UoTAA(6) UnepflBCefljK 2, 3, 14-16). Эти переключения осуществляются формирователем 20, который работает следующим образом.

ШИ-сигнал Uy с его информационного входа,X подается на выход U (фиг. 3), если на любой из его адресных входов А, F поступает сигнал режима работы Ug д или- в А « Если сигнал режима работы g или Upjgp g поступит на любой из адресных входов С, Е, то ШИ-сигнал Uy с инЧ формационного входа X подается на выход и. Но эти включения ШИ-сигнала Ну на выход и2 или } осуществляются- лишь в момент поступления сигналов и(.,или U т- на соответствующий тактовый вход СО или С1 формирователя 20.. При этом тактовый вход СО определяет прохождение сигнала на выход с адресных входов А и С,, а тактовый вход С1 - с адресных входов Ё и F. Если сигнал режима работы UOTK л или о поступает на любой из адресных входов В и D, прохождение ШИ-сигнала U блокируется и бн не проходит ни на од ин из выходов

0 формирователя 20. Работу этого формирователя 20 поясняют и временные диаграммы (фиг. 14-16).

19

1495907

под действием сигналов включения си- Повых ключей Uj и U, задержанного пригнала переключения режима UTZ сиг- йала запрета П (.j и сигналов режи- На Vgnnfl, екл в ornAt о-гки

I Фор шрователь 22 содержит два |канала формирования распределительны |г.игналов: канал формирования сигна- hoB Ug и Uj и канал формирования Сигналов и,д и и . Работа этих ка-- налов управляется схемой, состоящей Из триггеров 36 и 37, диэъюнктора р2 и элемента 33 задержки. Временные диаграммы, приведенные на фиг. 17, юясняют работу формирователя 22.

аспределительные сигналы Ug - U, ()ормируются из передних и задних (|)ронтов сигналов Uj и U с помощью оормирователей 28-31 кратковременных импульсов. Фронты сигнала Uj исполь уются для формирования распредели- : ельных сигналов Ug и Ug, а фронты ;игнала 0 - для формирования распре делительных сигналов U, и U,, , Но какие .фронты (передние или задние)

(и) используются для фор- распределительных сигнасигнала U, нирования

jjioB Ug и Ug (и,дИ и f, ) , зависит

(|)т очередности и особенности поступ- :|1ения команд переключения сетей элек- {ропитания ( Upep е;,). ; Эта зависимость может быть сфор- 1 1улирована следующим образом. Каждый аз при переводе питания с одной се-, и на другую в случаях, когда момент йеревода совпадает с включенным сос- оянием силового ключа 3 или 4, ны- йолняются два условия; во входящем и работу канале формирования распределительных сигналов Ug, и 9 или

U

fO

и

11

измеряется наименование

онта (передний, задний) сигнала lifj или и,.который используется для формирования распределительных сигналов и g и Uj (U, и U ), а так- же запрещается формирование кратко- гфеменного импульса от первого переднего фронта поступакяцего сигнала и, или и. Например, на инт1врвале К , t сигналы U- формируются от передних, а Uj - от задних фронтов сигнала в момент t запрещается формирование кратковременного импульса от переднего фронта первого импульса сигнала U,; на интервале t t,, t,J сигналы и ,д формиру- ьвтся от задних; я U ,, - от перед1тх

0

0

5

фронтов сигнала

20

и.

30

; на интервале

t , tj сигналы и формируются уже от задних, а Ug - от передних фронтов сигнала U и т.д. Изменения наименования фронта сигнала U или и, которьш используется для формирования распределительных сигналов Ug и Ug (UfpИ и ) , обеспечивается с помощью TV-триггеров 36 и 37 за счет соответствующего изменения потенциалов на адресных входах А и В мультиплексоров 34 и 35 (фиг. 5). Запрет формирования кратковременного

г импульса от соответствующего переднего фронта сигнала Uj или U4 обеспечивается через V-входы разрешения формирователей 28 и 29 путем подачи на них сигналов запрета U j,. . Через дизъюнктор 32 и злемент 33 задержки сигналами в б UBKA & Ujj д и UOT g осуществляется установка триггеров 36 и 37 в исходное состояние.

Управление агапуском коммутирующих тиристоров 12 и 13 (фиг. .1 и 2) в соответствии с общим .алгоритмом работы преобразователя обеспечивается сигналами U,, и U, , которые формируются на выходе формирователя 23 сигналов коммутации (фиг. 2 и 6) под действием распределительных сигналов Uo - Uj . Сигнал и 12 обеспечивающий запуск тиристора 12, формируется из сигналов Ug и U.j дизъюнктором 38,

35 а сигнал ,обеспечиваюций запуск тиристора 13, - из сигналов .U. и

и

(О

дизъюнктором 39. Дополнительно

к этому в формирователе 23 с помощью дизъюнктора 40 и элемента 41 из сиг40 налов Uj и и 10 под действием сигнала запрета и(-д формируется сигнал Uj для дополнительного запуска шунтирующего ключа 5 (фиг. 14 и I s). Управление запуском тиристоров

45 шунтирующего ключа 5 (фиг. 1 и 2) в соответствии с общим алгоритмом работы преобразователя обеспечивается сигналом и. Этот сигнал формируется на выходе формирователя 21

50 сигнала включения шунтирующего ключа (фиг. 2 и 4) из ШИ-сигнала Uy и сигнала дополнительного запуска U с помощью инвертора 26 и дизъгонктора 27. Работа формирователя 21 поясня55 ется временными диаграммами на фиг. 14 и 15.

При работе преобразователя в момент перевода питания с одной электросети иа другую коммутации тиристоров силовых ключей нет необходимости включать шунтируйщий ключ. Отключение одного силового ключа производится вместе с включением другого силового ключа, без проме- жуточного включе шя и отключения шунтирующего ключа.

Формула изобретения

Преобразователь трехфазного переменного напряжения в переменное для систем бесперебойного электропи тания, содержащий демпфирующие дроссели, включенные со стороны входных выводов, объединенные в группы по числу сетей электропитания, силовые ключи, составленные из трех пар встречно-параллельно соединенных силовых диода и тиристора, включенн между одной из групп демпфирующих дросселей и выходными выводами преобразователя, трехфазный шунтирую- щий диодно-тиристорный ключ, выводы переменного тока которого подключены к выходным выводам преобразователя, коммутирующий тиристор, распределительные вентильные блоки, взятые по числу сетей электропитания, в состав каждого из которых входят три распределительных диода, аноды которых соединены между собой, а катод каждого из которых соединен с катодом тиристора силового ключа, связанного с соответствующим демпфирующим дросселем, и распределительные тиристоры, катод каждого из которых соединен с общей точкой анодов распределительных диодов, а анод совместно с анодами других распределительных тиристоров соединен в одну общую точку, к которой подключен катод коммутирующего тиристора, коммутирующего тиристора, коммутирующий дроссель и коммутирующий конденсатор соединенные последовательно внешний вывод дросселя подключен к точке соединения анодов распределительных тиристоров, и устройство управления тиристорами, выходы которого соединены с уп равляющими электродами ти- . ристоров, имеющие вход аналогового управляющего сигнала и входы сигналов режима, число которых соответст- вует количест;ву команд режима работы, а именно команды: Подключение к сети А, Отключение от сети А,

10

5 20 25 д 0 5

35

40

5

Подключение к сети В, Отключение от сети В, Переключение, от сети А к сети в и Переключение от сети В к сети Л, составленное из формиро- ; вателя сигнала переключения режима, содержащего дизъюнктор, число входов которого соответствует числу входных команд переключения режима работы, задакщего генератора синхроимпульсов и широтно-импульсного модулятора, входы которых соединены с соответствующими входами устройства управления, форьшрователя cVir- налов включения силовых ключей, состоящего из демультиплексора, имеющего выходы по числу силовых ключей, адресные входы которого связаны с входами сигналов режима, а информа- ционньй вход служит входом широтно- импульсного сигнала, формирователя, сигнала включения шунтирующего ключа, выполненного в виде дизъюнктора, с. двумя входами, прямым и инверсным, причем инверсный вход является вхо- дом широтно-иьтульсного сигнала, формирователя распределительных сигналов, имеющего сигнальные входы, соединенные с выходами формирователя сигналов включения силовых ключей, и выходы по числу распределительных тиристоров, содержащего две пары формирователей кратковременных импульсов из положительных и из отри- цательных фронтов напряжения на сигнальных входах, выходы формирователей кратковременных импульсов являются вьЕходаки формирователя .распределительных сигналов, формирователя сигналов коммутации, сигнальные входы которого соединены с выходами формирователя распределительных сигналов, и связаны с выходами формирователя сигналов коммутации логическими выражениями Y Х + Х, Y,X, + + X , где Х, Х, Xj, значения сигналов на входах, а Y, Yj - на выходах формирователя-сигналов коммутации, а также формирователя импульсов запуска тиристоров, через кото- . рый выходы формирователей сигналов включения силовых и шунтирующего ключей, распределительных сигналов и сигналов коммутации связаны с управляющими электродами тиристоров, отличающийся тем, что, с целью повышения быстродействия и надежности работы, он снабжен дополнительным коммутирующим тиристором.

Д:()Т((.).г1Ь1ительными распредепитепьными тиристорами по числу распределительных вентильных блоков, катод каждого дополнительного распределитель- нЬго тиристора соединен с общей точ- кпй анодов распределительных диодов, а| анод совместно с анодами других дЬполнительных распределительных тиристоров соединен в одну общую TJoMKy, к которой подключен катод дополнительного коммутирующего тиристора и внешний вывод коммутирующего конденсатора, в качестве трехфазного шунтирующего ключа применен диодно- Т Иристорный ключ в виде трех ключей и|з встречно-параллельно включенных диода и .тиристора, один из выводов которых, связанный с катодом диода, объединен в общую точку, соединенную с анодами коммутируЕощих тиристоров, формирователь распределительных сигналов дополнен входами сигналов режима, соединенными с соответствующими входами устройства управления тиристорами, входом запрета, образо- BaHiibiM объединением входов разрешения формирователей кратковременных и|мпульсов из положительных фронтов, к|оторыми они дополнительно снабжены, также входом задержанного сигнала п|ереключения режима, а также дополнен дизъюнктором, один из входов ко- Tloporo непосредственно, а другой ч|ерез элемент задержки подключены к; выходам сигналов режима, двумя Мулы иплексорами, через которые вы- формирователей кратковременных импульсов связаны с выходами формнро- йателя распределительнь1х сигналов в соответствии с логическими выражениями FO А-В-DO :V А-В -D1 , F1 1 А-В-DO VA-B-D1, сигналы FO и Р1 на выходах мультиплексоров DO и D1 - ня информационных а А и В адресных входах этих мультиплексоров, дву- Ия TV-триггерами, выходы которых соединены с адресными входами мультиплексоров в соответствии с логическими выражениями дляпервого мультиплексора А Q , В Q,., для второго мультиплексора А Q, В Q, где Q, и QJ - выходы TV-триггеров, информационные Т-входы которых соединены с входом задержанного сигнала пере- вглючепия режима, а управляющие V-BXO- ды соединены с соответствующими сигнальными входаьш формирователя распределительных сигналов, а R-входы

0

5

0

5

0

5

0

5

установки исходного состояния триггеров соединены с выходом дизъюнкто- ра, демультиплексор формирователя сигналов включения силовых ключей дополнен тактовыми входами, каждьй из которых связан с его адресными входами, устройство управления тиристорами дополнено совместителем импульсных сигналов, имеющим входы широтно- импульсного управляющего сигнала, синхроимпульсов и сигнала переключения режима, соединенные соответствен- мо с выходами широтно-импульсного модулятора, задающего генератора синхроимпульсов и формирователя сигнала переключения режима, выход широтно- импульсного сигнала, соединенный с соответствующими входами формирователей сигналов включения силовых и шунтирующего ключей, выход импульсов синхронизации, соединенный с тактовым входом модулятора и с первым тактовым входом демультиплексора формирователя сигналов включения силовых ключей, два вьгхода задержанных сигналов переключения режима, первый из которых соединен с вторым тактовым входом этого же демультиплексора, а второй - с выходом задержанного сигнала формирователя распределительных сигналов, и выход сигнала запрета, соединенный с входом запрета формирователя распределительных сигналов, причем совместитель импульсных сигналов включает в себя трехсекцион- ный элемент задержки сигнала переключения режима, вход которого образует вход сигнала переключения режима совместителя, а выходы первой и второй секций - два выхода задержанных сигналов переключения , вход которого образует вход сигналу переключения режима совместителя, а выходы первой и второй секций - два выхода задержанных сигналов переключения режима совместителя, трехсекцион- ный элемент задержки синхроимпульсов, вход которого образует вход синхроимпульсов совместителя, а вы- - ход первой секции - вьтход импульсов синхронизации совместителя, формирователь временных интервалов запрета, состоящий из трех RS-триггеров, S- и R-входы первого из которых соединены соответственно с входом синхроимпульсов совместителя и с выходом второй секции элемента задержки синхроимпульсов, S- и R-входы второго из которых соединены соответственно с

выходами второй н третьем секции этго же элемента задержки, формирователь управляемых временнйх интервалов запрета, состоящий из узла задержки, содержащего синхронный D- триггер и RS-триггер, S- и R-входы которого соединены соответственно с входом сигнала переключения режима совместителя и вьпсодом третьей секции элемента задержки сигнала переключения режима, а выход которого соединен с входом синхронизации D- триггера, и из двух RS-триггеров, S-вход первого из которых связан с выходом второго RS-триггера формирователя временных интервалов запрета и выходом второй секции элемента задержки переключения режима через конъюктор, а R-вход соединен с выхо- дом третьей секции этого же элемента задержки, выход второго из этих HS- триггеров соединен с выходом сигнала запрета совместителя, его S-вход соединен с входом сигнала переключения режима совместителя, а на его R-входе сформирован логический сигнал а-Ь .с + d, где а,. Ь, с, d - сигналы на вькоде D-триггера, выходе второго RS-триггера формирователя временных интервалов запрета, на выходах второй и третьей секций элемента задержки сигнала переключения режима соответственно, два каскадно включенных ограничителя временных интервалов, состоящие каждый из двух синхронных D-триггеров, соединенных по схеме двухразрядного сдвигающего регистра с двумя.раздельными такто- выми входами так, что вход синхронизации каждого из триггеров представляет отдельный тактовый вход ограничителя временных интервалов, а сигнальный вход первого из ограничителей служит входом широтно-импульсно- го управляющего сигнала, а выход второго из них - выходом широтно-импуль сного сигнала совместителя, выход первого из ограничителей соединен с сигнальным входом второго ограничителя и сигнальным входом Ь-триггера узла задержки формирователя управляемых временных интервалов запрета, первый и второй тактовые входы первого ограничителя соединены соответ

10

5

5

0 0

0

5

0

5

стренно с выходамн третьего и первого RS-триггеров формз-грователя временных интервалов запрета, а первьш и вторсл тактовые входы второго ограничителя временных интервало в - с выходами первого и второго RS-триггеров формирователя управляемых интервалов запрета, при этом демульти- ялексор формирователя сигналов вклкг- чения силовых ключей выполнен с двумя тактовыми входам, первый из которых включен на выход импульсов синхронизации, а второй - на первый выход задержанных сигналов переключения режима совместителя, причем сигнал с информационного входа проходит на выход демультиплексора, управУ1Яющего силовым ключом первой сети, если на адресные входы А или F поступают к о- манды режима работы включения сети А или переключения от сети В к сети А, сигнал с информационного входа проходит на выход демультиплексора, управляющего силовым ключом второй сети, если на адресные входы С или Е поступают команды режима работы включения сети В или переключения от сети А к сети В, при этом фронт сигнала на первом тактовом входе определяет прохождение сигнала на выходы с адресных входов Аи С, а фронт сигнала на втором тактовом входе - с адресных входов Е и F, команды отключение от сети А или отключение от сети В, поступающие на адресные входы В или D блокируют прохождение сигнала с информационного входа на выходы демультиплексора, а формирователь сигналов коммутации дополнен входом запрета, соединенным с выходом сигнала запрета совместителя импульсных сигналов, и снабжен дополнительным выходом, соединенным с прямым входом формирователя сигнала включения шунтирующего ключа, дополнительным дизъюнктором и элементом запрета, через которые входы формирователя сигналов коммутации связаны с его дополнительным выходом, причем- на этом выходе сформирован логический сигнал, равный конъюнкции инверсии сигнала на входе запрета и дизъюнкции сигналов на сигнальных входах.

Фм. 1

IfffftaA s

Ufft/rB

ирткА

ирткВ

UnepAd

и пер 6 А

гй&;

Фиг.З

.

Фаг. 5

Фи.б

П

п

CL

% Wf/

% 3.} {3} Us

ii

Р(/г. /2

Wet

y

(/3(«) ) У5

Чз(«}

%/e)

l/ff(S)

(« «

аг/3

15 „

r

L

I

%f-J «У

y«

4

u U.«-J

ay

UM M/J /

И}«

«у

и

-Я

{}I-J

«

JTL

Г1

J3

tz

eiHA(B)

)

temxafA)

r.iM

-v

«PaiMt

| Источник бесперебойного электропитания | 1977 |

|

SU624338A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Источник бесперебойного электропитания | 1972 |

|

SU522536A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1989-07-23—Публикация

1987-10-22—Подача