Изобретение относится к вычислительной технике, а именно к энергонезависимым оперативным запоминающим устройствам, и может быть использовано для управления К/МОП статическими ОЗУ.

Цель изобретения - увеличение срока службы ячейки памяти.

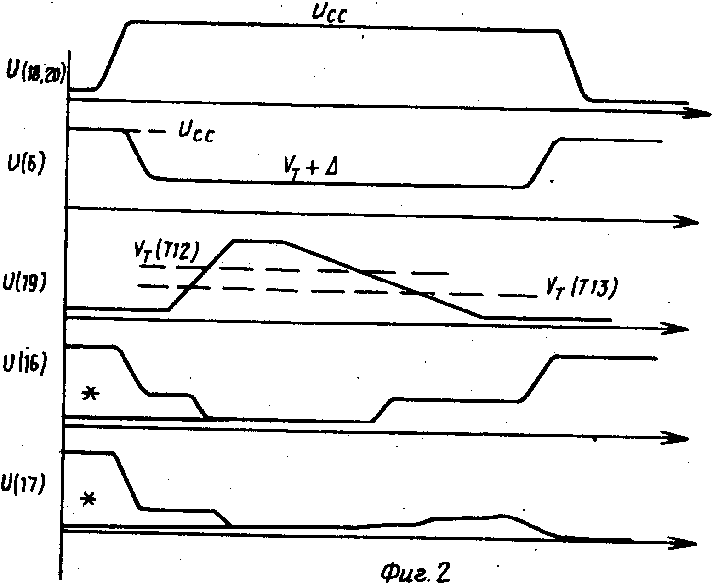

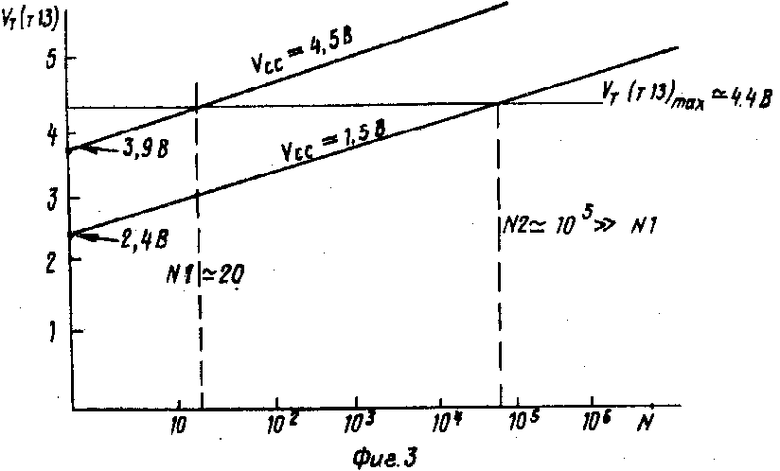

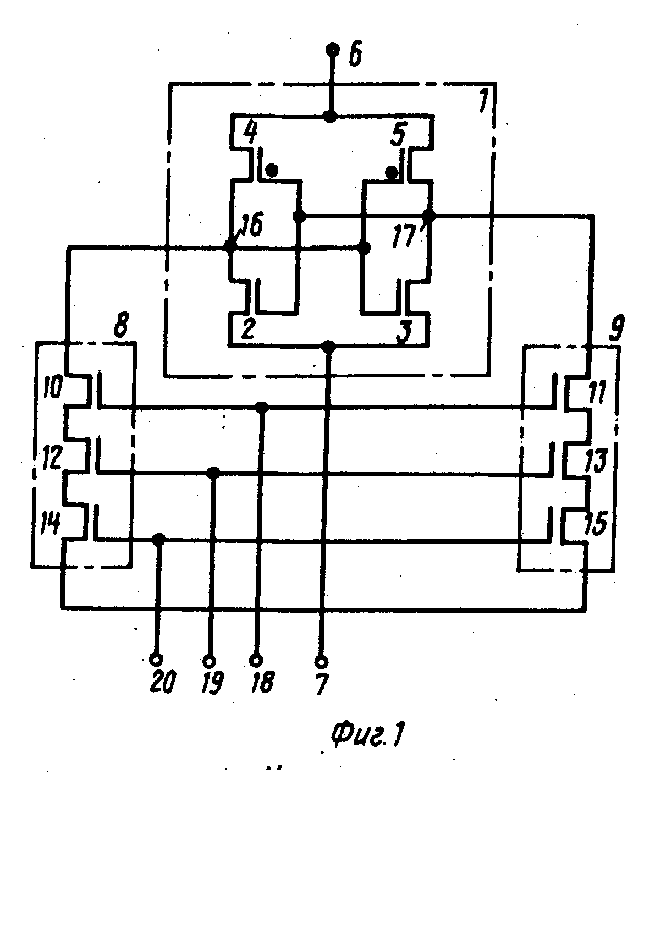

На фиг. 1 приведена электрическая схема ячейки памяти, управляемой с помощью предлагаемого способа; на фиг. 2 - временные диаграммы сигналов управления и потенциалов входов-выходов триггера; на фиг. 3 - зависимость эффективного порога включения запоминающего транзистора от количества циклов его программирования при различных величинах напряжения на входе питания.

Ячейка памяти содержит триггер 1 с перекрестными связями, образованный двумя вентильными транзисторами 2, 3, двумя нагрузочными транзисторами 4, 5 и имеющий шины напряжения питания 6 и нулевого потенциала 7, два элемента энергозависимого хранения 8, 9, образованные последовательно соединенными в указанном порядке коммутирующими 10, 11, запоминающими с изменяемым порогом включения 12, 13 и ключевыми 14, 15 транзисторами, причем каждый из элементов 8, 9 стоком коммутирующего транзистора подключен к одному из входов-выходов 16, 17 триггера, а истоком ключевого транзистора - к входу 7 нулевого потенциала, затворы коммутирующих, запоминающих и ключевых транзисторов являются соответственно входами коммутации 18, программирования 19 и стирания 20.

Пусть перед включением питания содержащаяся в триггере информация была скопирована в запоминающие транзисторы 12, 14. В результате этого пороговое напряжение транзистора 12 стало, например, 2,4 В, а транзистора 13 2,7 В. В первый момент после включения питания триггер установился в произвольное состояние, определяемое технологической и топологической асимметрией триггера. Для восстановления исходной информации в триггере сначала на входы 18 и 20 подают напряжение, равное, например, напряжению питания 4,5 В, открывая тем самым транзисторы 10, 11, 14, 15 (фиг. 2). Затем напряжение питания уменьшают до значения, меньшего номинального напряжения питания, но большего минимального напряжения хранения информации ячейки памяти, например до 1,5 В, после чего подают напряжение 4,5 В на вход 19. Так как в результате снижения напряжения на входе 6 максимальный ток нагрузочных транзисторов не превысит 4,9 мкА, это приведет к практически полному обнулению входов-выходов 16, 17 триггера. При уменьшении напряжения на входе 19 первым закроется запоминающий транзистор 12 с более высоким порогом, потенциал точки 16 начнет нарастать раньше, чем точки 17, что и приведет к установке триггера в состояние, задаваемое знаком разности пороговых напряжений транзисторов 12, 13. При такой величине напряжения на входе 6 и при наихудшей величине напряжения на входе 19, равной 4,5 В, ячейка сохранит работоспособность. Учитывая, что порог транзисторов 12, 13 растет от уровня примерно 2,4 В с темпом 0,4 В на одну декаду количества циклов перепрограммирования, получаем, что при данном способе восстановления информации количество циклов перепрограммирования ячейки памяти достигнет 100000. После снятия напряжения с входа 19 напряжение на входе 6 увеличивают до номинального значения, например 4,5 В, что обеспечивает нормальную работу ячейки памяти при записи/считывании информации из триггера и при программмировании запоминающих транзисторов.

При других значениях напряжения на входе 6 из указанного диапазона его изменения будут достигнуты промежуточные значения числа циклов программирования (фиг. 3). Уменьшать его до значений, меньших порогов включения транзисторов триггера нельзя, так как это не позволит устанавливать и фиксировать состояние триггера.

Способ может быть применен к любой другой ячейке памяти, где требуется закорачивание сильноточных нагрузок через транзистор, пороговое напряжение которого в процессе работы может меняться в широких пределах.

Использование способа наиболее эффективно в ячейках памяти на основе комплементарных структур, так как предложенное в нем техническое решение проблемы ограничения количества циклов перепрограммирования позволяет использовать в приборах памяти такие присущие им свойства, как высокая помехозащищенность и экономичность.

Использование предлагаемого способа управления ячейкой памяти обеспечивает расширение рабочего диапазона порогов включения запоминающих транзисторов в ячейке памяти, что позволяет разработать конструкцию экономического и помехоустойчивого энергонезависимого К/МОП ОЗУ с числом циклов программирования не менее 10000 и повышение выхода годных за счет меньшей зависимости характеристик ячейки памяти от технологического разброса порогов запоминающих транзисторов. (56) Авторское свидетельство СССР N 1308063, кл. G 11 C 11/40, 1986.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ПАМЯТИ | 1985 |

|

RU1318096C |

| ЯЧЕЙКА ПАМЯТИ | 1985 |

|

RU1308063C |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ НА МДП-ТРАНЗИСТОРАХ С ИЗМЕНЯЕМЫМ ПОРОГОВЫМ ВКЛЮЧЕНИЕМ | 1985 |

|

RU1378681C |

| ЭЛЕМЕНТ ПАМЯТИ | 1984 |

|

RU1253350C |

| СПОСОБ ОПРЕДЕЛЕНИЯ НАПРЯЖЕНИЯ ПРОГРАММИРОВАНИЯ ЯЧЕЙКИ ПАМЯТИ НА ОСНОВЕ ПНОП-СТРУКТУРЫ | 1988 |

|

RU1582834C |

| СПОСОБ ВОССТАНОВЛЕНИЯ РЕПРОГРАММИРУЕМЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1988 |

|

RU1604053C |

| СОСТАВНОЙ МДП-ТРАНЗИСТОР | 1987 |

|

SU1501803A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО И СПОСОБ УПРАВЛЕНИЯ ИМ | 1979 |

|

RU1110315C |

| СПОСОБ УМЕНЬШЕНИЯ ДЕФЕКТНОСТИ ДВУХСЛОЙНОГО ДИЭЛЕКТРИКА В СТРУКТУРЕ ПРОВОДНИК - НИТРИД КРЕМНИЯ - ОКИСЕЛ КРЕМНИЯ - ПОЛУПРОВОДНИК | 1983 |

|

SU1108962A1 |

| Способ перепрограммирования ячейки памяти на МНОП-транзисторе | 1985 |

|

SU1437918A1 |

Изобретение относится к вычислительной технике. Цель изобретения - увеличение срока службы ячейки памяти. Поставленная цель достигается тем, что перед подачей напряжения на вход программирования ячейки памяти величину напряжения питания уменьшают до значения, меньшего номинального значения напряжения питания, но большего минимального напряжения хранения информации в ячейке памяти, а после снятия напряжения со входа программирования ячейки памяти, напряжение питания восстанавливают до номинального значения. 3 ил.

СПОСОБ ВОССТАНОВЛЕНИЯ ИНФОРМАЦИИ В ЯЧЕЙКЕ ПАМЯТИ, заключающийся в подаче напряжения на входы коммутации, программировании и стирании информации с последующим уменьшением напряжения на входе программирования, отличающийся тем, что, с целью увеличения срока службы ячейки памяти, перед подачей напряжения на вход программирования ячейки памяти, величину напряжения питания уменьшают до значения, меньшего номинального напряжения питания, но большего минимального напряжения хранения информации в ячейке памяти, а после снятия напряжения со входа программирования ячейки памяти напряжение питания восстанавливают до номинального значения.

Авторы

Даты

1994-02-15—Публикация

1987-09-03—Подача