1

(21)4335061/24-09

(22)09.10.87

(46) 23.08.89. Бюл. № 31 (72) Ю.Н.Юркин

(53)621.395.664 (088.8)

(56) Авторское свидетельство СССР 1040613, кл. Н 04 В.3/46, 1982.

Авторское свидетельство СССР 951742, кл. Н 04 L 11/08, 1981.

(54)УСТРОЙСТВО ПРЕДСКАЗАНИЯ ОЦЕНКИ КАЧЕСТВА КАНАЛА СВЯЗИ

457) Изобретение относится к радиотехнике, и позволяет сократить время

предсказания оценки качества канала связи. Устройство содержит счетчик 1 ошибок, формирователь 2 циклов отсчета, элементы ИЛИ 3 и 9, регистр 4 сдвига, сумматор 5 по модулю два, элементы И 6 и 7, элемент ИЛИ-НЕ 8, блок 10 определения приращений час- тости ошибок и индикатор 11. Благодаря введению в устройство элемента ИЛИ 9 и блока 10 определения обеспечивается определение тенденции к нарастанию частости ошибок. 2 з.п. ф-лы, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля состояния канала связи | 1982 |

|

SU1040613A1 |

| Устройство для предсказания состояния дискретного канала связи | 1980 |

|

SU951741A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2450343C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2449350C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2459241C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2455682C1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2012 |

|

RU2517316C1 |

| Устройство для контроля ошибок аппаратуры многоканальной магнитной записи | 1988 |

|

SU1580438A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2013 |

|

RU2515215C1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ДИФФЕРЕНЦИРУЮЩЕЕ И ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2535467C1 |

Изобретение относится к радиотехнике и позволяет сократить время предсказания оценки качества канала связи. Устройство содержит счетчик 1 ошибок, формирователь 2 циклов отсчета, элементы ИЛИ 3 и 9, регистр 4 сдвига, сумматор 5 по модулю два, элементы И 6 и 7, элемент ИЛИ-НЕ 8, блок 10 определения приращений частости ошибок и индикатор 11. Благодаря введению, в устройство элемента ИЛИ 9 и блока 10 определения обеспечивается определение тенденции к нарастанию частости ошибок. 2 з.п. ф-лы, 3 ил.

§

(Л

СП

со

О

vj

фиаЛ

31503

И зобретение относится к радиотехнике и может использоваться для автоматического предсказания оценки качества дискретного канала связи.

Цель изобретения - сокращение времени предсказания оценки качества канала св язи за счет определения тенденции к нарастанию частости ошибок.

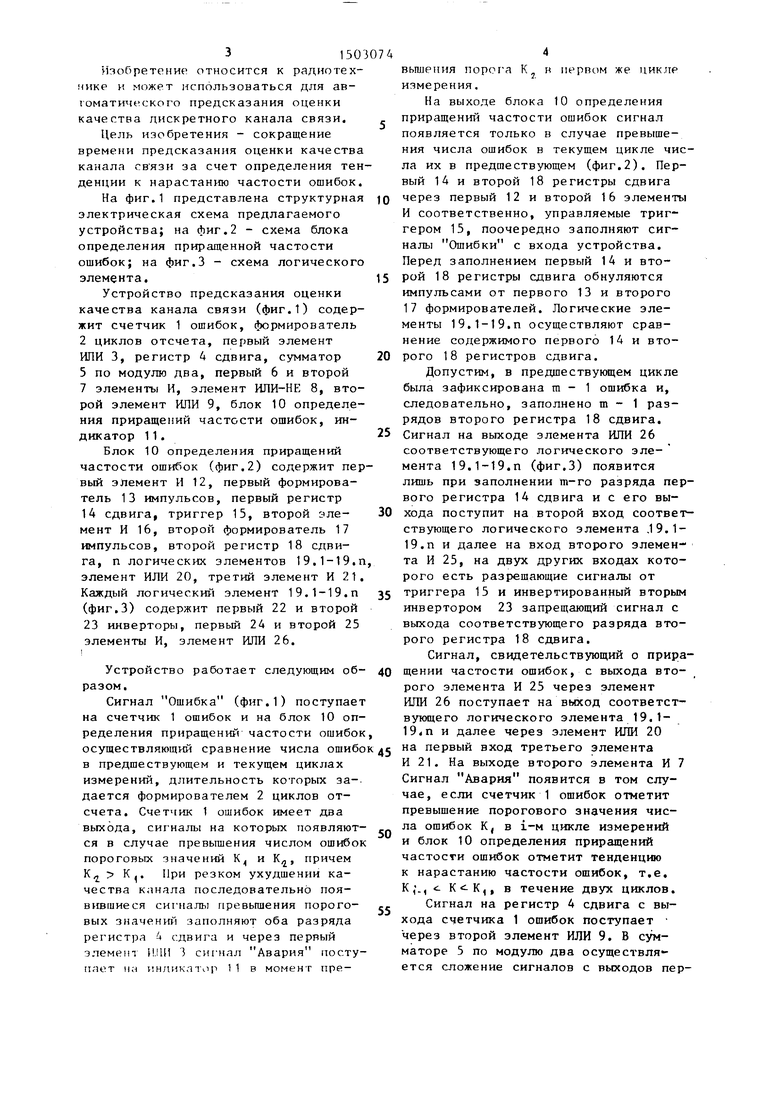

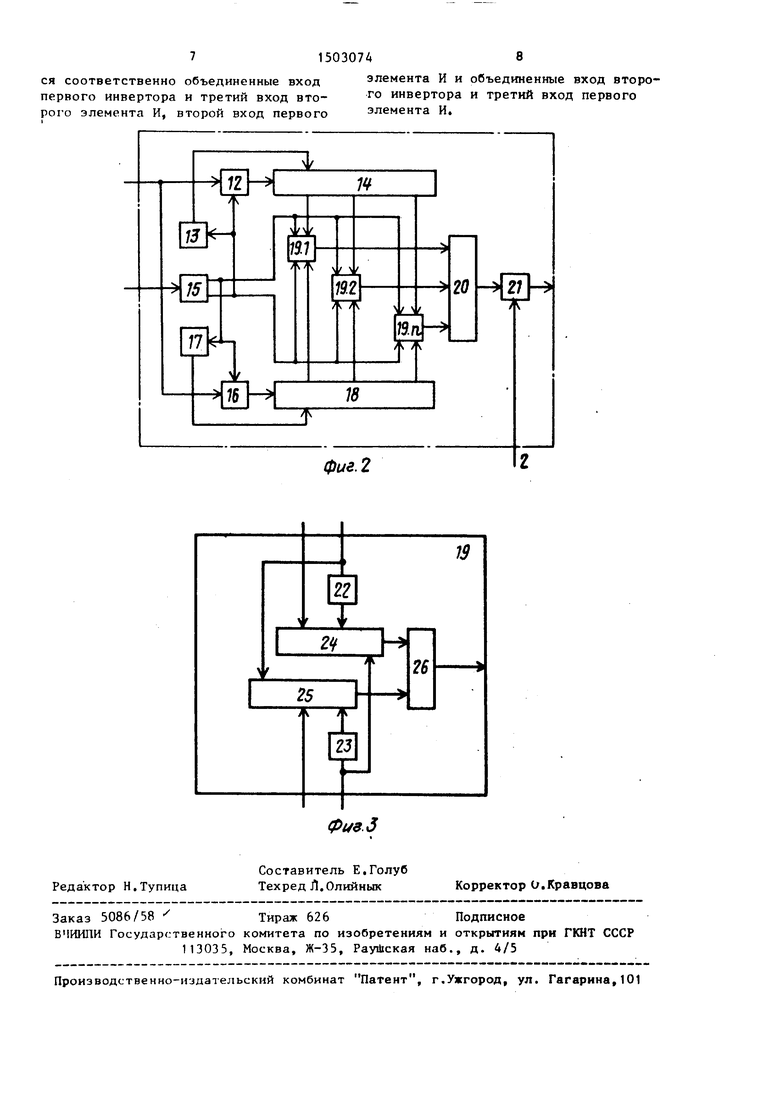

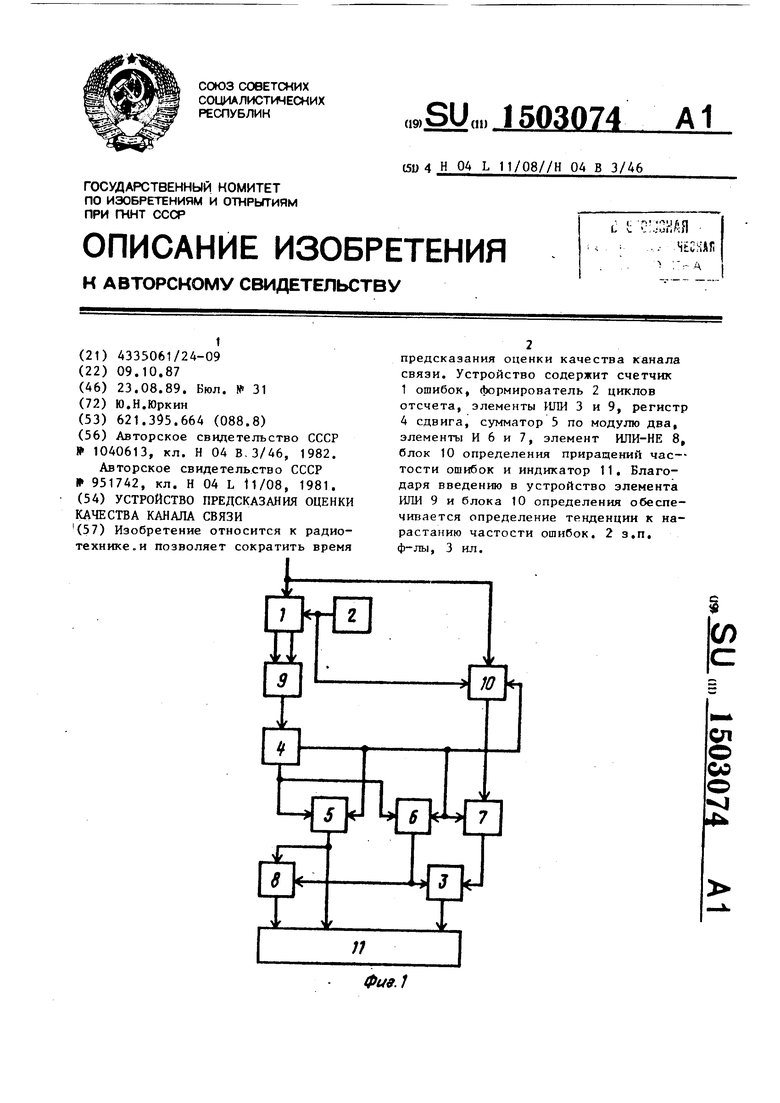

На фиг.1 представлена структурная электрическая схема предлагаемого устройства; на фиг.2 - схема блока определения приращенной частости ошибок; на фиг.З - схема логического элемента.

Устройство предсказания оценки качества канала связи (фиг.1) содержит счетчик 1 ошибок, формирователь 2 циклов отсчета, первый элемент ИЛИ 3, регистр 4 сдвига, сумматор

5 по модулю два, первый 6 и второй 7 элементы И, элемент ИЛИ-НЕ 8, второй элемент ИЛИ 9, блок 10 определения приращений частости ошибок, индикатор 11.

Блок 10 определения приращений частости ошибок (фиг.2) содержит первый элемент И 12, первый формирователь 13 импульсов, первый регистр 14 сдвига, триггер 15, второй эле- мент И 16, второй формирователь 17 импульсов, второй регистр 18 сдвига, п логических элементов 19.1-19.п элемент ИЛИ 20, третий элемент И 21. Каждый логический элемент 19.1-19.П (фиг.З) содержит первый 22 и второй 23 инверторы, первый 24 и второй 25

элементы И, элемент ИЛИ 26.

1

Устройство работает следующим об- разом.

Сигнал Ошибка (фиг.1) поступает на счетчик 1 ошибок и на блок 10 определения приращений частости ошибок осуществляющий сравнение числа ошибо в предшествующем и текущем циклах измерений, длительность которых за-. дается формирователем 2 циклов отсчета. Счетчик 1 ошибок имеет два выхода, сигналы на которых тгаявляют- ся в случае превышения числом ошибок пороговых значений К и К, причем К К.. При резком ухудшении качества канала последовательно поя- В1шшиеся сигналы превьш1ения порого- вых значений заполняют оба разряда регистра 4 сдвига и через первый элемент ll.ilil 3 сигнал Авария поступает на индикатор 11 в момент пре-

вьш1ения порога К в нерпой же цикле измерения.

На выходе блока 10 определения приращений частости ошибок сигнал появляется только в случае превышения числа ошибок в текущем цикле числа их в предшествующем (фиг.2). Первый 14 и второй 18 регистры сдвига через первый 12 и второй 16 элементы И соответственно, управляемые триггером 15, поочередно заполняют сигналы Ошибки с входа устройства. Перед заполнением первый 14 и второй 18 регистры сдвига обнуляются импульсами от первого 13 и второго 17 формирователей. Логические элементы 19.1-19.П осуществляют сравнение содержимого первого 14 и второго 18 регистров сдвига.

Допустим, в предшествующем цикле была зафиксирована та - 1 ошибка и, следовательно, заполнено m - 1 разрядов второго регистра 18 сдвига. Сигнал на выходе элемента ИЛИ 26 соответствующего логического эле- мента 19.1-19.п (фиг.З) появится лишь при заполнении ш-го разряда первого регистра 14 сдвига и с его выхода поступит на второй вход соответствующего логического элемента ,19.1- 19.П и далее на вход вторю го элемента И 25, на двух других входах которого есть разрешающие сигналы от триггера 15 и инвертированный вторым инвертором 23 запрещающий сигнал с выхода соответствующего разряда второго регистра 18 сдвига.

Сигнал, свидетельствующий о приращении частости ошибок, с выхода второго элемента И 25 через элемент ИЛИ 26 поступает на выход соответствующего логического элемента 19.1- 19.П и далее через элемент ИЖ 20 на первый вход третьего элемента И 21. На выходе второго элемента И 7 Сигнал Авария появится в том случае, если счетчик 1 ошибок отметит превышение порогового значения числа ошибок К, в i-M цикле измерений и блок 10 определения приращений частости ошибок отметит тенденцию к нарастанию частости ошибок, т.е. К;., 1 ,, в течение двух циклов.

Сигнал на регистр 4 сдвига с выхода счетчика 1 ошибок поступает через второй элемент ИЛИ 9. В сумматоре 5 по модулю два осуществляется сложение сигналов с выходов перnoj о и BToporvi разрядил iioniryrpa сдвига, которые также черед первый элемент И 6 подаются Fia входы первого элемента ИЛИ 3 и элемента ИЛН- НЕ 8. На первый, второй и третий вхды индикатора 11 подаются соответственно сигналы с выходов первого элемента ИЛИ 3, элемер1та 1ШИ-НЕ 8 и сумматора модулю два.

По второму и третьему входам в логические элементы 19.1-19,п поступают сигналы на входы первого инвертор 22 и первого элемента И 24, с выходов которых сигналы подаются на входы элемента ИЛИ 26.

Формула изобретени

счета, выходом первого разряда регистра сдвига и вторым входом счетчика ошибок, а выход блока определения приращенш частости ошибок подключен к второму входу второго элемента И.

5 соединены с соответствующими вхоДами элемента ИЛИ, выход которого подключен к первому входу третьего элемента И, первый выход триггера соединен с входом первого формирователя импуль0 сов, первым входом первого элемента И и первыми входами всех п логических элементов, вторые входы которых с соответствующими выходами первого регистра сдвига, вход и вход Сброс

5 которого соединены соответственно с выходом первого элемента И и с выходом первого формирователя им- . пульсов, второй выход триггера соединен с входом второго формирователя

0 импульсов, с первым входом второго элемента И и с третьими входами всех п логических элементов, четвертые входы которых соединены с соответствующими выходами второго регистра

, сдвига, вход и вход Сброс которого соединены соответственно с выходом второго элемента И и с выходом второго формирователя импульсов, вход триггера является первым входом бло0 ка определения приращений частости ошибок, вторым и третьим входами и выходом которого являются соответственно второй вход третьего элемента И, объединенные вторые входы перс вого и второго элементов И и выход третьего элемента И.

го элемента, первым входом которого . является второй вхол второго элемента И, а вторым, третьим и четверп тм входами логического элемента являют715030748

ся соответственно объединенные вход элемента И и объединенные вход второ- первого инвертора и третий вход вто- ° инвертора и третий вход первого рого элемента И, второй вход первого элемента И.

фие.2

Авторы

Даты

1989-08-23—Публикация

1987-10-09—Подача