fpi/.f

Изобретение относится к радиотехнике и может использоваться для формирования однополосного сигнала в различных радиотехнических устройст- вах.

Цель изобретения - увеличение подавления нежелательной боковой полосы частот.

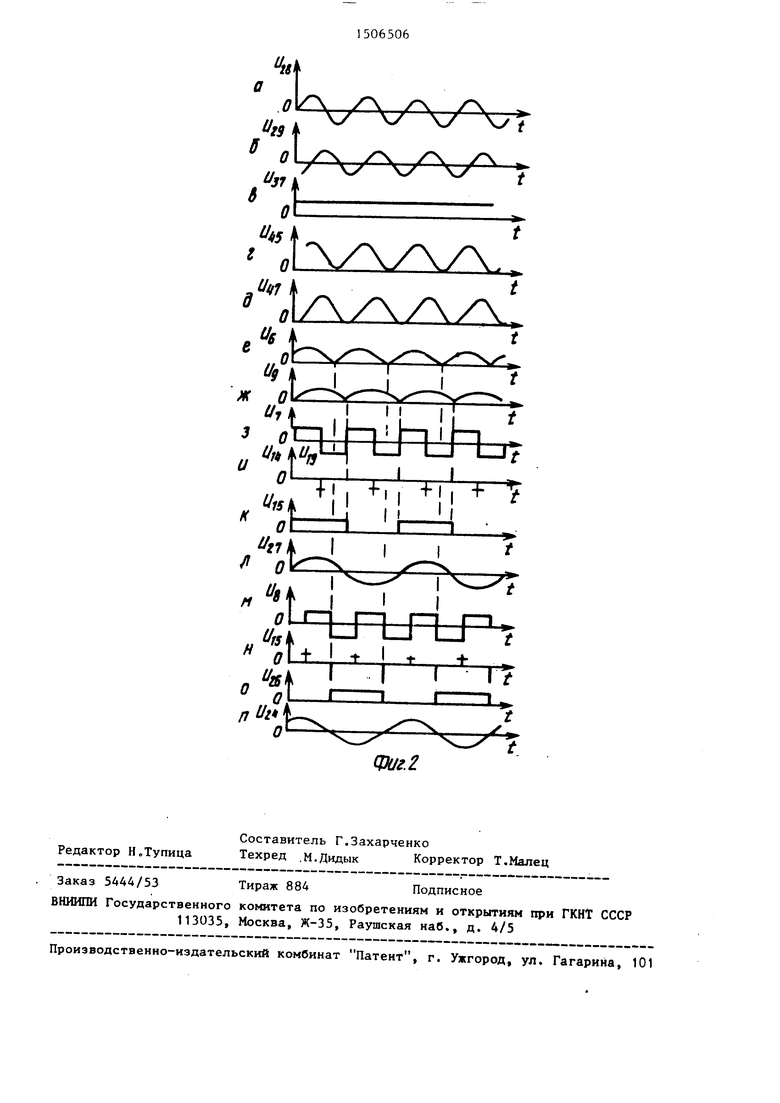

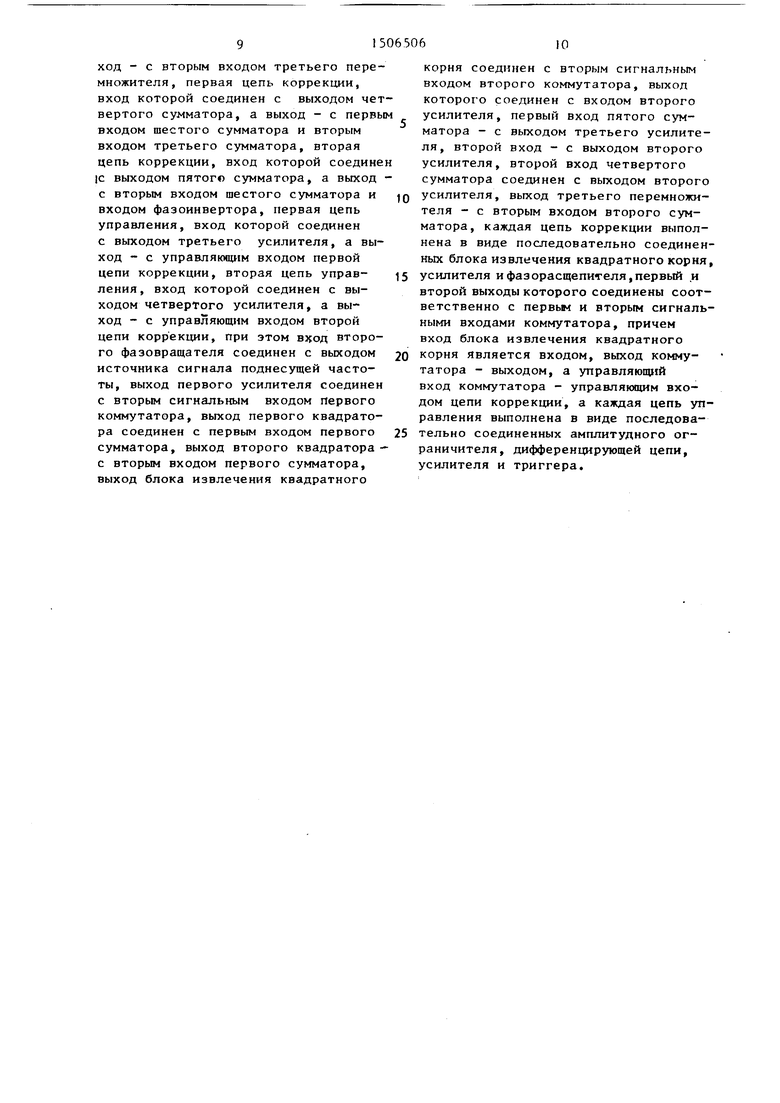

На фиг. 1 представлена структур- ная электрическая схема формирователя однополосного сигнала на фиг.2 - временные диаграммы работы формирователя .

Формирователь однополосного сиг- нала содержит источник 1 модулирующего сигнала, первый пёремнояситель 2, источник 3 сигнала поднесущей частоты, полосовой фильтр 4, второй фазовращатель 5, первую цепь 6 коррек- ции, первую цепь 7 управления, детектор 8 огибающей, первый усилитель 9, делитель 10 напряжений,, вторую цепь 11 коррекции, вторую цепь 12 управления, первый коммутатор 13, шестой сумматор 14. фазоинвертор 15j первый 16 и второй 17 когерентные детекторы, первый 18 и второй 19 квадраторы, первый сумматор 20, второй коммутатор 21, блок 22 извлечения квадратного корня, третий усилитель 23, второй усилитель 24, четвертый сумматор 25, четвертый усилитель 26, первый регулятор 27 уровня, третий сумматор 28, второй регулятор 29 уровня, второй перемножитель 30, источник 31 модулируемого сигнала, первый фазовращатель 32, третий перемножитель 33, второй сумматор 34, пятый сумматор 35.

Первая 6 и вторая 11 цепи коррекции содержат блок 36 извлечения квадратного корня, усилитель 37, фазо- расщепитель 38, коммутатор 39. Перва 7 и вторая 12 цепи управления содер- жат амплитудный ограничитель 40, дифференцирующую цепь 41, усилитель 42, триггер 43.

Формирователь однополосного сигнала работает следуюгцим образом.

МодулируюпХий сигнал U(t) V(t)cost/(t) от источника 1 модулирующего сигнала поступает, на низкочастотный первый вход перемножителя 2, на высокочастотный второй вход которого подается сигнал Uj(t) V-Coswt от источника 3 сигнала поднесущей частоты. На выходе перемножителя 2 образуется колебание

5

с

5 0 0 5 40

5

гп

U(t) U,(t)U.,(t) V(t)cosq (t) ;«V3COSujt 0,5V3V(t)cos(i + tf(t) + -I- 0,5V,jV (t)cos(aJC - ). Полосовой фильтр 4 вьзделяет одну боковую полосу, например, верхнюю ) 0,3V3V(t)cos(u;t + c/(t). После усиления в усилителе 9 сигнал U(t) Поступает на входы коммутатора 13, делителя 10 напряжений, детектора 8 вгибающей. С выхода коммутатора 13 сигнал поступает на входы когерентных детекторов 16 и 17. От источника 3 подается колебание Uj(t) на второй (опорный) вход когерентного детектора 16 непосредственно, а на второй вход (опорный) когерентного детектора 1 7 - через фазовращатель 5 на 90. В них перемножаются между собой сигналы и (t)rU ,j(t)- U3(t) V,3V(t)t . 4cos(wt + cft)) Vjcoscot 0,5УзУ,з V(t) costXt) -t- 0,5V3V,j V(t) cos(2u;t + 4(t)); U ,7(t) и ,j(t)-U(t) V ,j V(t)cos (ii;t + Cf(t)) VjCosCwt + + 90°) 0,5VjV,j V(t)cos(c/t) - ) + + 0,5V5V,j V(t)cos(2(ot + 4(t) + 90), a их фильтры нижних частот выделяют только низкочастотные составляющие (t) 0,5УэУ ,3V(t))i и ,,(t) 0,(t)cos(cft) - 90). При этом устанавливается УЗ Vj. После возведения их в квадрат соответственно в квадраторах 18 и 19 (фиг. 2а,б) они суммируются в сумматоре 20

U,o(t) U,4(t) + U,g(t) (t) +

+ U(t) 0,25V3V,v (t)(cos cf(

+ sinV(t)) - Vio-V (t). После этого из огибающей в квадрате V(t)V извлекается квадратный корень в блоке 22. С выхода блока 22 извлечения квадратного корня сигнал (фиг. 2в) поступает на один из сигнальных входов коммутатора 21. Цепь из когерентных детекторов 16 и 17, квадраторов 18 и 19, сумматора 20 и блока 31, представляющая собой детектор огибающей, используется при малом эффективном значении однополосного сигнала, полученного после усилителя 9.

В случае больщого эффективного значения этого сигнала для выделения огибающей используется детектор 8 огибающей, который может быть выполнен известным способом - на диоде и т.д. Коммутатор 21 переключается при этом в соответствующее положение

извне. Сигнал с выхода детектора 8 огибающей U,,(t) KV(t) поступает на другой вход коммутатора 21. С выхода коммутатора 21 сигнал Ue(t) или

о

Uj,{t) через усилитель 24 поступает на входы сумматоров 25 и 35 и на вход делителя 10 напряжений. На выходе делителя 10 получается колебание постоянного уровня

U,o(t)

Us(t) U,4(t)

0,5V3V(t)cos(cot + M Ct) KV(t)

K,cos(6Jt + qi(t);; K,

Ha другой вход сумматора 25 подается колебание с выхода когерентного детектора 16 через усилитель 26, а на другой вход сумматора 35 - с . выхода когерентного детектора 17 через усилитель 23. На выходе сумматоров 25 и 35 (фиг. 2г, д) получаются

и ,(t)

KV(t)

+ U24(t) 2KV(t)

1} ,,(t) + U,(t)

KV(t)cos(tXt) - 90) 4. KV(t)) ,i

Из этих сигналов

, 45)

в блоках 36 и 22 извлекаются корни квадратные, отчего на их выходах имеют место колебания (фиг. 2е, ж)

U,(,,(t) V2KV(t)/cos /; U,,,(t

- V2KV(t)/cos( - )/.

Структура этих сигналов такая же, как и на выходе двухполупериодных выпрямителей с активной нагрузкой, что отмечено вертикальными линиями, охватывающими косинус, означающими у одуль. По этим однополярным сигна- ,лам необходимо восстановить двух- полярные, соответствующие модулирующему сигналу в цепях 6 и 11 коррекции. Сигнал с вькода блока 36 каждой ,из цепей 6 и 11 усиливается усилителем 37 и в фазорасщепителе 38 преобразуется в два сигнала, сдвинутые между собой по фазе на 180, которые поступают на первый и второй сигнальные входы коммутатора 39. На управ- ляюгций вход коммутатора 39 цепи подается сигнал (t) через цепь 7 управ6506

пения

10

а на управляющий вход коммутатора цепи 11 - сигнал Uji(t) через такую же цепь 12 управления. Триггеры 43 цепей 7 и 12 управления работают от импульсов, сформированных из напряжений Uj(t) и и,7 (t), которые находятся между собой в квадратуре для обеспечения требуемой коррекции. Колебания с выходов триггеров 43 цепей 7 и 12 (фиг. 2к, о) управляют работой коммутаторов 39 так, что на их выходах имеют место скорректированные знакопеременные сигналы

Ujga (t 3901)) - 45).

/ ШОсоз ; /2Kv7ocos(- Эти сигналы сдвинуты по фазе друг относительно друга на 45°. В сумматоре 14 сигналы с коммутаторов 39 склады- ваются

UnCt) Uj,, (t) + U3t(,ii (t) - /Ii)fcos.coe( 45°) 2/2KV(t) cos22,5° .cos(- - 22,5°) - Vijhv(t)- ,

.cos( 22,5), .,

..

где 2VK cos22,5, a в сумматоре 28 вычитаются

40

Uu(t

45

50

55

39 (п (t) - U,,(,,,(t) - i( cos - co8.( - 45°) -2-/2KV(O 81022,5° sin( - 22,5) « KjV2V(t)

«sin( 22,5); К j -2VKsin22,,

в результате чего сигналы оказываются сдвинутыми между собой по фазе на 90.

В цепях 7 и 12 управления перед, подачей на триггер 43 производится амплитудное ограничение входных сигналов в амплитудном ограничителе 40 (фиг. 2з, м), дифференцирование в

дифференцирующей цепи 41 (фиг. 2и, н) и усиление до необходимого уровня в усилителе А2. Сигналы с выходов коммутаторов 39 соответственно цепей 7 и 12 показаны на фиг. 2л, п.

В регуляторах 27 и 29 уровня выравниваются уровни выходных сигналов сумматоров 14 и 28 (К J К., К). которые затем поступают на низкочастот- ные входы перемножителей 30 и 33. С выхода источника 31 модулируемого сигнала колебание рабочей несущей частоты Uj, (t) VjjCosWjt подается на высокочастотн ый вход перемножите- ля 30 непосредственно, а на высокочастотный вход перемножителя 33 че-- рез фазовращатель 32 на 90°.

На выходе перемножителя 30 и 33 образуются сигналы

изо (t) U,(t).U3,(t) - /mOcosC- l - 22,5).

t 0,5Vjy2V(t) cos(w,t-

22,5) + cosCco t +

22.5),

U,.,(t)V,,(t)

/2V(t)

,cos(- - 90° - 22,5°)x

«V,, cos(u)ot + 90)

0,5V /2V(t) co3(tujt - +

+ 22,5 ) - cos(a)jt + - - 22,5) .

(t)

В сумматоре 34 эти сигналы складываются ) Ujo(t) + UasCt). при этом образуется нижняя боковая полоса, которая в 2 раза меньше полосы частот модулирующего сигнала. ЕСЛИ же в блоке 34 эти сигналы вычитаются

один из другого ) UjoCt)

- u,,(t)

ээ

U,,,V2V(t)cos( 4+ - 22,5°), TO образуется верхняя боковая полоса, которая тоже в 2 раза меньше полосы частот модулирующего сигнала, с увеличенным подавлением другой, нежелательной боковой полосы частот.

5

0

5

0

5

0

5

0

5

Формула изобретения

Формирователь однополосного сигнала, содержащий последовательно соединенные источник модулирующего сигнала, первый перемножитель, полосовой фильтр и первый усилитель, последовательно соединенные первый сумматор и блок извлечения квадратного корня, последовательно соединенные источник модулируемого сигнала, второй перемножитель и второй сумматор, последовательно соединенные первый фазовращатель, вход которого соединен с вторым выходом источника модулируемого сигнала, и третий перемножитель, последовательно соединенные фазоин- вертор и третий сумматор, а также источник сигнала поднесущей частоты, выход которого соединен с вторым входом первого перемножителя, второй фазовращатель, первый и второй коммутаторы, первый и второй квадраторы, второй и третий усилители, четвертый, пятый и шестой сумматоры, отличающийся тем, что, с целью увеличения подавления нежелательной боковой полосы частот, в него введены детектор огибающей, вход которого соединен с первым выходом первого усилителя, а выход - с первым сигналь ным входом второго коммутатору, первый когерентнЕзш детектор, первый вход которого соединен с выходом первого коммутатора, второй вход - с выходом источника сигнала поднесущей частоты, а выход - с входом первого квадратора, второй когерентный детектор, первый вход которого соединен с выходом первого коммутатора, второй вход - с выходом второго фазовращателя, а вьпсод - с входами второго квадратора и третьего усилителя, делитель напряжений, первый вход которого соединен t третьим выходом первого усилителя, второй вход - с выходом второго усилителя, а выход - с первым сигнальным входом первого коммутатора, четвертый усилитель, вход которого соединен с выходом первого когерентного детектора, а выход - с первым входом четвертого сумматора, первый регулятор уровня, вход которого соединен с выходом шестого сумматора, а выход - с вторым входом второго перемножителя, второй регулятор уровня, вход которого соединен с выходом третьего сумматора, а выход - с вторым входом третьего перемножителя, первая цепь коррекции, вход которой соединен с выходом четвертого сумматора, а выход - с первы входом шестого сумматора и вторым входом третьего сумматора, вторая цепь коррекции, вход которой соедине |с выходом пятого сумматора, а выход с вторым входом шестого сумматора и входом фазоинвертора, первая цепь управления, вход которой соединен с выходом третьего усилителя, а выход - с управляющим входом первой цепи коррекции, вторая цепь управ- ления, вход которой соединен с выходом четвертого усилителя, а выход - с управляющим входом второй цепи коррекции, при этом вз{од второго фазовращателя соединен с выходом источника сигнала поднесущей частоты, выход первого усилителя соединен с вторым сигнальным входом Первого коммутатора, выход первого квадратора соединен с первым входом первого сумматора, выход второго квадратора - с вторым входом первого сумматора, выход блока извлечения квадратного

корня соединен с вторым сигнальным входом второго коммутатора, выход которого соединен с входом второго усилителя, первый вход пятого сумматора - с выходом третьего усилителя, второй вход - с выходом второго усилителя, второй вход четвертого сумматора соединен с выходом второго усилителя, выход третьего перемножителя - с вторым входом второго сумматора, каждая цепь коррекции выполнена в виде последовательно соединенных блока извлечения квадратного корня усилителя и фазорасщепителя,первый и второй выходы которого соединены соответственно с первым и вторым сигнальными входами коммутатора, причем вход блока извлечения квадратного корня является входом, выход коммутатора - выходом, а управляющий вход коммутатора - управляющим входом цепи коррекции, а каждая цепь управления выполнена в виде последовательно соединенных амплитудного ограничителя, дифференцирующей цепи, усилителя и триггера.

ы

/7U

Х r r

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь однополосного сигнала | 1988 |

|

SU1644358A1 |

| Формирователь однополосного сигнала | 1990 |

|

SU1753578A1 |

| Формирователь однополосного сигнала | 1985 |

|

SU1356183A1 |

| СПОСОБ ДЕЛЕНИЯ ПОЛОСЫ ЧАСТОТ ПЕРЕДАВАЕМОГО СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2004 |

|

RU2259632C1 |

| ФОРМИРОВАТЕЛЬ ОДНОПОЛОСНОГО СИГНАЛА ФАЗОВЫМ СПОСОБОМ | 2008 |

|

RU2363091C1 |

| ДЕЛИТЕЛЬ ПОЛОСЫ ЧАСТОТ РЕЧЕВОГО СИГНАЛА | 2010 |

|

RU2439795C1 |

| Формирователь однополосного сигнала | 1987 |

|

SU1450070A1 |

| ИНДИКАТОРНОЕ УСТРОЙСТВО | 1991 |

|

RU2005994C1 |

| Формирователь однополосного сигнала с угловой модуляцией | 1987 |

|

SU1494202A1 |

| ПАНОРАМНЫЙ ПРИЕМНИК | 1991 |

|

RU2010244C1 |

Изобретение относится к радиотехнике. Цель изобретения - увеличение подавления нежелательной боковой полосы частот. Цель достигается введением в устройство двух цепей коррекции 6 и 11, двух цепей управления 7 и 12, детектора огибающей 8, делителя 10 напряжений, двух когерентных детекторов 16, 17, усилителя 26, двух регуляторов 27, 29 уровня и их связей. Каждая цепь коррекции выполнена в виде последовательно соединенных блока 36 извлечения квадратного корня, усилителя 37 и фазорасщепителя 38. Каждая цепь управления выполнена в виде последовательно соединенных амплитудного ограничителя 40, дифференцирующей цепи 41, усилителя 42 и триггера 43. 2 ил.

%

r

y y T

/N /X W .V

X

7 I I It

3 gV-i I H IH

. РТЧЧ,// -I-11 - I

lU

I

I

zFhftP-

l

IT

vx

xx

IT

| Формирователь однополосного сигнала | 1985 |

|

SU1356183A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-09-07—Публикация

1987-02-10—Подача