СП

Од

10

Изобретение относится к радиотехике и может быть использовано в пребразователях частоты радиоприемных других устройств.

Цель изобретения - увеличение по- авления гетеродинного сигнала на выоде смесителя.

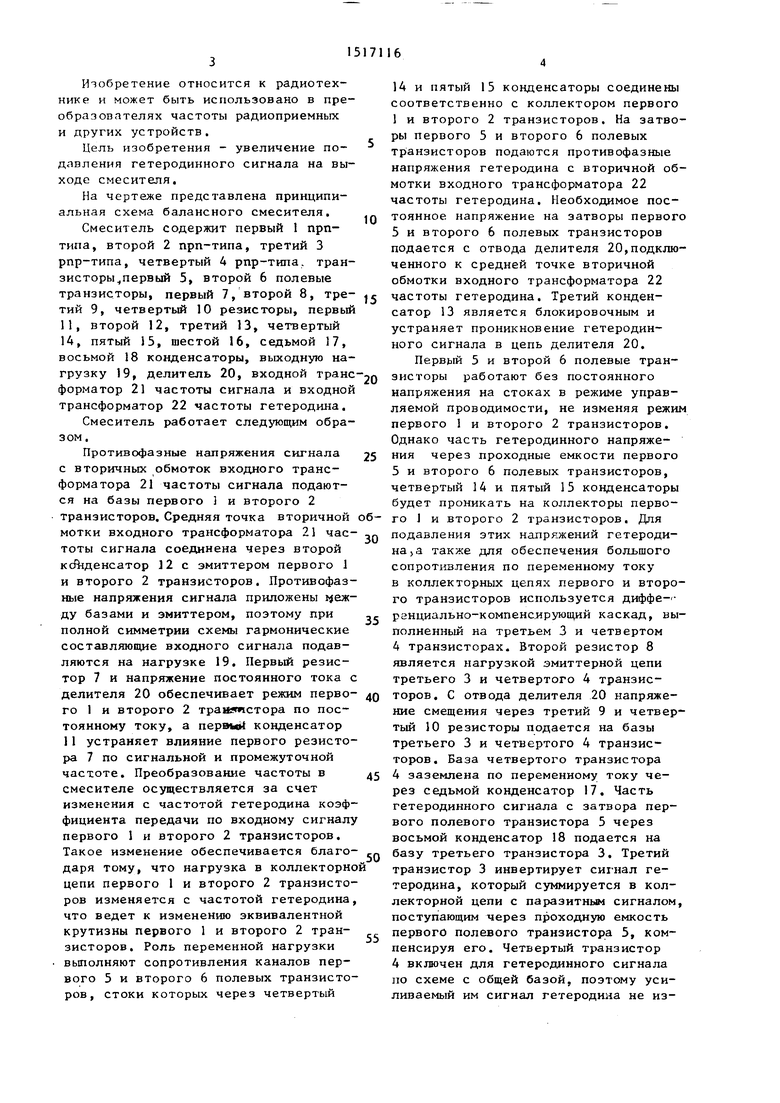

На чертеже представлена принципильная схема балансного смесителя.

Смеситель содержит первый 1 прп- типа, второй 2 прп-типа, третий 3 пр-типа, четвертый 4 рпр-типа. тран- зисторы первый 5, второй 6 полевые транзисторы, первый 7, второй 8, тре- с тий 9, четвертый 10 резисторы, первый 11, второй 12, третий 13, четвертый 14, пятый 15, шестой 16, седьмой 17, восьмой 18 конденсаторы, выходную нагрузку 19, делитель 20, входной TpaHc-jQ орматор 21 частоты сигнала и входной трансформатор 22 частоты гетеродина.

Смеситель работает следующим образом.

Противофазные напряжения сигнала 25 с вторичных обмоток входного трансорматора 21 частоты сигнала подаются на базы первого и второго 2 транзисторов. Средняя точка вторичной обмотки входного трансформатора 21 частоты сигнала соединена через второй ксА1денсатор 12 с эмиттером первого 1 и второго 2 транзисторов. Противофазные напряжения сигнала приложены цеж- ду базами и эмиттером, поэтому при полной симметрии схемы гармонические составляющие входного сигнала подавляются на нагрузке 19. Первый резистор 7 и напряжение постоянного тока с делителя 20 обеспечивает режим перво- до го 1 и второго 2 трайяястора по постоянному току, а первкй конденсатор 11 устраняет влияние первого резисто- ра 7 по сигнальной и промежуточной частоте. Преобразование частоты в д5 смесителе осуществляется за счет изменения с частотой гетеродина коэффициента передачи по входному сигналу первого 1 и второго 2 транзисторов. Такое изменение обеспечивается благодаря тому, что нагрузка в коллекторной цепи первого 1 и второго 2 транзисторов изменяется с частотой гетеродина, что ведет к изменению эквивалентной крутизны первого 1 и второго 2 транзисторов. Роль переменной нагрузки выполняют сопротивления каналов первого 5 и второго 6 полевых транзисторов, стоки которых через четвертый

30

.50

55

0

с Q

5 о 5

0

0

5

14 и пятый 15 конденсаторы соединены соответственно с коллектором первого 1 и второго 2 транзисторов. На затворы первого 5 и второго 6 полевых транзисторов подаются противофазные напряжения гетеродина с вторичной обмотки входного трансформатора 22 частоты гетеродина. Необходимое постоянное напряжение на затворы первого 5 и второго 6 полевых транзисторов подается с отвода делителя 20,подключенного к средней точке вторичной обмотки входного трансформатора 22 частоты гетеродина. Третий конденсатор 13 является блокировочным и устраняет проникновение гетеродинного сигнала в цепь делителя 20.

5 и второй 6 полевые транзисторы работают без постоянного напряжения на стоках в режиме управляемой проводимости, не изменяя режим первого 1 и второго 2 транзисторов. Однако часть гетеродинного напряжения через проходные емкости первого 5 и второго 6 полевых транзисторов, четвертый 14 и пятый 15 конденсаторы будет проникать на коллекторы первого 1 и второго 2 транзисторов. Для подавления этих напряжений гетеродина, а также для обеспечения большого сопротивления по переменному току в коллекторных цепях первого и второго транзисторов используется диффе- - ренциально-компенсирующий каскад, выполненный на третьем 3 и четвертом 4 транзисторах. Второй резистор 8 является нагрузкой эмиттерной цепи третьего 3 и четвертого 4 транзисторов. С отвода делителя 20 напряжение смещения через третий 9 и четвертый 10 резисторы подается на базы третьего 3 и четвертого 4 транзисторов. База четвертого транзистора 4 заземлена по переменному току через седьмой конденсатор 17. Часть гетеродинного сигнала с затвора первого полевого транзистора 5 через восьмой конденсатор 18 подается на базу третьего транзистора 3. Третий транзистор 3 инвертирует сигнал гетеродина, который суммируется в коллекторной цепи с паразитным сигналом, поступающим через проходную емкость первого полевого транзистора 5, компенсируя его. Четвертый транзистор 4 включен для гетеродинного сигнала по схеме с общей базой, поэтому усиливаемый им сигнал гетеродина не изменяет фазу и также компенсирует паразитный сигнал, поступающий через проходную емкость второго полевого транзистора 6. Уровень компенсирующих сигналов определяется делителем, образующим восьмым 18 и шестым 16 конденсаторами.

Таким образом, в предлагаемом устройстве высокое подавление гетеро динного сигнала определяется тремя факторами. Во-первых, гетеродинный сигнал проходит на выход через малые проходные емкости первого 1 и второго 2 транзисторов. Во-вторых, гете- родинный сигнал, изменяя сопротивления первого 5 и второго 6 полевых транзисторов, не изменяет режим первого 1 и второго 2 транзисторов, поэтому не меняется соотнощение их про ходных емкостей, что стабилизирует баланс. В-третьих, паразитный сигнал прошедший через проходиые емкости первого 5 и второго 6 полевых транзисторов, компенсируется дифференци- ально-компенсирующим каскадом.

Формула изобретения

Балансный смеситель, содерж-ащий первый и второй транзисторы, эмиттеры которых через параллельно соединенные первый резистор и первый конденсатор и последовательно с ними соединенную выходную нагрузку подключены к общей шине, а через второй конденсатор - к первому вьшоду делителя и среднему вьшоду вторичной обмотки входного трансформатора частоты сигнала, код5 0 5

0

5

торая включена между базами первого и второго транзисторов, третий и четвертый транзисторы противоположной проводимости, эмиттеры которьи через второй резистор соединены с выводом источника питания, коллектор третьего транзистора соединен с коллектором первого транзистора, а коллектор четвертого транзистора соединен с коллектором второго транзистора, входной трансформатор частоты гетеродина, средняя точка вторичной обмотки которого соединена с вторым отводом делителя и через третий конденсатор - с общей шиной, и четвертый конденсатор, отличающийся тем, что, с целью увеличения подавления гетеродинного сигнала на выходе, введены третий, четвертый резисторы, пятый, шестой, седьмой и восьмой конденсаторы, первый и второй полевые транзисторы, истоки которых соединены с общей шиной, а стоки через четвертый и пятый конденсаторы подключены соответственно к коллекторам третьего и четвертого транзисторов, вторичная обмотка входного трансформатора частоты гетеродина включена между затворами первого и второго полевых транзисторов, базы третьего и четвертого транзисторов через третий и четвертый резисторы подключены к третьему выводу делителя, и через шестой и седьмой конденсаторы - к общей шине, между затвором первого полевого транзистора и базой третьего транзистора включен восьмой конденсатор.

| название | год | авторы | номер документа |

|---|---|---|---|

| БАЛАНСНЫЙ СМЕСИТЕЛЬ | 1989 |

|

RU2017321C1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2005 |

|

RU2285330C1 |

| БАЛАНСНЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2004 |

|

RU2260244C1 |

| Управляемый резистор | 1983 |

|

SU1105902A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2004 |

|

RU2279180C1 |

| Смеситель | 1984 |

|

SU1224958A1 |

| ВЫСОКОЧАСТОТНЫЙ КВАРЦЕВЫЙ ГЕНЕРАТОР | 2010 |

|

RU2439775C1 |

| СМЕСИТЕЛЬ ЧАСТОТ | 2004 |

|

RU2266610C1 |

| Смеситель | 1989 |

|

SU1617624A1 |

| Ключевое устройство | 1990 |

|

SU1721796A1 |

Изобретение относится к радиотехнике. Цель изобретения - увеличение подавления гетеродинного сигнала на выходе смесителя. Балансный смеситель содержит транзисторы /Т/ 1 и 2 NPN-типа, Т 3 и 4 PNP-типа, полевые Т 5 и 6, резисторы 7...10, конденсаторы 11...18, выходную нагрузку 19, делитель 20 и входные трансформаторы 21 и 22 частоты сигнала и гетеродина соответственно. Цель достигается за счет того, что гетеродинный сигнал проходит на выход через малые проходные емкости Т 1 и 2. При этом гетеродинный сигнал, изменяя сопротивление Т 5 и 6, не изменяет режим Т 1 и Т 2, поэтому не меняется соотношение их проходных емкостей, что стабилизирует баланс. Кроме того, паразитный сигнал, прошедший через проходные емкости Т 5 и 6, компенсируется дифференциально-компенсирующим каскадом, выполненным на Т 3 и 4. 1 ил.

| Балансный смеситель | 1985 |

|

SU1264299A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-10-23—Публикация

1987-12-18—Подача