Изобретение относится к цифровой измерительной технике и может быть Использовано для точного измерения частоты в течение произвольного числа ее периодов, а также для измерения электрических и неэлектрических величин, предварительно преобразованных в частоту.

Цель изобретения - расширение диапазона измеряемых частот.

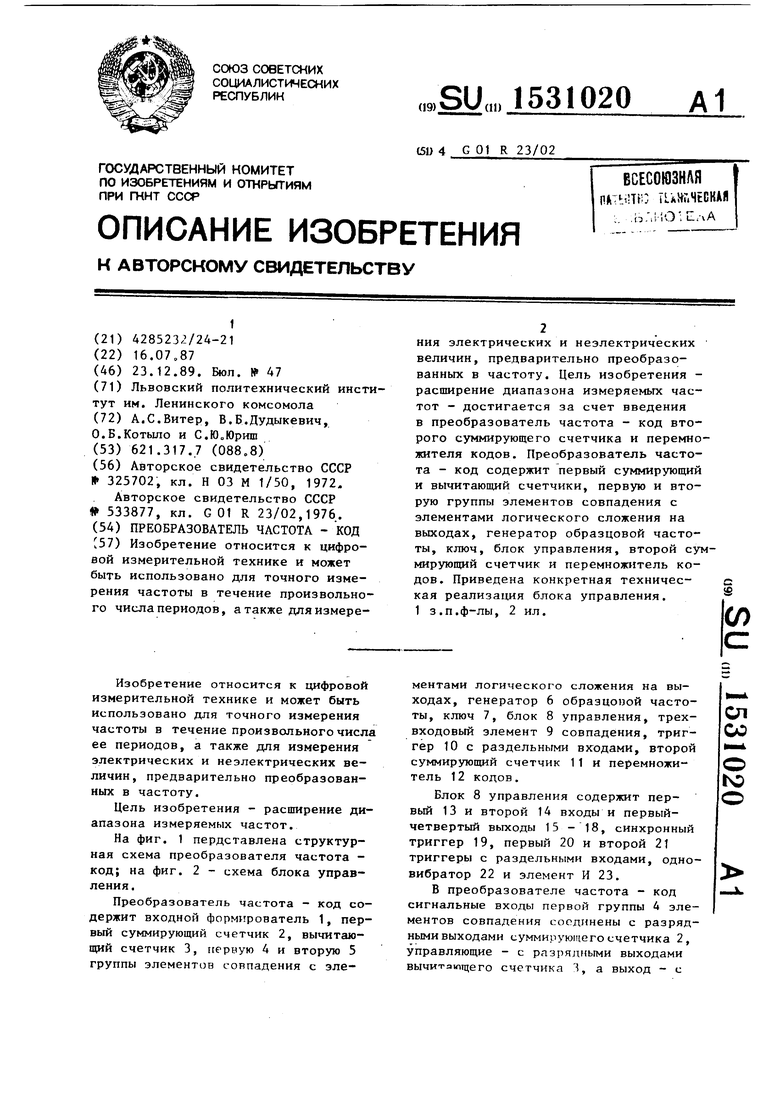

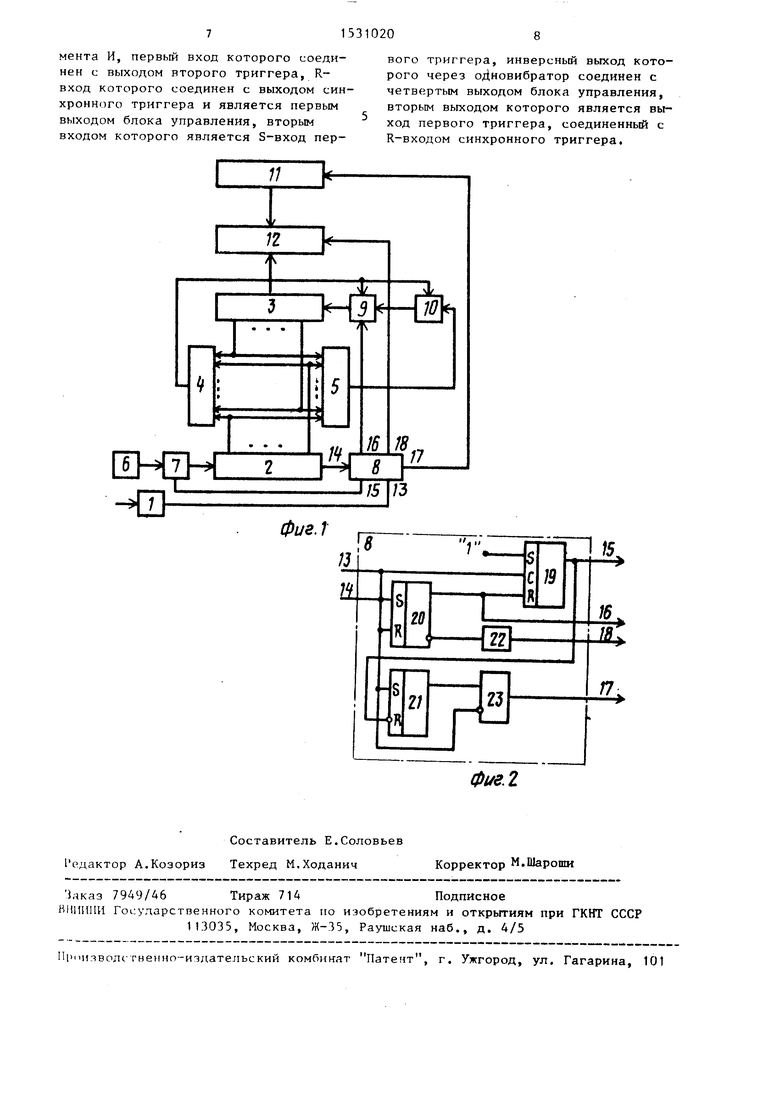

На фиг. 1 пердставлена структурная схема преобразователя частота - код; на фиг. 2 - схема блока управления.

Преобразователь частота - код содержит входной формирователь 1, первый суммирующий счетчик 2, вычитающий счетчик 3, первую 4 и вторую 5 группы элементов совпадения с элементами логического сложения на выходах, генератор 6 образцовой частоты, ключ 7, блок 8 управления, трех- входовый элемент 9 совпадения, триггер 10 с раздельными входами, второй суммирующий счетчик 11 И перемножитель 12 кодов.

Блок 8 управления содержит первый 13 и второй 14 входы и первый- четвертый выходы 15 - 18, синхронный триггер 19, первый 20 и второй 21 триггеры с раздельными входами, одно- вибратор 22 и элемент И 23.

Б преобразователе частота - код сигнальные входы первой группы 4 элементов совпадения соединены с разрядными выходами суммирующего счетчика 2, управляющие - с разрядными выходами вычитатщего счетчика Ч, а выход - с

СП

СО

ю

о

первым входом элемента 9 совпадения и с первым из раздельных входов триггера 10, второй вход которого соединен с выходом второй группы 5 элементов совпадения, управляющие входы которой соединены с разрядными выходами суммирующего счетчика 2,а сигнальные - с разрядными выходами вычитающего счетчика 3, вход которого соединен с выходом элемента 9 совпадения, второй вход которого соединен с выходом триггера 10, а третий - с вторым выходом блока 8 управления, первый выход 15 блока 8 управления соединен с управляющим входом ключа 7, вход которого соединен с выходом генератора 6 образцовой частоты, а выход - с входом суммирующего счетчика 2, выход которого соединен с вторым входом блока 8 управления, первый вход блока 8 управления соединен с выходом входного формирователя 1, вход которого является входом преобразователя, первая группа входов перемножителя 12 кодов соединена с разрядными выходами второго суммирующего счетчика 11, счетный вход которого соединен с третьим выходом блока 8 управления, четвертый выход которого соединен с разрешающим входом перемножителя 12 кодов, вторая группа входов которого соединена с разрядными выходами вычитающего счетчика 3.

Первый вход 13 блока 8 управления соединен с R-входом первого триггера 20, S-входом второго триггера 21, вторым входом элемента И 23 и С-вхо- дом синхронного триггера 19, выход которого является первым выходом 15 блока 8 управления и соединен с R-BX дом второго триггера 21, выход которого соединен с первым входом элемента И 23, выход которого является третьим выходом 17 блока 8 управления, второй выход 16 которого соединен с R-входом синхронного триггера 19 и выходом первого триггера 20, S-вход которого является вторьм входом 14 блока 8 управления, а инверсный выход - через одновибратор 22 соединен с четвертым выходом 18 блока 8 управления.

Преобразователь работает следующим образом.

В исходном состоянии ключ 7 и элемент 9 совпадения закрыты, счетчики 2, 3 и 11 находятся в нулевом состоянии. с приходом переднего фронта первого импульса измеряемой частоты блок 8 управления открывает ключ 7. Импульсы генератора 6 с частотой следования fp поступают на вход счетчика 2. Коэффициенты пересчета счетчиков 2 и 3 равны N

(к - коли10

чество двоичных разрядов счетчиков). При поступлении первых N импульсов на вход счетчика 2 в течение време5

0

5

0

5

0

5

0

происходит его переь Nm НИ t , ---

полнение и с блока 8 подается отпирающий потенциал на злемент 9 совпадения. С приходом переднего фронта первого после переполнения счетчика 2 импульса измеряемой частоты блок 8 управления закрывает ключ 7 и злемент 9 совпадения.

Таким образом, ключ 7 открыт в течение целого количества периодов п, т.е. в течение времени t - пТ (причем t t - 2t ,), где Т , - период измеряемой частоты. С момента времени t, импульсы с выхода первой группы 4 элементов совпадения поступают на один из входов элемента 9 совпадения и один из входов триггера 10, а импульсы выхода второй группы 5 элементов совпадения - на другой вход элемента 9 совпадения. Счетчики 2 и 3, первая группа 4 элементов совпаде НИН представляет собой двоичный умножитель частоты.

Частота следования импульсов на выходе этого двоичного умножителя равна

f

v где N

N N,

(1)

m число,

, содержгицееся в вычитающем счетчике 3. Средняя частота следования импульсов на выходе элемента 9 совпадения определяется f а-у и числом, содержащимся в счетчике 2. Из частоты fey вычитается частота импульсов обратной связи, получаемых путем их выборки из счетчиков 3 с помощью второй группы 5 элементов совладения, т.е.

Вих

faw - f.

tklic

К

ест

ос

(2) (3)

Д KOC коэффициент обратной связи, который равен

KOC NWN, (4)

где N - число, содержащееся в счетчике 2.

После преобразований на основа;ции выражений (1) - (4) получают

f Biu N -b N

(5)

Всего на счетчик 2 с учетом первых N HMynbcoB, приведших его к переполнению, к моменту времени t t поступает следующее количество импульсов

Nt N +-N - f. t. (6) Окончательное вьфажение для f. при нимает вид

f „ -Nl(t)|o Nj(t) ,. t,..x t

Число в вычитающем счетчике 3 уменьшается с момента времени t от величины Nj в соответствии с выражением

Hf(0-N -j-Sip

Продифференцировав уравнение и разделив переменные, получают

cli

(8)

ENi(t) Nf(t)

dt t

Проинтегрировав и делы интегрирования,

bNf(t)|J

Nfltl

ткуда

Njlt)

N.

- tn 11

, tL t

t

(10)

(11)

N

ЮТ

При t n T и t, -T- йолуча

to

N (t) Ъ-. ii. (12) fo-n-T, f, n

По окончанию счета блок 8 управления подает сигнал на разрешающий вход перемножителя 12 кодов. При этом происходит перемножение числа Nn, содержащегося в вычитающем счетчике 3, с числом п, равное количеству периодов TX и накапливающееся в .. счетчике 11 в процессе измерения.

Тогда окончательное вьфажение для числа N(t) имеет вид

2.

N.(t) f,.(13)

t Id

Таким образом, число, содержащееся в перемножителе 12 кодов после окончания п периодов Т, пропорционально измеряемой частоте f.

Формула изобретения

1. Преобразователь частота - код, содержащий входной формирователь.

5310206

вход которого является входом преобразователя, а выход соединен с первым входом блока управления, первый

, выход которого соединен с управляю- щим входом ключа, вход которого соединен с выходом генератора образцовой частоты, а выход - с входом первого суммирующего счетчика, вы- - 10 ход которого соединен с вторым входом блока управления, второй выход которого соединен с третьим входом трехвходового элемента совпадения, второй вход которого соединен

15 с выходом первой группы элементов совпадения с элементами логического сложения на выходах и первым входом триггера с раздельными входами, выход которого соединен с первым вхо20 дом трехвходового элемента совпадения, а второй вход - с выходом второй группы элементов совпадения с элементами логического сложения на выходах, управляющие входы которой

25 соединены с разрядными выходами

первого суммирующего счетчика, а сигнальные - с разрядными выходами вычитающего счетчика, сигнальные входы первой группы элементов совпаде30 ния с элементами логического сложения на выходах соединены с разряд- выходами первого суммирующего счетчика, а управляющие - с разрядными выходами вычитающего счетчика.

вход которого соединен с выходом

трехвходового элемента совпадения, отличающийся тем, что, с целью расширения диапазона измеряемых частот, в него введены второй

суммирующий счетчик и перемножитель кодов, первая группа входов которого соединена с разрядами второго суммирующего счетчика, счетный вход которого соединен с третьим выходом

блока управления, четвертый выход которого соединен с разрешающим входом перемножителя кодов, вторая группа входов которого соединена с разрядами вычитающего счетчика.

2. Преобразователь по п. 1, о т- личающийся тем, что блок управления содержит синхронньй триггер, первый и второй триггеры одно- вибратор и элемент И, выход которого является третьим выходом блока управления, первый вход которого соединен с С-входом синхронного триггера, R- входом первого триггера, S-входом второго триггера и вторым входом эле

мента И, первый вход которого соединен с выходом второго триггера, R- вход которого соединен с выходом синхронного триггера и является первым выходом блока управления, вторым входом которого является S-вход первого триггера, инверсный выход которого через оДновибратор соединен с четвертым выходом блока управления, вторым выходом которого является выход первого триггера, соединенный с R-входом синхронного триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частота-код | 1974 |

|

SU533877A1 |

| Цифровой фазометр | 1979 |

|

SU788025A1 |

| Преобразователь частоты следования импульсов в код | 1974 |

|

SU513323A1 |

| Цифровой частотомер | 1986 |

|

SU1372245A1 |

| Преобразователь частоты в код | 1975 |

|

SU600470A1 |

| Функциональный преобразовательчиСлА иМпульСОВ B цифРОВОй КОд | 1979 |

|

SU807285A1 |

| Арифметическое устройство | 1977 |

|

SU674016A1 |

| Число-импульсный функциональный преобразователь | 1982 |

|

SU1043645A1 |

| Цифровой измеритель параметров комплексного сопротивления | 1986 |

|

SU1437799A1 |

| Арифметическое устройство | 1979 |

|

SU773619A1 |

Изобретение относится к цифровой измерительной технике и может быть использовано для точного измерения частоты в течение произвольного числа периодов, а также для измерения электрических и неэлектрических величин, предварительно преобразованных в частоту. Цель изобретения - расширение диапазона измеряемых частот - достигается за счет введения в преобразователь частота-код второго суммирующего счетчика и перемножителя кодов. Преобразователь частота-код содержит первый суммирующий и вычитающий счетчики, первую и вторую группы элементов совпадения с элементами логического сложения на выходах, генератор образцовой частоты, ключ, блок управления, второй суммирующий счетчик и перемножитель кодов. Приведена конкретная техническая реализация блока управления. 1 з.п. ф-лы. 2 ил.

фие. Т

| СЛЕДЯЩИЙ НИЗКОЧАСТОТНЫЙ ПРЕОБРАЗОВАТЕЛЬ «ЧАСТОТА — КОД» | 0 |

|

SU325702A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь частота-код | 1974 |

|

SU533877A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-12-23—Публикация

1987-07-16—Подача