Изобретение относится к вычислительной технике и дискретной автома- тике и предназначено для ввода информации о состоянии источников дискретных сообщений, в частности сигналов состояния двухпозиционных датчиков исполнительной автоматики, в уп- равляющую вычислительную систему.

Цель изобретения - повышение достоверности вводимой информации в режиме контроля путем обнаружения постоянного ложного сигнала на выходах усилителей.

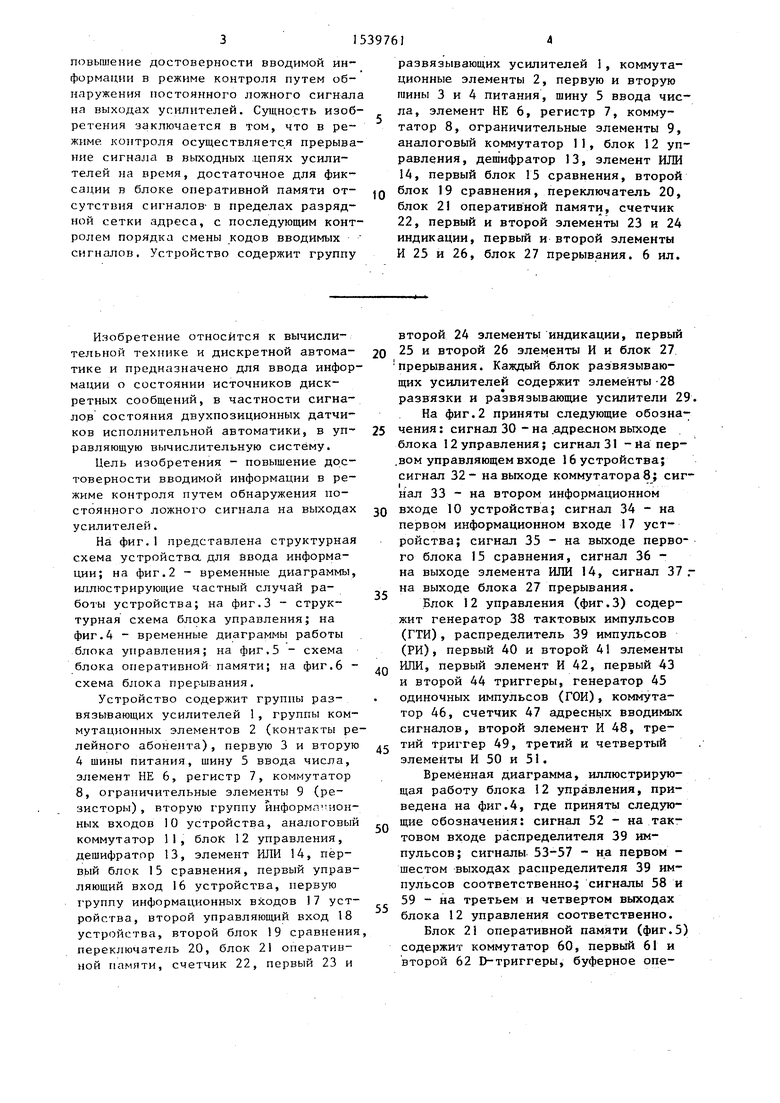

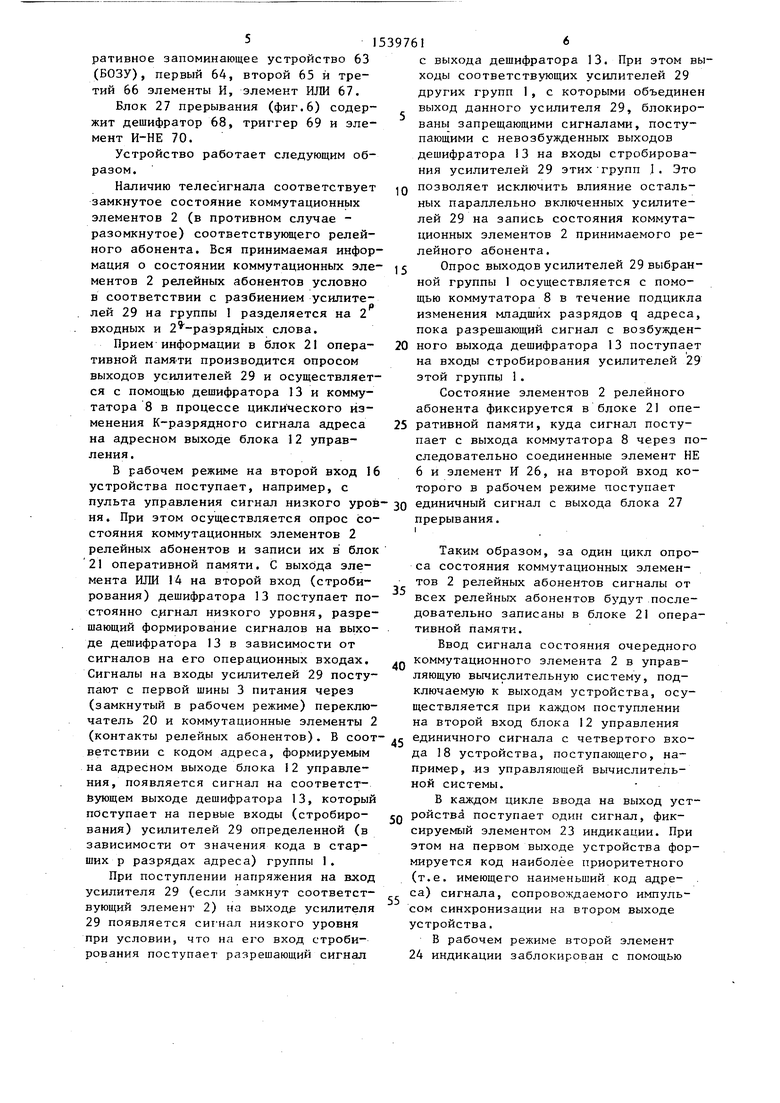

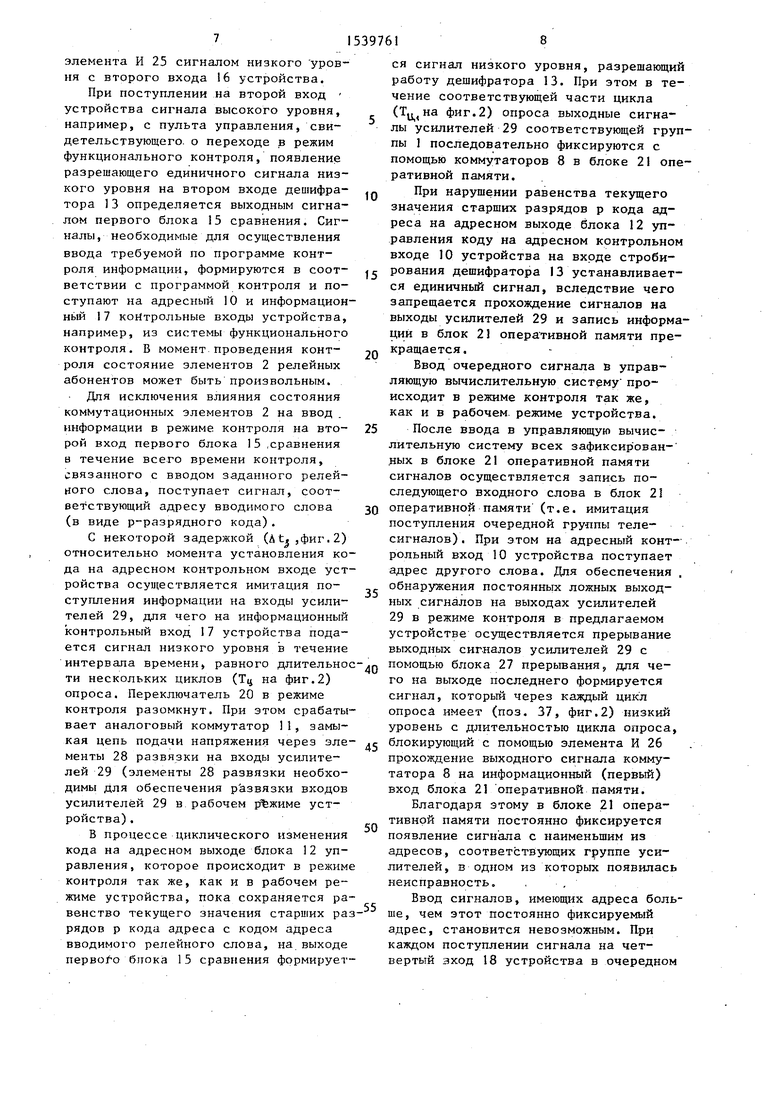

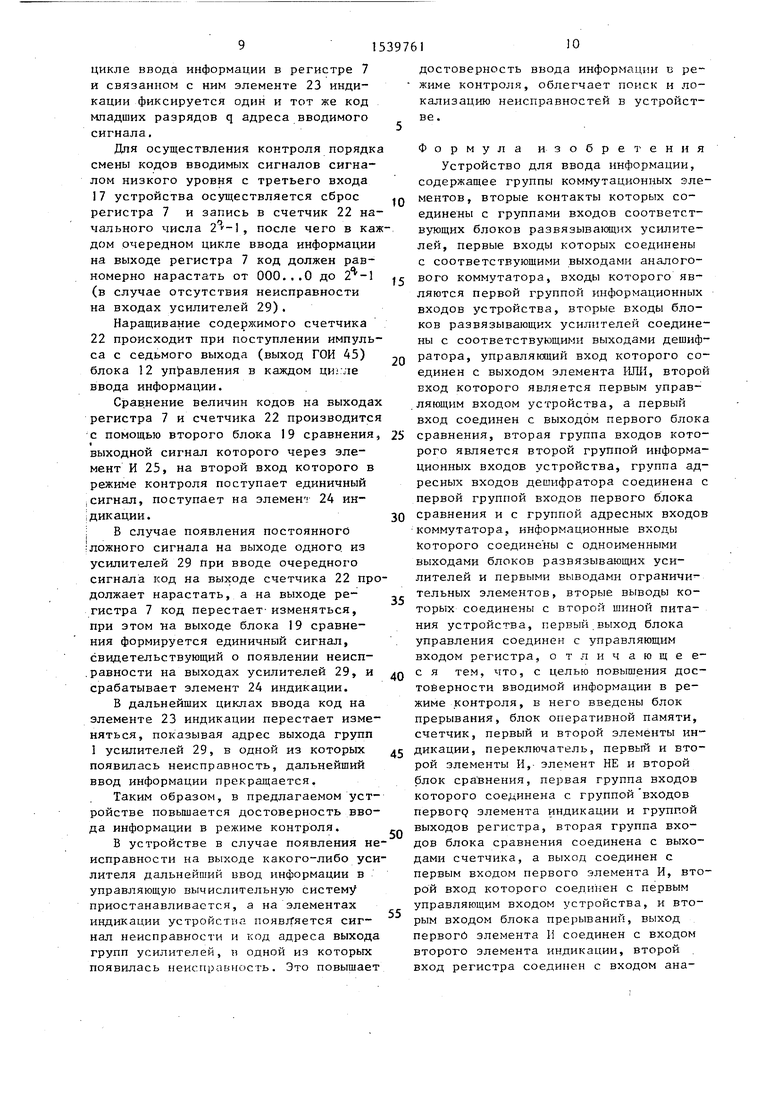

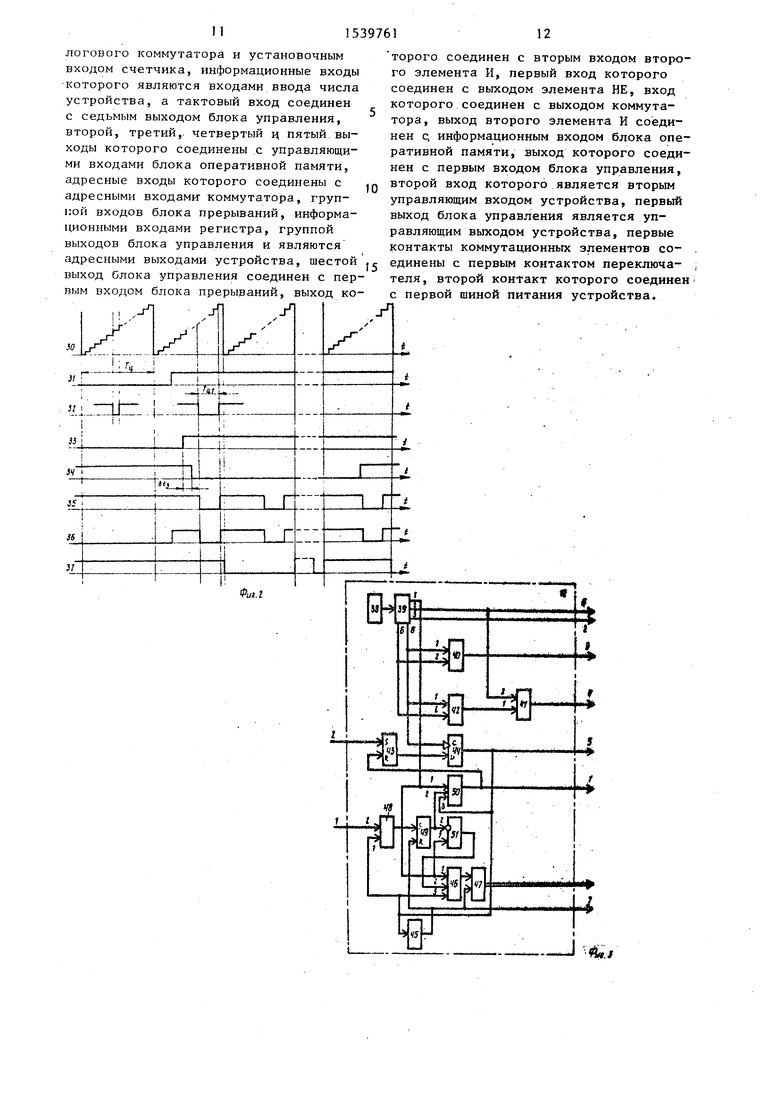

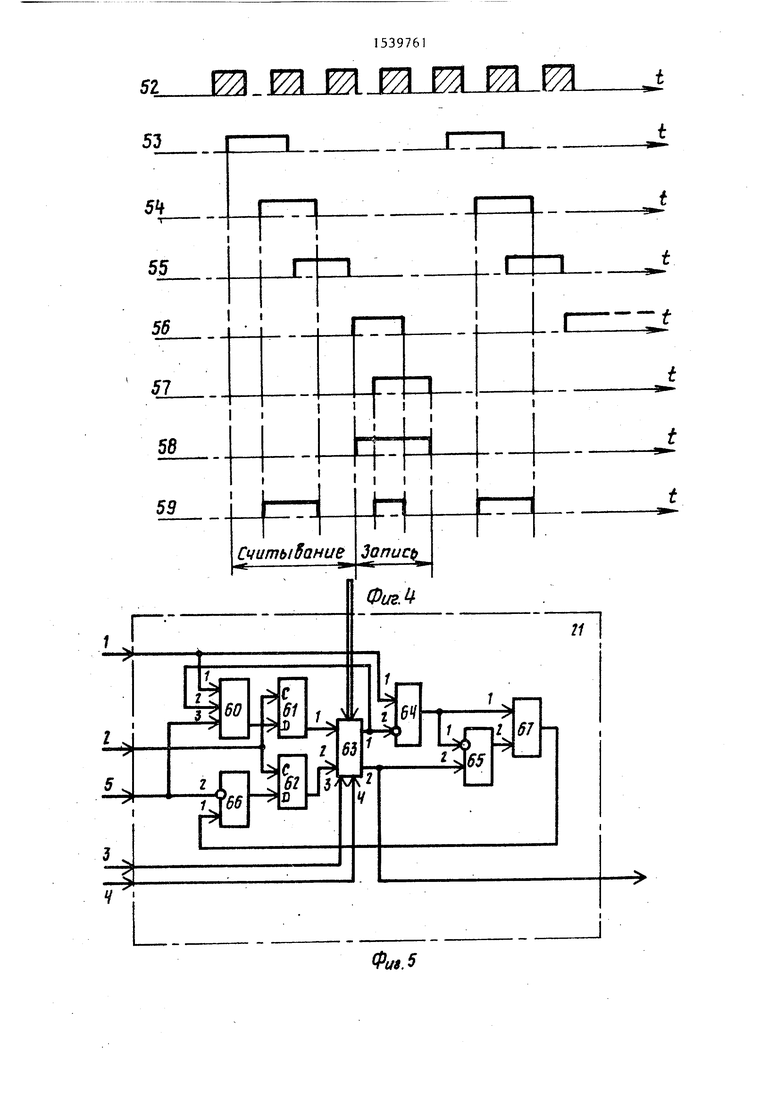

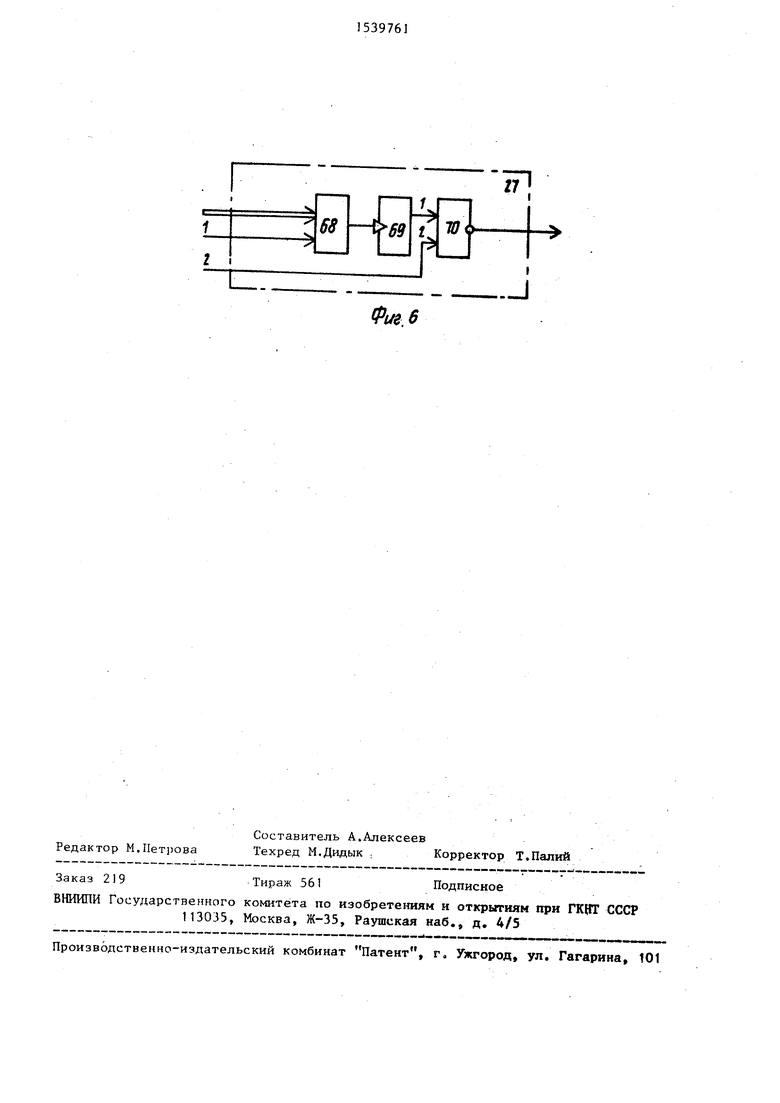

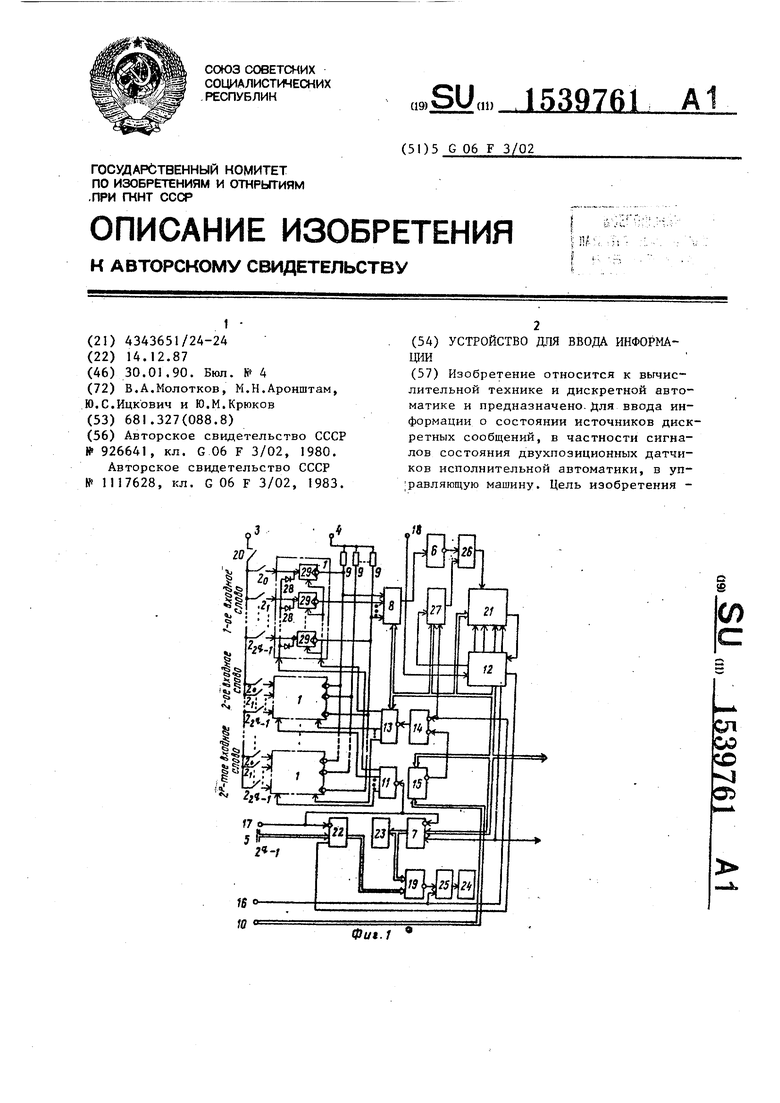

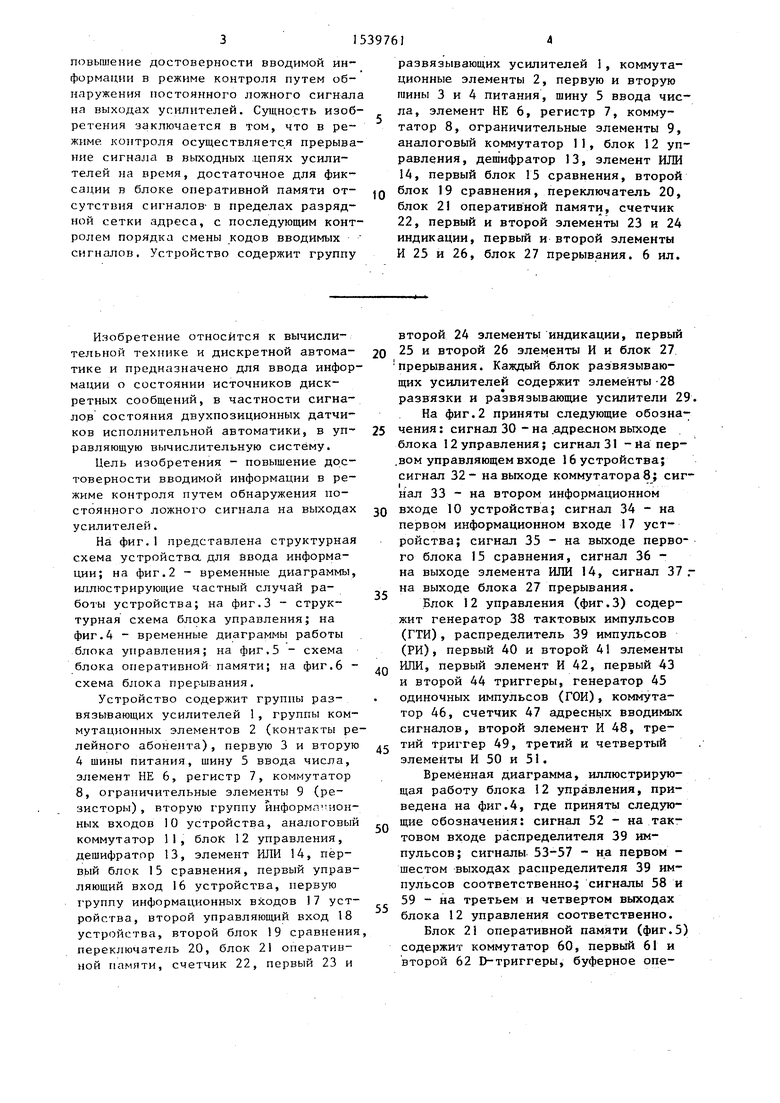

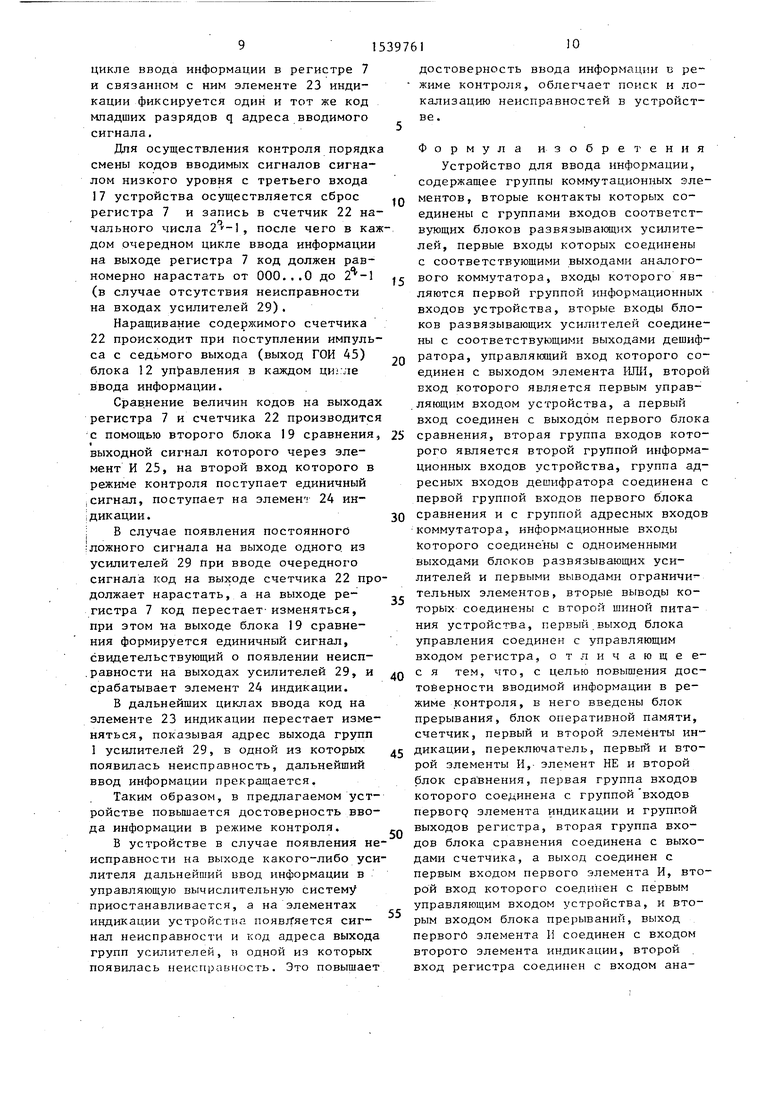

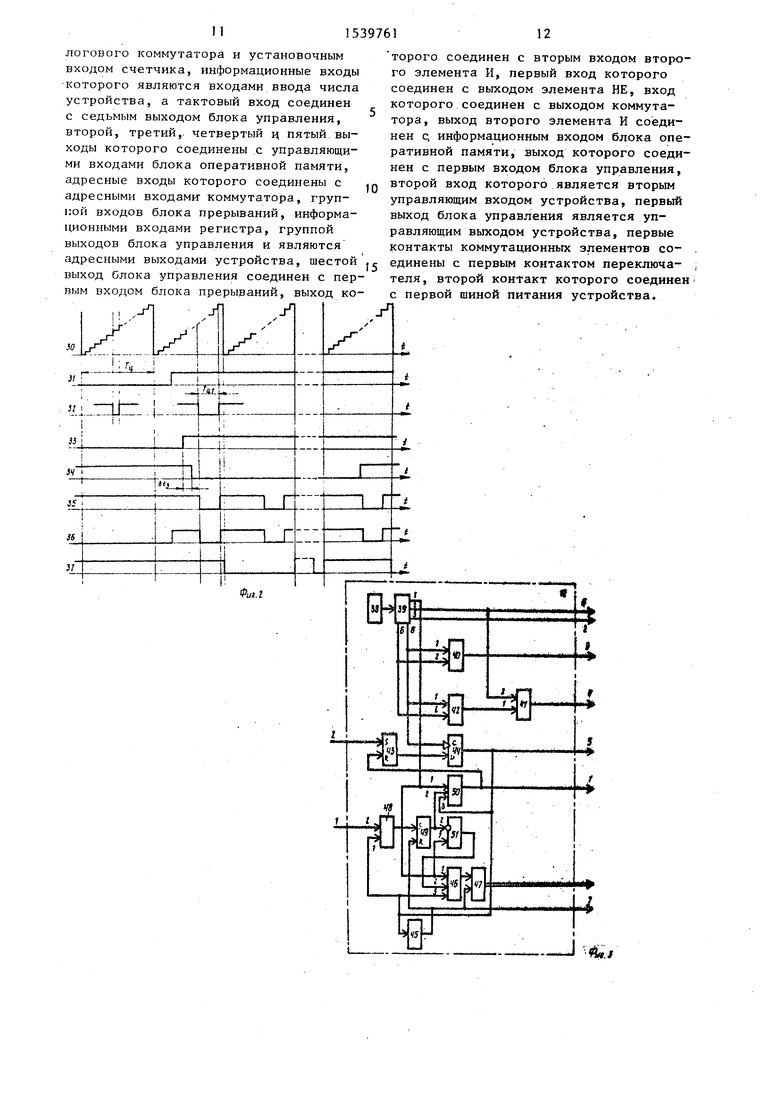

На фиг.1 представлена структурная схема устройства для ввода информации; на фиг.2 - временные диаграммы, иллюстрирующие частный случай работы устройства; на фиг.З - структурная схема блока управления; на фиг.4 - временные диаграммы работы блока управления; на фиг.З - схема блока оперативной памяти; на фиг.6 - схема блока прерывания.

Устройство содержит группы развязывающих усилителей 1, группы коммутационных элементов 2 (контакты релейного абонента), первую 3 и вторую 4 шины питания, шину 5 ввода числа, элемент НЕ 6, регистр 7, коммутатор 8, ограничительные элементы 9 (резисторы) , вторую группу информл1 ион- ных входов 10 устройства, аналоговый коммутатор 11, блок 12 управления, дешифратор 13, элемент ИЛИ 14, первый блок 15 сравнения, первый управляющий вход 16 устройства, первую группу информационных входов 17 устройства, второй управляющий вход 18 устройства, второй блок 19 сравнения переключатель 20, блок 21 оперативной памяти, счетчик 22, первый 23 и

5

0 5

0

Q

5 „

второй 24 элементы индикации, первый 25 и второй 26 элементы И и блок 27 1 прерывания. Каждый блок развязывающих усилителей содержит элементы-28 развязки и развязывающие усилители 29.

На фиг.2 приняты следующие обозначения : сигнал 30 - на .адресном выходе блока 12 управления; сигнал 31 -На пер- .вом управляющем входе 16 устройства; сигнал 32- на выходе коммутатора 8; сигнал 33 - на втором информационном входе 10 устройства; сигнал 34 - на первом информационном входе 17 устройства; сигнал 35 - на выходе первого блока 15 сравнения, сигнал 36 - на выходе элемента ИЛИ 14, сигнал 37,- на выходе блока 27 прерывания.

Блок 12 управления (фиг.З) содержит генератор 38 тактовых импульсов (ГТй), распределитель 39 импульсов (РИ), первый 40 и второй 41 элементы ИЛИ, первый элемент И 42, первый 43 и второй 44 триггеры, генератор 45 одиночных импульсов (ГОИ), коммутатор 46, счетчик 47 адресных вводимых сигналов, второй элемент И 48, третий триггер 49, третий и четвертый элементы И 50 и 5I.

Временная диаграмма, иллюстрирующая работу блока 12 управления, приведена на фиг.4, где приняты следующие обозначения: сигнал 52 - на тактовом входе распределителя 39 импульсов; сигналы 53-57 - на первом - шестом выходах распределителя 39 импульсов соответственно сигналы 58 и 59 - на третьем и четвертом выходах блока 12 управления соответственно.

Блок 21 оперативной памяти (фиг.5) содержит коммутатор 60, первый 61 и второй 62 D-триггеры, буферное oneративное запоминающее устройство 63 (БОЗУ), первый 64, второй 65 и третий 66 элементы И, элемент ИЛИ 67.

Блок 27 прерывания (фиг.6) содержит дешифратор 68, триггер 69 и элемент И-НЕ 70.

Устройство работает следующим образом.

Наличию телесигнала соответствует замкнутое состояние коммутационных элементов 2 (в противном случае - разомкнутое) соответствующего релейного абонента. Вся принимаемая информация о состоянии коммутационных элементов 2 релейных абонентов условно в соответствии с разбиением усилитер

лей 29 на группы 1 разделяется на 2 входных и 2 -разрядных слова.

Прием информации в блок 21 оперативной памяти производится опросом выходов усилителей 29 и осуществляется с помощью дешифратора 13 и коммутатора 8 в процессе циклического изменения К-разрядного сигнала адреса на адресном выходе блока 12 управления.

В рабочем режиме на второй вход 16 устройства поступает, например, с

10

с выхода дешифратора 13. При этом ходы соответствующих усилителей 29 других групп 1, с которыми объедин выход данного усилителя 29, блокир ваны запрещающими сигналами, посту пающими с невозбужденных выходов дешифратора 13 на входы стробирова ния усилителей 29 этих трупп 1. Эт позволяет исключить влияние осталь ных параллельно включенных усилите лей 29 на запись состояния коммута ционных элементов 2 принимаемого р лейного абонента.

Опрос выходов усилителей 29 выбран ной группы 1 осуществляется с помощью коммутатора 8 в течение подцикл изменения младших разрядов q адреса пока разрешающий сигнал с возбужден ного выхода дешифратора 13 поступае на входы стробирования усилителей 2 этой группы 1.

Состояние элементов 2 релейного абонента фиксируется в блоке 21 опе 25 ративной памяти, куда сигнал поступает с выхода коммутатора 8 через п следовательно соединенные элемент Н 6 и элемент И 26, на второй вход ко торого в рабочем режиме поступает

15

20

пульта управления сигнал низкого уров- зо единичный сигнал с выхода блока 27

ня. При этом осуществляется опрос состояния коммутационных элементов 2 релейных абонентов и записи их в блок 21 оперативной памяти. С выхода элемента ИЛИ 14 на второй вход (стробирования) дешифратора 13 поступает постоянно сигнал низкого уровня, разрешающий формирование сигналов на выходе дешифратора 13 в зависимости от сигналов на его операционных входах. Сигналы на входы усилителей 29 поступают с первой шины 3 питания через (замкнутый в рабочем режиме) переключатель 20 и коммутационные элементы 2

35

40

прерывания.

i

Таким образом, за один цикл опро са состояния коммутационных элементов 2 релейных абонентов сигналы от всех релейных абонентов будут после довательно записаны в блоке 21 опер тивной памяти.

Ввод сигнала состояния очередног коммутационного элемента 2 в управляющую вычислительную систему, подключаемую к выходам устройства, осу ществляется при каждом поступлении на второй вход блока 12 управления

с выхода дешифратора 13. При этом выходы соответствующих усилителей 29 других групп 1, с которыми объединен выход данного усилителя 29, блокированы запрещающими сигналами, поступающими с невозбужденных выходов дешифратора 13 на входы стробирова- ния усилителей 29 этих трупп 1. Это позволяет исключить влияние остальных параллельно включенных усилителей 29 на запись состояния коммутационных элементов 2 принимаемого релейного абонента.

Опрос выходов усилителей 29 выбранной группы 1 осуществляется с помощью коммутатора 8 в течение подцикла изменения младших разрядов q адреса, пока разрешающий сигнал с возбужденного выхода дешифратора 13 поступает на входы стробирования усилителей 29 этой группы 1.

Состояние элементов 2 релейного абонента фиксируется в блоке 21 опе- 5 ративной памяти, куда сигнал поступает с выхода коммутатора 8 через последовательно соединенные элемент НЕ 6 и элемент И 26, на второй вход которого в рабочем режиме поступает

5

0

5

0

прерывания.

i

Таким образом, за один цикл опроса состояния коммутационных элементов 2 релейных абонентов сигналы от всех релейных абонентов будут последовательно записаны в блоке 21 оперативной памяти.

Ввод сигнала состояния очередного коммутационного элемента 2 в управляющую вычислительную систему, подключаемую к выходам устройства, осуществляется при каждом поступлении на второй вход блока 12 управления

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1988 |

|

SU1539763A1 |

| Устройство для ввода информации | 1983 |

|

SU1117628A1 |

| Устройство для диспетчерской дуплексной связи | 1985 |

|

SU1293853A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Устройство для обмена информацией управляющей вычислительной машины с объектами управления | 1982 |

|

SU1030792A1 |

| Устройство для ввода информации | 1987 |

|

SU1529208A1 |

| Устройство для диагностики абонентов вычислительной сети | 1989 |

|

SU1679488A1 |

| Устройство для ввода информации | 1991 |

|

SU1828553A3 |

| Устройство для ввода информации | 1986 |

|

SU1345204A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ МОНТАЖА, ПАРАМЕТРОВ ЭЛЕКТРИЧЕСКИХ ЦЕПЕЙ И ДИАГНОСТИКИ НЕИСПРАВНОСТЕЙ СЛОЖНЫХ УСТРОЙСТВ ЭЛЕКТРОАППАРАТУРЫ И ТОКОРАСПРЕДЕЛИТЕЛЬНЫХ СЕТЕЙ | 2008 |

|

RU2377585C1 |

Изобретение относится к вычислительной технике и дискретной автоматике и предназначено для ввода информации о состоянии источников дискретных сообщений, в частности сигналов состояния двухпозиционных датчиков исполнительной автоматики, в управляющую машину. Целью изобретения является повышение достоверности вводимой информации в режиме контроля путем обнаружения постоянного ложного сигнала на выходах усилителей. Сущность изобретения заключается в том, что в режиме контроля осуществляется прерывание сигнала в выходных цепях усилителей на время, достаточное для фиксации в блоке оперативной памяти отсутствия сигналов в пределах разрядной сетки адреса, с последующим контролем порядка смены кодов вводимых сигналов. Устройство содержит группу развязывающих усилителей 1, коммутационные элементы 2, первую и вторую шины питания 3, 4, шину 5 ввода числа, элемент НЕ 6, регистр 7, коммутатор 8, ограничительные элементы 9, аналоговый коммутатор 11, блок управления 12, дешифратор 13, элемент ИЛИ 14, первый блок сравнения 15, второй блок сравнения 19, переключатель 20, блок оперативной памяти 21, счетчик 22, первый и второй элементы индикации 23, 24, первый и второй элементы И 25, 26, блок прерывания 27. 6 ил.

(контакты релейных абонентов). В соот- .с единичного сигнала с четвертого вховетствии с кодом адреса, формируемым на адресном выходе блока 12 управления, появляется сигнал на соответствующем выходе дешифратора 13, который поступает на первые входы (стробирования) усилителей 29 определенной (в зависимости от значения кода в старших р разрядах адреса) группы 1 .

При поступлении напряжения на вход усилителя 29 (если замкнут соответствующий элемент 2) на выходэ усилителя 29 появляется сигнап низкого уровня при условии, что на его вход стробирования поступает разрешающий сигнал

50

55

да 18 устройства, поступающего, например , из управляющей вычислительной системы.

В каждом цикле ввода на выход устройства поступает один сигнал, фиксируемый элементом 23 индикации. При этом на первом выходе устройства формируется код наиболее приоритетного (т.е. имеющего наименьший код адреса) сигнала, сопровождаемого импульсом синхронизации на втором выходе устройства.

В рабочем режиме второй элемент 24 индикации заблокирован с помощью

0

5

да 18 устройства, поступающего, например , из управляющей вычислительной системы.

В каждом цикле ввода на выход устройства поступает один сигнал, фиксируемый элементом 23 индикации. При этом на первом выходе устройства формируется код наиболее приоритетного (т.е. имеющего наименьший код адреса) сигнала, сопровождаемого импульсом синхронизации на втором выходе устройства.

В рабочем режиме второй элемент 24 индикации заблокирован с помощью

элемента И 25 сигналом низкого уровня с второго входа 16 устройства.

При поступлении на второй вход устройства сигнала высокого уровня, например, с пульта управления, свидетельствующего о переходе в режим функционального контроля, появление разрешающего единичного сигнала низкого уровня на втором входе дешифратора 3 определяется выходным сигналом первого блока 15 сравнения. Сигналы, необходимые для осуществления ввода требуемой по программе контроля информации, формируются в соответствии с программой контроля и поступают на адресный 10 и информационный 17 контрольные входы устройства, например, из системы функционального контроля, В момент проведения контроля состояние элементов 2 релейных абонентов может быть произвольным.

Для исключения влияния состояния коммутационных элементов 2 на ввод . информации в режиме контроля на второй вход первого блока 15 сравнения в течение всего времени контроля, связанного с вводом заданного релейного слова, поступает сигнал, соответствующий адресу вводимого слова (в виде р-разрядного кода).

С некоторой задержкой (At. ,фиг2) относительно момента установления кода на адресном контрольном входе устройства осуществляется имитация поступления информации на входы усилителей 29, для чего на информационный контрольный вход 17 устройства подается сигнал низкого уровня в течение интервала времени, равного длительноти нескольких циклов (Тц на фиг.2) опроса. Переключатель 20 в режиме контроля разомкнут. При этом срабатывает аналоговый коммутатор 11, замыкая цепь подачи напряжения через элементы 28 развязки на входы усилителей 29 (элементы 28 развязки необходимы для обеспечения развязки входов усилителей 29 в рабочем ргежиме устройства) .

В процессе циклического изменения кода на адресном выходе блока 12 управления, которое происходит в режим контроля так же, как и в рабочем режиме устройства, пока сохраняется равенство текущего значения старших рарядов р кода адреса с кодом адреса вводимого релейного слова, на выходе первого бпока 15 сравнения формирует

0

5

0

5

0

5

0

5

ся сигнал низкого уровня, разрешающий работу дешифратора 13. При этом в течение соответствующей части цикла ( фиг.2) опроса выходные сигналы усилителей 29 соответствующей группы 1 последовательно фиксируются с помощью коммутаторов 8 в блоке 21 оперативной памяти.

При нарушении равенства текущего значения старших разрядов р кода адреса на адресном выходе блока 12 управления коду на адресном контрольном входе 10 устройства на входе строби- рования дешифратора 13 устанавливается единичный сигнал, вследствие чего запрещается прохождение сигналов на выходы усилителей 29 и запись информации в блок 2 оперативной памяти прекращается.

Ввод очередного сигнала в управляющую вычислительную систему происходит в режиме контроля так же, как и в рабочем режиме устройства.

После ввода в управляющую вычислительную систему всех зафиксированных в блоке 21 оперативной памяти сигналов осуществляется запись последующего входного слова в блок 21 оперативной памяти (т.е. имитация поступления очередной группы телесигналов) . При этом на адресный контрольный вход 10 устройства поступает адрес другого слова. Для обеспечения . обнаружения постоянных ложных выходных сигналов на выходах усилителей 29 в режиме контроля в предлагаемом устройстве осуществляется прерывание выходных сигналов усилителей 29 с помощью блока 27 прерывания, для чего на выходе последнего формируется сигнал, который через каждый цикл опроса имеет (поз. 37, фиг.2) низкий уровень с длительностью цикла опроса, блокирующий с помощью элемента И 26 прохождение выходного сигнала коммутатора 8 на информационный (первый) вход блока 21 оперативной памяти.

Благодаря этому в блоке 21 оперативной памяти постоянно фиксируется появление сигнала с наименьшим из адресов, соответствующих группе усилителей, в одном из которых появилась неисправность.

Ввод сигналов, имеющих адреса больше, чем этот постоянно фиксируемый адрес, становится невозможным. При каждом поступлении сигнала на четвертый .зход 18 устройства в очередном

цикле ввода информации в регистре 7 и связанном с ним элементе 23 индикации фиксируется один и тот же код младших разрядов q адреса вводимого сигнала.

Для осуществления контроля порядка смены кодов вводимых сигналов сигналом низкого уровня с третьего входа 17 устройства осуществляется сброс регистра 7 и запись в счетчик 22 начального числа , после чего в каждом очередном цикле ввода информации на выходе регистра 7 код должен равномерно нарастать от 000...0 до (в случае отсутствия неисправности на входах усилителей 29).

Наращивание содержимого счетчика 22 происходит при поступлении импульса с седьмого выхода (выход ГОИ 45) блока 12 управления в каждом цш ле ввода информации.

Сравнение величин кодов на выходах регистра 7 и счетчика 22 производится с помощью второго блока 19 сравнения, выходной сигнал которого через элемент И 25, на второй вход которого в режиме контроля поступает единичный сигнал, поступает на элеменг| 24 индикации.

В случае появления постоянного ложного сигнала на выходе одного из усилителей 29 при вводе очередного сигнала код на выходе счетчика 22 продолжает нарастать, а на выходе регистра 7 код перестает изменяться, при этом на выходе блока 19 сравнения формируется единичный сигнал, свидетельствующий о появлении неисправности на выходах усилителей 29, и срабатывает элемент 24 индикации.

В дальнейших циклах ввода код на элементе 23 индикации перестает изменяться, показывая адрес выхода групп 1 усилителей 29, в одной из которых появилась неисправность, дальнейший ввод информации прекращается.

Таким образом, в предлагаемом устройстве повышается достоверность ввода информации в режиме контроля.

В устройстве в случае появления неисправности на выходе какого-либо усилителя дальнейший ввод информации в управляющую вычислительную систему приостанавливается, а на элементах индикации устройстна появляется сигнал неисправности и код адреса выхода групп усилителей, в одной из которых появилась неиспр ншосгь. Это повышает

10

5

0

5

0

5

0

5

0

5

достоверность ввода информации с ре жиме контроля, облегчает поиск и локализацию неисправностей в устройстве.

Формула изобретения

Устройство для ввода информации, содержащее группы коммутационных элементов, вторые контакты которых соединены с группами входов соответствующих блоков развязывающих усилителей, первые входы которых соединены с соответствующими выходами аналогового коммутатора, входы которого являются первой группой информационных входов устройства, вторые входы блоков развязывающих усилителей соединены с соответствующими выходами дешифратора, управляющий вход которого соединен с выходом элемента ИЛИ, второй вход которого является первым управляющим входом устройства, а первый вход соединен с выходом первого блока сравнения, вторая группа входов которого является второй группой информационных входов устройства, группа адресных входов дешифратора соединена с первой группой входов первого блока сравнения и с группой адресных входов коммутатора, информационные входы Которого соединены с одноименными выходами блоков развязывающих усилителей и первыми выводами ограничительных элементов, вторые выводы которых соединены с второй шиной питания устройства, первый выход блока управления соединен с управляющим входом регистра, отличающее- с я тем, что, с целью повышения достоверности вводимой информации в режиме контроля, в него введены блок прерывания, блок оперативной памяти, счетчик, первый и второй элементы индикации, переключатель, первый и второй элементы И, элемент НЕ и второй блок сравнения, первая группа входов которого соединена с группой входов первого элемента индикации и группой выходов регистра, вторая группа входов блока сравнения соединена с выходами счетчика, а выход соединен с первым входом первого элемента И, второй вход которого соединен с первым управляющим входом устройства, и вторым входом блока прерываний, выход первого элемента И соединен с входом второго элемента индикации, второй вход регистра соединен с входом аналотового коммутатора и установочным входом счетчика, информационные входы которого являются входами ввода числа устройства, а тактовый вход соединен с седьмым выходом блока управления, второй, третий, четвертый и. пятый выходы которого соединены с управляющими входами блока оперативной памяти, адресные входы которого соединены с адресными входами коммутатора, группой входов блока прерываний, информационными входами регистра, группой выходов блока управления и являются адресными выходами устройства, шестой выход блока управления соединен с первым входом блока прерываний, выход ко

торого соединен с вторым входом второго элемента И, первый вход которого соединен с выходом элемента НЕ, вход которого соединен с выходом коммутатора, выход второго элемента И соединен с, информационным входом блока оперативной памяти, выход которого соединен с первым входом блока управления, второй вход которого является вторым управляющим входом устройства, первый выход блока управления является управляющим выходом устройства, первые контакты коммутационных элементов соединены с первым контактом переключателя, второй контакт которого соединен с первой шиной питания устройства.

52т т иъ ттул тj

II

i i

56

55

Считыбание

L

t

t

t

iiii t

я-Э

Запись

/

EF

2

67 u-J

.5

Фиг 6

| Устройство для ввода информации | 1980 |

|

SU926641A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода информации | 1983 |

|

SU1117628A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-30—Публикация

1987-12-14—Подача