сл

4ь

sj

GO СС

мостах на ключах 4-15 переменного Тока и одном полумосте ня ключах 16- 1 в виде транзисторов, шунтированных возвратными диодами, к которому подключен отвод от промежуточной точки первичной обмотки выходного трансформатора 28. Вторичные обмотки 31- 33 выходных трансформаторов мостовых

инверторных ячеек соединены звездой. Ключи 4-21 полумостов управляются с 18-ти выходов блока управления по алгоритму, обеспечивающему формирование семиступенчатого фазного напряжения с широтно-импульсной частичной (на неполную глубину) модуляцией в процессе регулирования. 6 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления преобразователем постоянного напряжения в трехфазное | 1987 |

|

SU1504764A1 |

| Устройство для управления трехфазным преобразователем постоянного напряжения | 1988 |

|

SU1598084A1 |

| Устройство для управления преобразователем постоянного напряжения в трехфазное квазисинусоидальное | 1988 |

|

SU1617587A1 |

| Преобразователь постоянного напряжения в трехфазное | 1985 |

|

SU1292143A1 |

| Устройство для управления преобразователем постоянного напряжения в трехфазное | 1988 |

|

SU1644331A1 |

| Трехфазный преобразователь | 1985 |

|

SU1443099A1 |

| Устройство для управления преобразователем постоянного напряжения в трехфазное квазисинусоидальное | 1985 |

|

SU1415379A1 |

| Устройство для управления преобразователем постоянного напряжения в квазисинусоидальное трехфазное | 1985 |

|

SU1304150A1 |

| Устройство для управления регулируемым по напряжению преобразователем постоянного напряжения в трехфазное | 1986 |

|

SU1471268A1 |

| Мостовой инвертор | 1986 |

|

SU1554096A1 |

Изобретение относится к электротехнике и может быть использовано в системах вторичного электропитания и электропривода. Цель изобретения - повышение качества выходного напряжения за счет уменьшения коэффициента гармоник. Преобразователь содержит три мостовые инверторные ячейки 1,2,3. Каждая мостовая инверторная ячейка выполнена на двух полумостах на ключах 4-15 переменного тока и одном полумосте на ключах 16-21 в виде транзисторов, шунтированных возвратными диодами, к которому подключен отвод от промежуточной точки первичной обмотки выходного трансформатора 28. Вторичные обмотки 31-33 выходных трансформаторов мостовых инверторных ячеек соединены звездой. Ключи 4-21 полумостов управляются с 18-ти выходов блока управления по алгоритму, обеспечивающему формирование семиступенчатого фазного напряжения с широтно-импульсной частичной (на неполную глубину) модуляцией в процессе регулирования. 6 ил.

Изобретение относится к электротехнике и может быть использовано в системах вторичного электропитания и электропривода.

Цель изобретения - повышение качества выходного напряжения за счет уменьшения коэффициента гармоник.

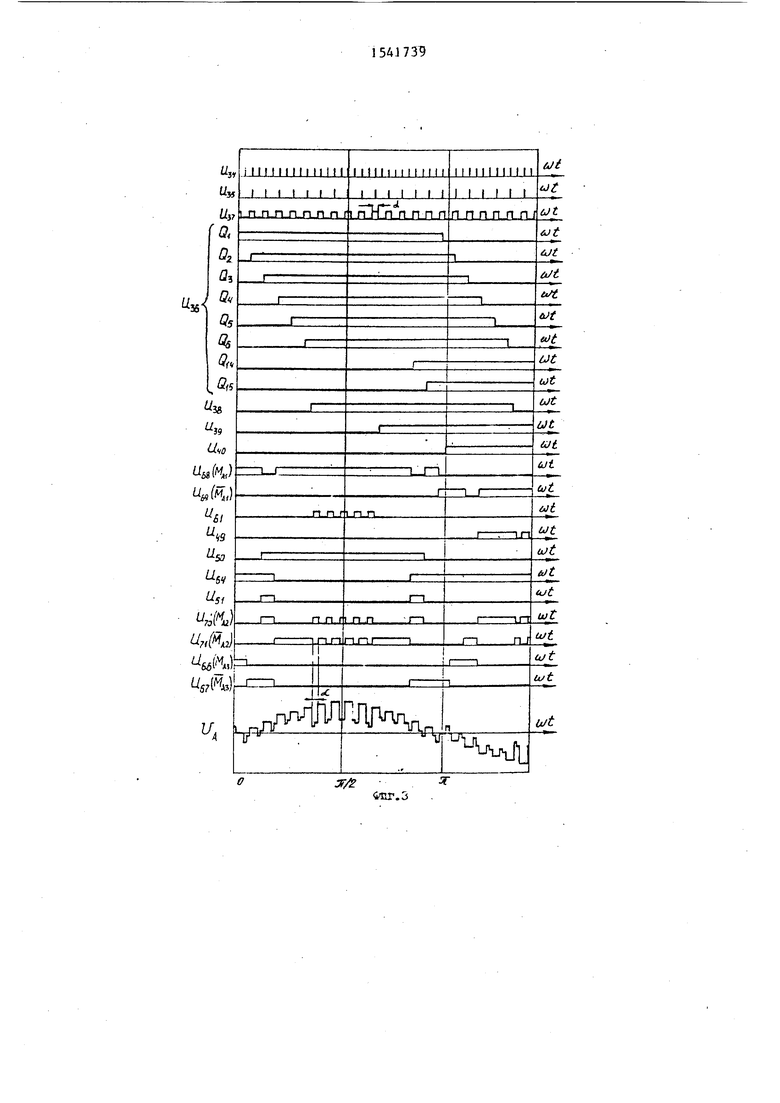

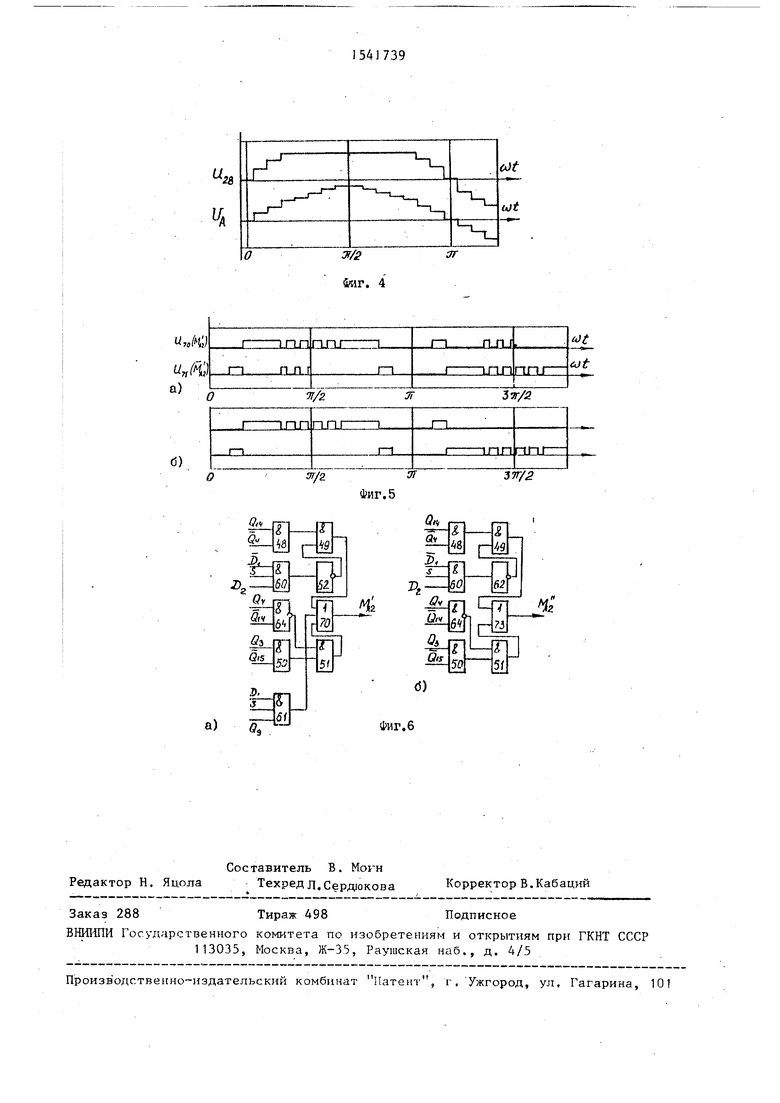

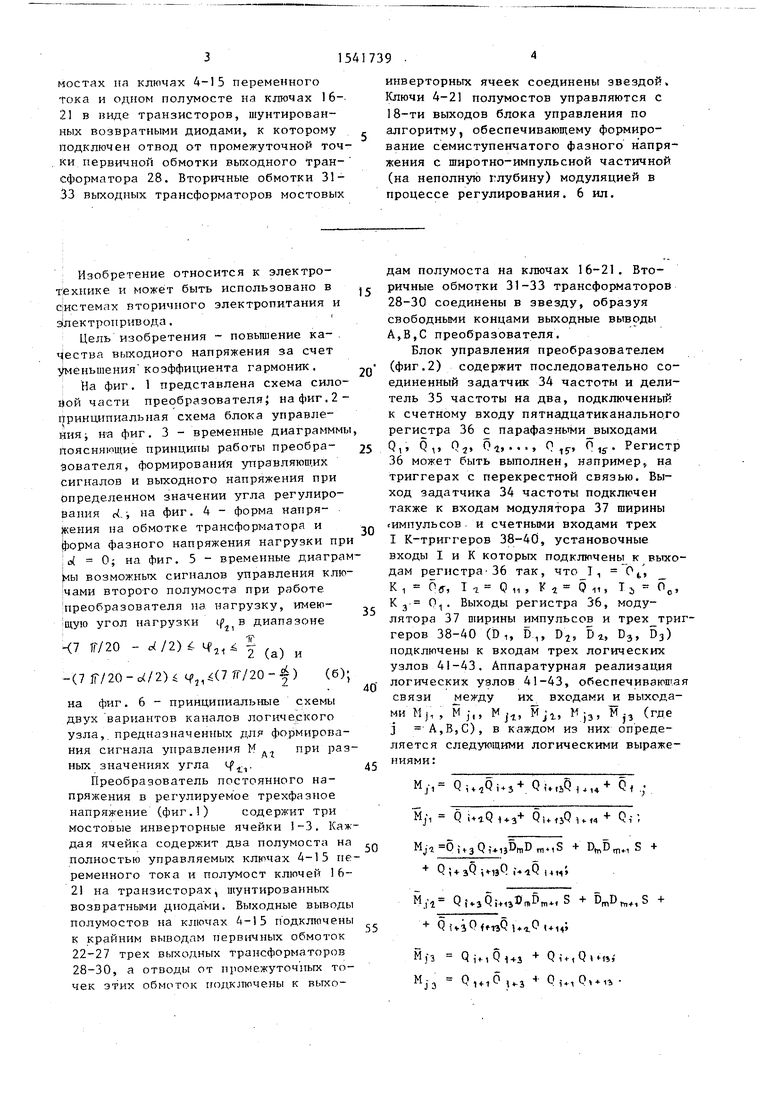

На фиг. 1 представлена схема сило- ой части преобразователя; на фиг. 2- принципиальная схема блока управления, на фиг. 3 - временные диаграмммы поясняющие принципы работы преобра- дователя, формирования управляющих сигналов и выходного напряжения при Определенном значении угла регулирования d , на фиг. 4 - форма напряжения на обмотке трансформатора и форма фазного напряжения нагрузки при о( 0; на фиг. 5 - временные диаграм мы возможных, сигналов управления кпю- чами второго полумоста при работе преобразователя на нагрузку, имею- щую угол нагрузки ifti в диапазоне

1Г/20 - Л/2) Ј if

1 & У (а) и

-()4 ,(7ТГ/20-)

(б);

на фиг. 6 - принципиальные схемы двух вариантов каналов логического узла, предназначенных для формирования сигнала управления F дг при разных значениях угла iftl

Преобразователь постоянного напряжения в регулируемое трехфазное напряжение (фиг.) содержит три мостовые инверторные ячейки )-3, Каждая ячейка содержит два полумоста на полностью управляемых ключах 4-15 переменного тока и полумост ключей 16- 21 на транзисторах, шунтированных возвратными диодами. Выходные выводы полумостов на ключах 4-15 подключены к крайним выводам первичных обмоток 22-27 трех выходных трансформаторов 28-30, а отводы от промежуточных точек этих обмоток подключены к вьтхо

Q

5 Q 5

0

5

дам полумоста на ключах 16-21. Вторичные обмотки 31-33 трансформаторов 28-30 соединены в звезду, образуя свободными концами выходные выводы А,В,С преобразователя.

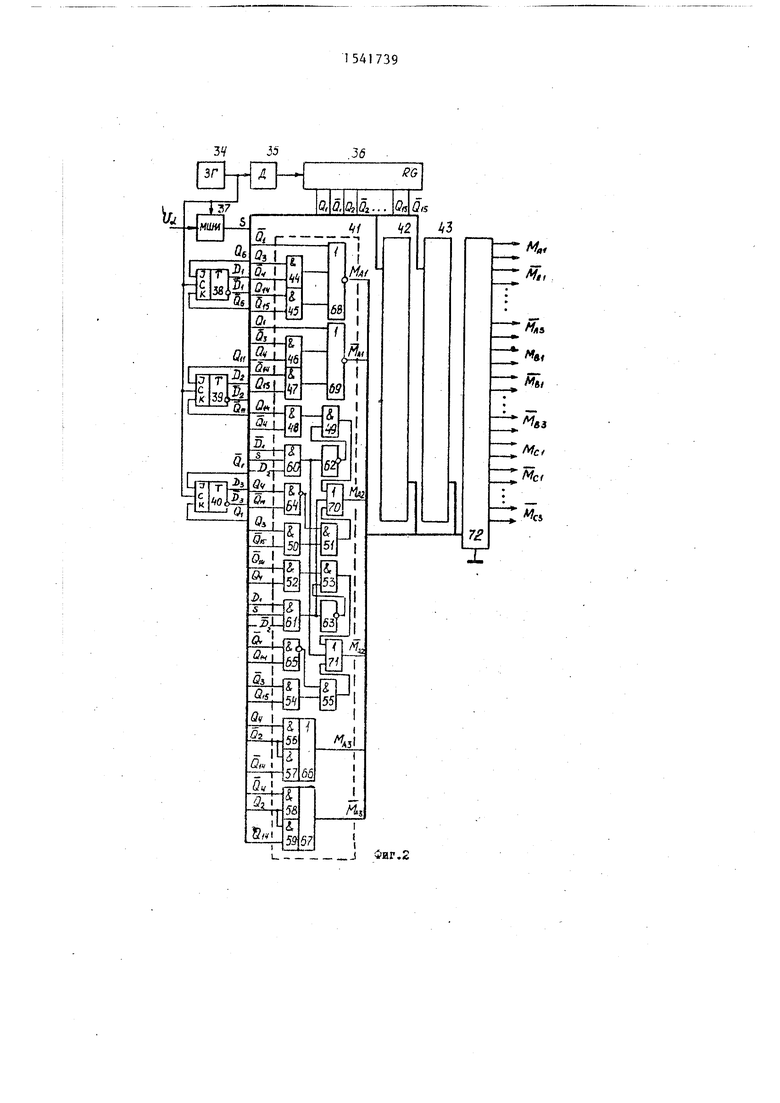

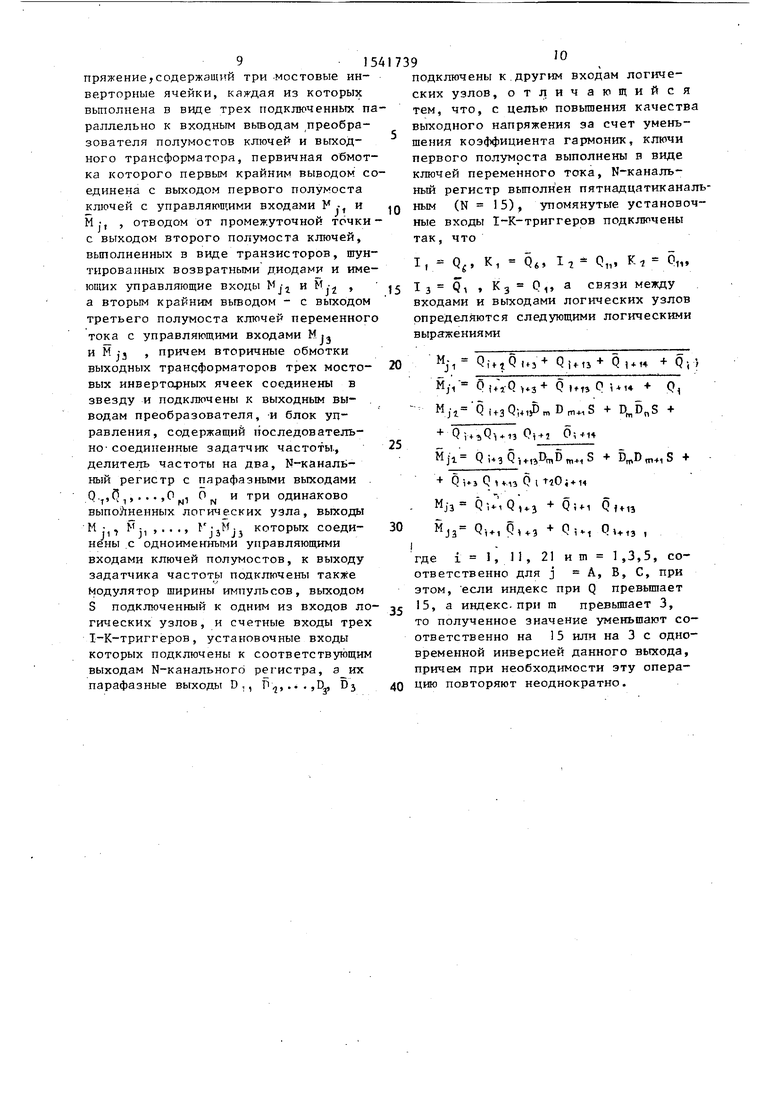

Блок управления преобразователем (фиг.2) содержит последовательно соединенный задатчик 34 частоты и делитель 35 частоты на два, подключенный к счетному входу пятнадцатиканального регистра 36 с парафазными выходами Q,. Q,, 02, 0, ..., О 15-, 01ЈГ. Регистр 36 может быть выполнен, например, на триггерах с перекрестной связью. Выход задатчика 34 частоты подключен также к входам модулятора 37 ширины симпульсов и счетными входами трех I К-триггеров 38-40, установочные входы I и К которых подключены к выходам регистра 36 так, что 11 С1 t t , ,1,,, Т 5 0„, К3 О,. Выходы регистра 36, модулятора 37 ширины импульсов и трех триг- геров 38-40 (D ,, D,, Ъг, D 4, D3, D3) подключены к входам трех логических узлов 4I-43. Аппаратурная реализация логических узлов 41-43, обеспечивающая связи межДУ их входами и выхода- миМ)л, Mj,, Mj4, м;г, Mj3, Mj3 (где j А,В,С), в каждом из них определяется следующими логическими выражениями:

Mj,e Q,,,Q, + 3+ Qu,iQM,4+ Q ; и,-, Q . + Q,-;

50

,43Q,--n}PmDmMS + .,5 +

+ Qi + .4Qt44;

M,4 Qt aQiHs i 6|n iS + + + QuaOftnQUtOUu;

Mj-3 + Qn-,QtMii MJ3 Q,6U3 0,,0

Индекс i для фазы А равен 1, для фазы В i 11, а для фазы С i 21. Если определенный по данным выражениям результирующий индекс соответствующего выхода регистра 36 окажется больше 15 следует осуществить операцию замены: Q-, Qf , где 1 i-15. Аналогично, индекс m для фазы А равен 1, для фазы В m 3 и для фазы С m 5, a Dm Dn, если m5 3, причем п ш-3. Эти приведенные логические выражения могут быть реализованы различным образом при помощи стандартных логических микросхем. На-фиг. 2 представлен один из возможных вариантов. Так, каждый логический узел 41-43 содержит 16 логических элементов 2 И, 44-59,

два логических элемента 3 И, 60 и 63, 20 49 (2 И 53), подключенном к одному

два логических элемента НЕ 62 и 63, два логических элемента 2 И-НЕ 54 и 65, два логических элемента 2 ИЛИ 66 и 67, два логических элемента 3 ИЛИ- НЕ 68 и 69 и два логических элемента 3 ИЛИ 70 и 71. Выходы Мдклогиче- ского узла 41 через усилительно-развязывающий узел 72 связаны с соответствующими управляющими входамиМд ключей 4-7 ;16 и 17.

Канал логического узла 41, предназначенный, например, для формирования управляющего сигнала F 1 (М Д1 ) ключом 4 (или 5), содержит два лоиз входов логического элемента 3 ИЛИ 70 (3 ИЛИ 71) при этом формируется сигнал Q4014 (2 И 53 -Q40,4D,) В состав описываемого канала логиче25 ского узла 41 входят также логические элементы 2 И 50, выход 0}0(2 И 54 - ) которого подключен к входу логического элемента 2И 51 (2И 55), а к второму его входу подключен выход

30 логического элемента 2И-НЕ 64 (2 И-НЕ 65). На выходе логического элемента 2И 51 формируется сигнал Р40 14р3515 (2 И 55 - jQ т) и он подключен

к второму входу логического элемента гических элемента 2И 44 и 45 (46 и 47) 3 ИЛИ 70 (3 ИЛИ 71). На выходе логи- К их входам подключены выходы регист- ческого элемента 3 ИЛИ 70 (3 ИЛИ 71),

к оставшемуся входу которого подключен выход логического элемента 5 И 61 (3 И 60), формируется управляющий

ра 36 так, что, связи между ними определяются логическими выражениями: на выходе логического элемента 2 И

44 - QjQ4 (2 И 46 - 030„), & на вы- 40 сигнал М д а + ВЛВЛ5 + ходе логического элемента 2И 45 - Q,4Ot/2H 47 - Q,4Q1S). Выходы этих элементов подключены к входам логического элемента 3 ИЛИ-НЕ 68 (69),

+ 0,0,4 030 15(3 ИЛИ 71 -М +D.,DaS + Q4Q,403OfJ).

к оставшемуся свободному входу последнего подключен соответствующий выход регистра 36. На выходе логического элемента 3 ИЛИ-НЕ 68 будет при этом сформирован управляющий сигнал, определяемый логическим выражением, 3 ИЛИ-НЕ 68 - М д,- QaQ4 + Q 1 (3 ИЛИ-НЕ 69 - М Л1 Q3Q4 +

+ 5 140 IS О,)

Канал логического узла 41, преддс Третий канал логического узла 41, предназначенный для формирования управляющего сигнала ключом 6 (7), содержит два логических элемента 2 И 56 и 57 (2 И 58 и 59), подклю5Q ченных выходами к входам логического элемента 2 ИЛИ 66 (2 ИЛИ 67), так, что на выходе последнего формируют управляющий сигнал, определяемый логическим выражением М лз + назначенный для формирования управ- ее + Q-iQ it (2 ИЛИ 67 - Ь лз Q 04 + ляющего сигнала ключом 16 (17) вто- , QiQn-) Эти выходы логического узла рой стойки инверторной ячейки 1 и свя- 41 связаны с управляющими выходами занный выходом М д г (М д) через усили- М лз и М лз ключей 6 и 7. Два других тельно-развязьтающий учел 72 с управляю- логических узла 42 и 43 выполнены ана щим входом М..(МЛ2) упомянутого ключа 36 (17), содержит два логических элемента ЗИ 60 и 61 . К их входам ключены выходы S модулятора ширины импульсов и выходы I-K триггеров 38 и 39 таким образом, что связи между ними определяются логическими выражениями: ЗИ 60 - , а на выходе 3 И

61 - D,. После инвертирования логический сигнал с выхода логи- ческого элемента НЕ 62 (НЕ 63 - P,DaS) поступает на вход логического элемента 2 И 49 (2 И 53), другой вход которого подключен к выходу логического элемента 2И 48 (2И 52), где формируется сигнал, определяемый логическим выражением Q4QM (2 И 52 - Q4Q,4). На выходе логического элемента 2 И

из входов логического элемента 3 ИЛИ 70 (3 ИЛИ 71) при этом формируется сигнал Q4014 (2 И 53 -Q40,4D,) В состав описываемого канала логического узла 41 входят также логические элементы 2 И 50, выход 0}0(2 И 54 - ) которого подключен к входу логического элемента 2И 51 (2И 55), а к второму его входу подключен выход

логического элемента 2И-НЕ 64 (2 И-НЕ 65). На выходе логического элемента 2И 51 формируется сигнал Р40 14р3515 (2 И 55 - jQ т) и он подключен

сигнал М д а + ВЛВЛ5 +

+ 0,0,4 030 15(3 ИЛИ 71 -М +D.,DaS + Q4Q,403OfJ).

Третий канал логического узла 41, предназначенный для формирования управляющего сигнала ключом 6 (7), содержит два логических элемента 2 И 56 и 57 (2 И 58 и 59), подключенных выходами к входам логического элемента 2 ИЛИ 66 (2 ИЛИ 67), так, что на выходе последнего формируют управляющий сигнал, определяемый лолопгпю с учетом сдвига на угол управляющих сигналов ключами фаз А, В, С. Логические выражения, определяющие связи между логическими элементами в каждом канале всех трех логических узлов , приведены йыше.

Принцип работы преобразователя поясняется временными диаграммами, Представленными на фиг.З. На этом чертеже представлены: U3 - сигнал t впхида за/датчика 34 частоты, синхронизирующего работу преобразователя, U - сигнал с выхода делителя1 35 частоты, иэт - сигнал S с быхпдз модулятора 37 ширины импуль- Сов 37. Длительность & этого-сигнала, пропорциональная величине 12 , определяет величину выход гого напряжения преобразователя. С выхода регистра 36 получают симметричные импульсы U прямоугольной формы, сдвинутые друг относительно друга на угол ( /15, например, ,

, ° ts на Фиг«3. Каждый из 1-К триггеров (38-40) синхронизирован соответствующим сигналом с выхода регистра 36. При этом выходные сигналы U3j U40 сидвинуты на угол 1Г/30 по отношению к сигналам QA Qti u ft-i соответственно. После осуществления логических операций над полученными последовательностями импульсов на выходах логических элементов 66-7 логических узлов 41-43 получают новые последовательности управляющих импульсов, определяемые приведенными выражениями. Номер каждого логического элемента 44-71 в узле 41, соответствует индексу полученной последовательности импульсов, некоторые из которых представлены н фиг.З. В результате ключи 4-21 преобразователя переключаются в соответствии с разработанным алгоритмом. Регулировочные паузы Ј и дополнительные импульсы при этом вводятся не на всем интервале проводимости О- /Г и ТГ- 2ff а только на определенном участке (U-,c 71 на фиг.З). При симметричной нагрузке преобразователя, соединенной в звезду без нулевого провода, фазное напряжение на нагрузке (при соответ- ствуюшей величине регулировочной паузы- d ) имеет вид Од (фиг.З).

38

Для случая d 0 форма фазного выходного напряжения нагрузки U д приведена на фиг.4. Там же представлена кривая напряжения 1ТЧ на трансформаторе 28.

Представленная на фиг.2 схема логического узла 41 обеспечивает работу преобразователя по фиг.1 на на- грузку, имеющую любой, не заданный заранее, коэффициент мощности cos i/ (угол нагрузки -1Г/2 if41 .Ј ff/2) . В том случае, когда величина cos ограничена, схема управления, обеспе- 5 чивающая неискажаемую форму выходного напряжения, может быть изменена. Так, при работе на нагрузку с -(Iff/20 -е//2± JT/2 управляющее - Ј,игналы М q и М 1 могут иметь форму, % о приведенную на фиг.З а.. Дополнительные переключения на интервале для сигнала М (О- ТГ для сигнала Р) могут быть ограничены только зоной

1Г-ЗЙ72 (О- Г/2) (фиг.5а). При ра- 5 боте на нагрузку, имеющую -(7ТГ/20-о(/2) Ч 11«71Г/20 - о(/2) дополнительных включений в указанных зонах можно вообще не производить (фиг.Зб). В этих случаях схема каналов логического 0 Узла (например, узла 41) имеет вид, представленный на фиг. 6. В первом из рассмотренных случаев один из входов логического элемента 3 И 61 подключен к выходу 05 регистра 46 (фиг. 6э). 5 а сигнал имеет вид. м л Q4Q.MD1D1 + +D,OgS + 04Q1403015.

Во втором случае вместо логического элемента 3 ИЛИ 70 (71) включают логический элемент . Сигнал име- 0 МЯЛ7 „6,0,5 + 04P14Q3Q .

Предлагаемый преобразователь обеспечивает формирование квазнсинусои- далыюго трехфазного напряжения с

5 уменьшенной по сравнению с известным преобразователем величиной коэффициента гармоник К (U) . В диапазоне изменения соотношения чисел витков секций первичных обмоток 22 и 23 1:К, где 1 ,3 4

0 К 41,5 К (U) (при изменяется в пределах 0,068 iKr(U) Я),071. Для сравнения в известном преобразователе Kr(U) 0,094. Таким образом обеспечено улучшение качества выходного напряжения.

5

Формула изобретения

Преобразователь постоянного напряжения в регулируемое трехфазное напряжение,содержащий три мостовые ин- верторные ячейки, каждая из которых выполнена в виде трех подключенных параллельно к входным выводам преобразователя полумостов ключей и выходного трансформатора, первичная обмотка которого первым крайним выводом соединена с выходом первого полумоста ключей с управляющими входами V и

М

„ г

отводом от промежуточной точки с выходом второго полумоста ключей, выполненных в виде транзисторов, шунтированных возвратными диодами и имеющих управляющие входы М.-г и М.-2 , а вторым крайним выводом - с выходом третьего полумоста ключей переменног тока с управляющими входами М ,.

и М

J3

причем вторичные обмотки

выходных трансформаторов трех мостовых инверторных ячеек соединены в звезду и подключены к выходным выводам преобразователя, и блок управления, содержащий последовательно соединенные задатчик частоты, делитель частоты на два, N-каналь- ный регистр с парафазными выходами

От,,,...,0

Nl

О

N

и три одинаково

выполненных логических узла, выходы MJO MJ,,..., f jjMj3 которых соединены с одноименными управляющими входами ключей полумостов, к выходу задатчика частоты подключены также Модулятор ширины импульсов, выходом S подключенный к одним из входов логических узлов, и счетные входы трех 1-К-триггеров, установочные входы которых подключены к соответствующим выходам N-канального регистра, з их парафазные выходы D,, fi/j,.. . ,Ц, D3

подключены к другим входам логических узлов, отличающийся тем, что, с целью повышения качества выходного напряжения за счет уменьшения коэффициента гармоник, ключи первого полумоста выполнены в виде ключей переменного тока, N-каналъ- ный регистр выполнен пятнадцатиканалъ- ным (N 15), упомянутые установочные входы I-К-триггеров подключены так, что

1г Q,,, Ґ-1 0„,

I, Q,. К,

;А

1з QК

1

41 а связи между

входами и выходами логических узлов определяются следующими логическими выражениями

0

5

MJi- MjV

Qft7Q i,3 + Qu, + Q

i + t4

Q-,

м

n

Q f+iQ з+ Q IMS f

Q ,43Q-,4,,pm Dm+1S

0;-f14

D.DnS

+ QuaQi,, Q, Qi+3Q

MJ4

j-H3™mD w+i S

Dm

tn-M

Qi

+

s +

+ Q ,M3 Q tnOi + u

0

M

J3

MJ3 , Q

Qui Ьм

Puts

где i 1, 11, 21 ответственно для j

ит 1,3,5, co- - А, В, С, при

этом, если индекс при Q превышает 15, а индекс, при m превышает 3, то полученное значение уменьшают соответственно на 15 или на 3 с одновременной инверсией данного выхода, причем при необходимости эту операцию повторяют неоднократно.

IHUIIHUUI-Ш

f 5 Ј .1 l . l Й 85

yr/г

№Г.З

U

а)

О

-Л/2

О

Я/2

а)

УГ

Ътг/а.

ДГ

37Г/2

Фиг. 6

| Способ регулирования выходного напряжения трехфазного мостового инвертора | 1974 |

|

SU532162A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления регулируемым по напряжению преобразователем постоянного напряжения в трехфазное | 1986 |

|

SU1471268A1 |

Авторы

Даты

1990-02-07—Публикация

1987-04-02—Подача