Изобретение относится к цифровой вычислительной технике и может быть использовано для получения полного множества решений потоковой задачи в ориентированной сети.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности моделирования узла сети в различных режимах функционирования.

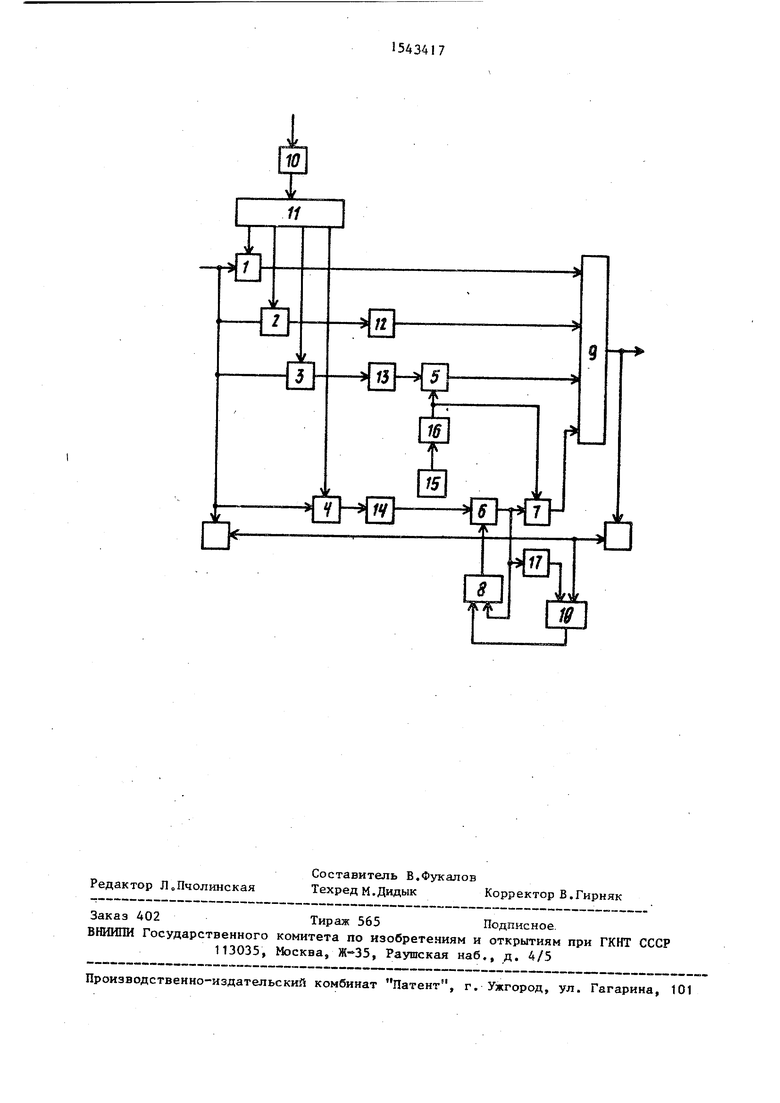

На чертеже приведена схема устройства.

Устройство содержит первый 1 - седьмой 7 элементы И, триггер 8, первый элемент .ИЛИ 9, регистр 10 памяти, дешифратор 11, первый 12, второй 13 и третий 14 элементы, задержки, генератор 15 случайных импульсов, элемент НЕ 16, четвертый элемент 17 задержки и второй элемент ИЛИ 18.

Устройство для моделирования узла сети работает следующим образом.

Перед началом работы устройства через его установочный вход поступает сигнал, который устанавливает триггер 8 в состояние 1, разрешая прохождение информационных сигналов через элемент И 5. Затем через управляющий вход устройства на вход регистра 10 поступает код, определяющий один из четырех возможных режимов функционирования узла сети: информационные сигналы без задержки и без изменений проходят через узел сети; информационные сигналы с задержкой, но без изменений проходят через узел сети; информационные сигналы с за- держксй и с потерями из-за воздействия на них потока ошибок проходят через узел сети; информационные сигнасд

4

со

и&ь -4

лы с задержкой и с потерями (из-за воздействия на них потока ошибок и потерь в очереди на обслуживание) проходят через узел сети.

С выхода регистра 10 код управления поступает на вход дешифратора 11, который разрешает прохождение информационных сигналов через один из четырех соответствующих элементов И 1 - 4 (т.е. задается требуемый режим функционирования устройства).

Входные информационные сигналы (в виде импульсов) через информационный вход устройства поступают на ин- формационные входы этих элементов И. I

Если открыт элемент И 1, то входные информационные сигналы поступают на информационный выход устройства через элемент ИЛИ 9; если открыт элемент И 2 - через элемент 12 задержки и элемент ИЛИ 9, если открыт элемент И 3 - через элемент 13 задержки, элемент И 5 и элемент ИЛИ 9 (в случайные моменты времени появления импульсов на управляющем входе элемента И 5 запрещается прохождение сигналов через него, в результате моделируется процесс информационных потерь).

Если открыт элемент И 4, то вход- цые информационные сигналы поступают н;а информационный выход устройства элемент задержки 14, элементы И 6, И 7 и ИЛИ 9. Элемент И 6, эле™ кент 17 задержки, элемент ИЛИ 18 и триггер 8 предназначены для моделирования информационных потерь в очереди узла сети. Импульс с выхода эле- м|ента И 6, поступающий на вход триггера 7, устанавливает триггер 7 в состояние О, чем запрещается прохождение сигналов через элемент И 6 на время задержки сигнала элементом

17задержки. Импульс с выхода элемента 17 задержки через элемент ИЛИ

18вновь устанавливав т триггер 8в состояние 1,вновь разрешаяпрохождение сигналачерез элементИ 6.В случай мйе моменты времени появления имлуль сов на выходе генератора 15 запрещается прохождение сигналов через элмент И 7. В результате моделируется процесс информационных потерь(из-за воздействия на моделируемый процесс потока ошибок)«

0

5

0

5

0

5

0

5

Формула изобретения Устройство для моделирования узла сетиа содержащее регистр памяти, дешифратор, первый элемент ИЛИ, выход которого является информационным выходом устройства, семь элементов И, информационные входы регистра памяти являются входом задания режима работы устройства, а информационные выходы регистра памяти подключены соответственно к входам дешифратора, с первого по четвертый выходы которого соединены с первыми входами соответственно с первого по четвертый элементов И, вторые входы с первого по четвертый элементов И объединены и являются информационным входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет моделирования различных режимов работы узла сети, оно дополнительно содержит второй элемент ИЛИ, четыре элемента задержки, генератор случайных импульсов и элемент НЕ, причем выход первого элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого через первый элемент задержки подключен к выходу второго элемента И, выход третьего элемента И через второй элемент задержки соединен с первым входом пятого элемента И, выход которого подключен к третьему входу первого элемента ИЛИ, выход четвертого элемента И через третий элемент задержки соединен с первым входом шестого элемента И, выход которого подключен к первому входу седьмого элемента И, выход которого соединен с четвертым входом первого элемента ИЛИ, выход шестого элемента И подключен к нулевому входу триггера и входу четвертого элемента задержки, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого является установочным входом устройства, а выход второго элемента ИЛИ подключен к единичному входу триггера, прямой выход которого соединен с вторым входом шестого элемента И, выход генератора случайных импульсов подключен к входу элемента НЕ, выход которого соединен с вторыми входами пятого и седьмого элементов И,

у

7

| название | год | авторы | номер документа |

|---|---|---|---|

| Модель дуги сети | 1987 |

|

SU1499372A1 |

| Устройство для моделирования систем массового обслуживания | 1989 |

|

SU1783539A1 |

| Устройство для моделирования сети коммутации каналов | 1985 |

|

SU1287173A1 |

| Устройство для моделирования систем передачи данных | 1983 |

|

SU1151983A1 |

| Устройство для моделирования многоканальных систем массового обслуживания | 1989 |

|

SU1681308A1 |

| СИСТЕМА УПРАВЛЕНИЯ РАСПРЕДЕЛЕНИЕМ ДАННЫХ В СЕТИ ИНФОРМАЦИОННО-АНАЛИТИЧЕСКОГО ЦЕНТРА | 2005 |

|

RU2291481C1 |

| Устройство для определения длиннейшего пути в сетях | 1986 |

|

SU1339581A1 |

| Устройство для моделирования систем передачи и обработки данных | 1983 |

|

SU1150629A1 |

| Устройство для моделирования топологии сетей | 1982 |

|

SU1024930A1 |

| Устройство для моделирования отказов | 1986 |

|

SU1381537A1 |

Изобретение относится к цифровой вычислительной технике. Цель изобретения - расширение функциональных возможностей за счет различных режимов функционирования узла сети. Устройство для моделирования узла сети содержит семь элементов И, четыре элемента задержки, два элемента ИЛИ, регистр памяти, триггер, дешифратор, элемент НЕ, генератор случайных импульсов. Устройство позволяет моделировать работу узла сети в режиме без искажения информации, режиме без искажений и с задержкой информации, режиме с задержкой информации и ее потерями, режиме с задержкой информации, ее потерями и ожиданием обработки информации. 1 ил.

| Устройство для моделирования системы сбора и обработки данных | 1983 |

|

SU1115059A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля датчика информации | 1987 |

|

SU1465889A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-15—Публикация

1987-12-02—Подача