Фиг.1

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники.

Цель изобретения - повышение надежности функционирования путем обеспечения возможности корректного выбора величин длительности и периода выходных импульсов.

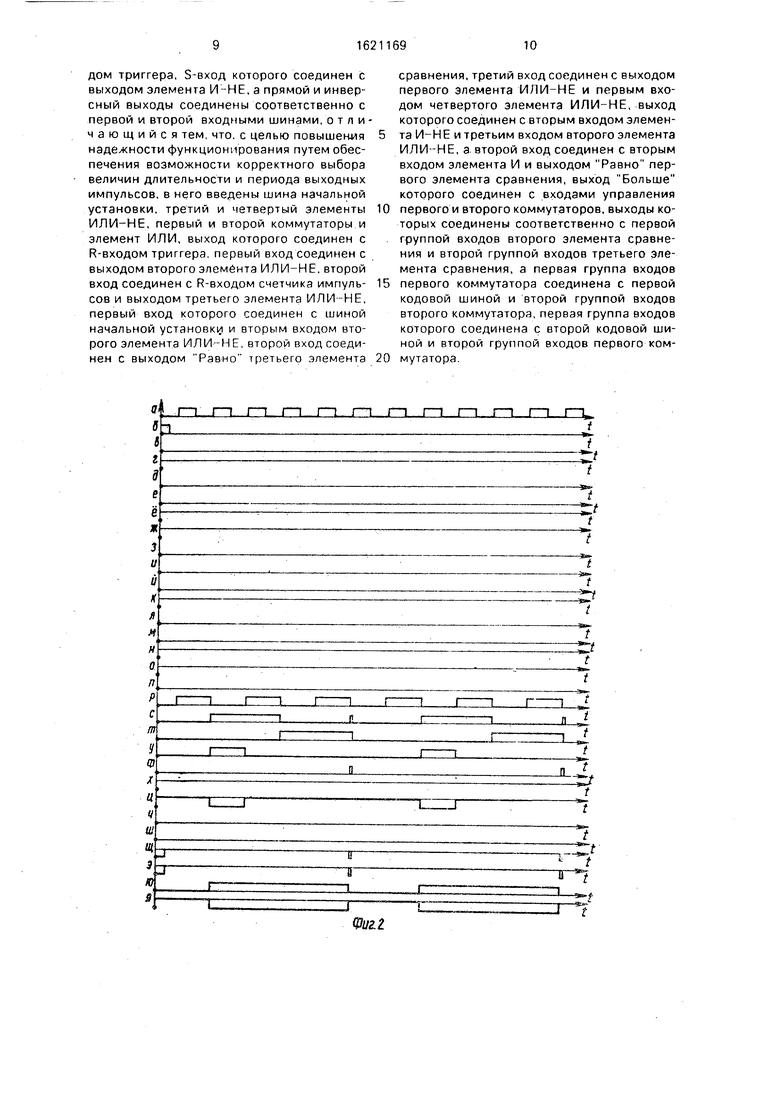

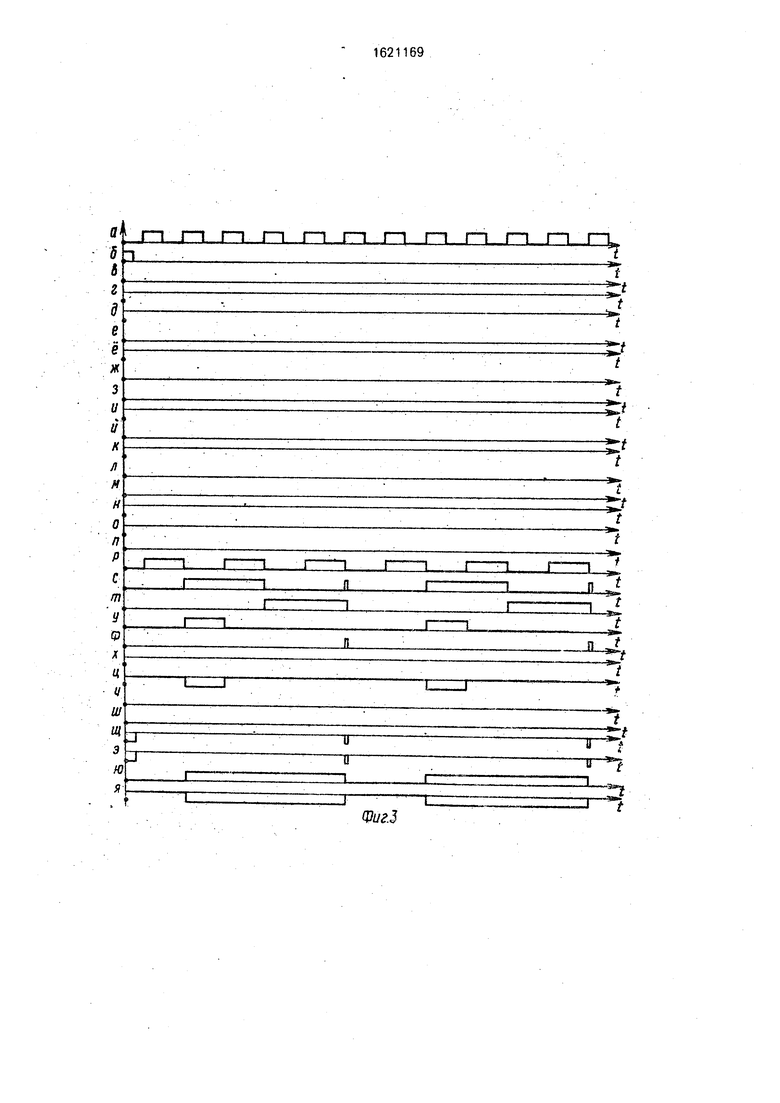

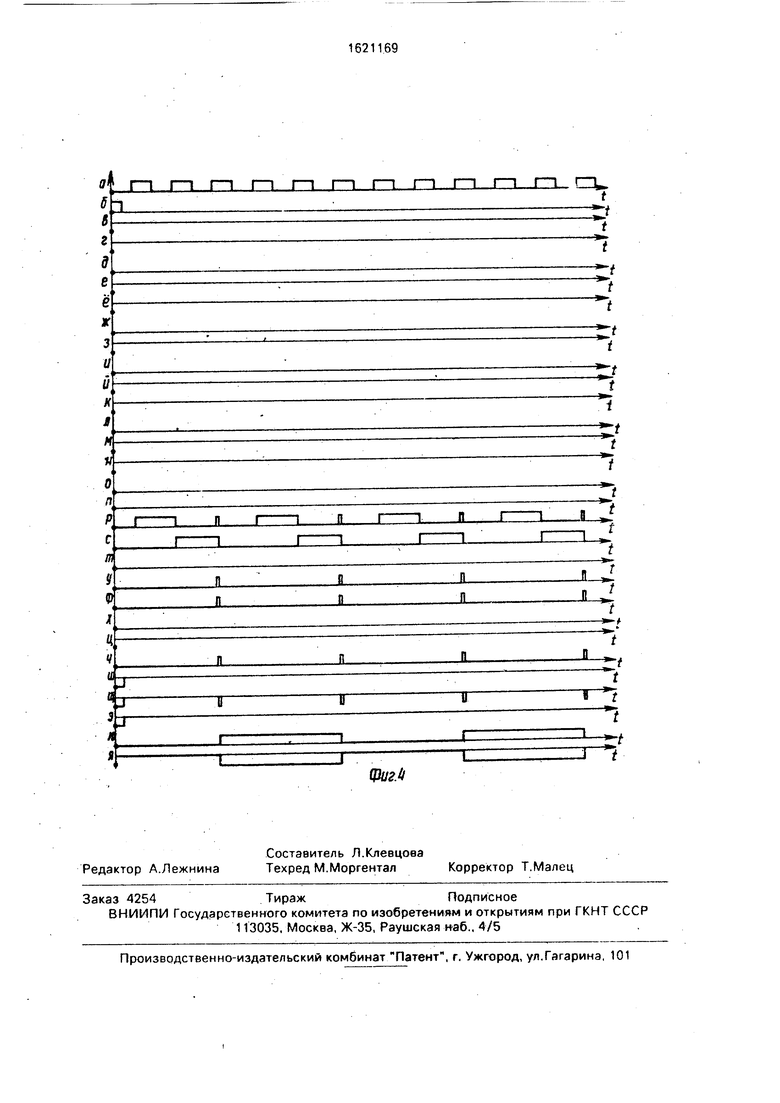

На фиг.1 представлена структурная электрическая схема управляемого делите- ля частоты; на фиг.2-4 - временные диаграммы, поясняющие его работу.

Управляемый делитель частоты содержит первую и вторую кодовые шины 1 и 2, которые соединены соответственно с первой и второй группами входов первого элемента 3 сравнения, второй элемент 4 сравнения, выход Равно которого соединен с первым входом элемента И-НЕ 5, первая группа входов соединена с соответствующими входами первого элемента ИЛ И-НЕ 6, выход которого соединен с первым входом второго элемента ИЛИ-НЕ 7, счетчик 8 импульсов, счетный вход которого соединен с входной шиной 9, разрядные выходы соединены с второй группой входов второго элемента 4 сравнения и первой группой входов третьего элемента 10 сравнения, выход Равно которого соединен с первым входом элемента И 11, выход которого соединен со счетным входом триггера 12, S-вход которого соединен с выходом элемента И-НЕ 5, а прямой и инверсный выходы соединены соответственно с первой и второй выходными шинами 13 и 14. Делитель содержит также шину 15 начальной установки, третий и четвертый элементы ИЛИ-НЕ 16 и 17, первый и второй коммутаторы 18 и 19 и элемент ИЛИ 20, выход которого соединен с R-входом триггера 12, первый вход - с выходом второго элемента ИЛИ-НЕ 7, второй вход - с R-входом счетчика 8 импульсов и выходом третьего элемента ИЛИ-НЕ 16, первый вход которого соединен с шиной 15 начальной установки и вторым входом второго элемента ИЛИ-НЕ 7, второй вход-с выходом Равно третьего элемента 10 сравнения, третий вход - с выходом первого элемента ИЛИ- НЕ 6 с первым входом четвертого элемента ИЛИ-НЕ 17, выход которого соединен с вторым входом элемента И-НЕ 5 и третьим входом второго элемента ИЛИ-НЕ 7, а второй вход - с вторым входом элемента И 11 и выходом Равно первого элемента 3 сравнения, выход Больше которого соединен с входами управления первого и второго коммутаторов 18 и 19,выходы которых соединены соответственно с первой группой входов

второго элемента 4 сравнения и второй группой входов третьего элемента 10 срав-. нения, а первая группа входов первого коммутатора 18 соединена с первой кодовой шиной 1 и второй группой входов второго коммутатора 19, первая группа входов которого соединена с второй кодовой шиной 2 и второй группой входов первого коммутатора 18

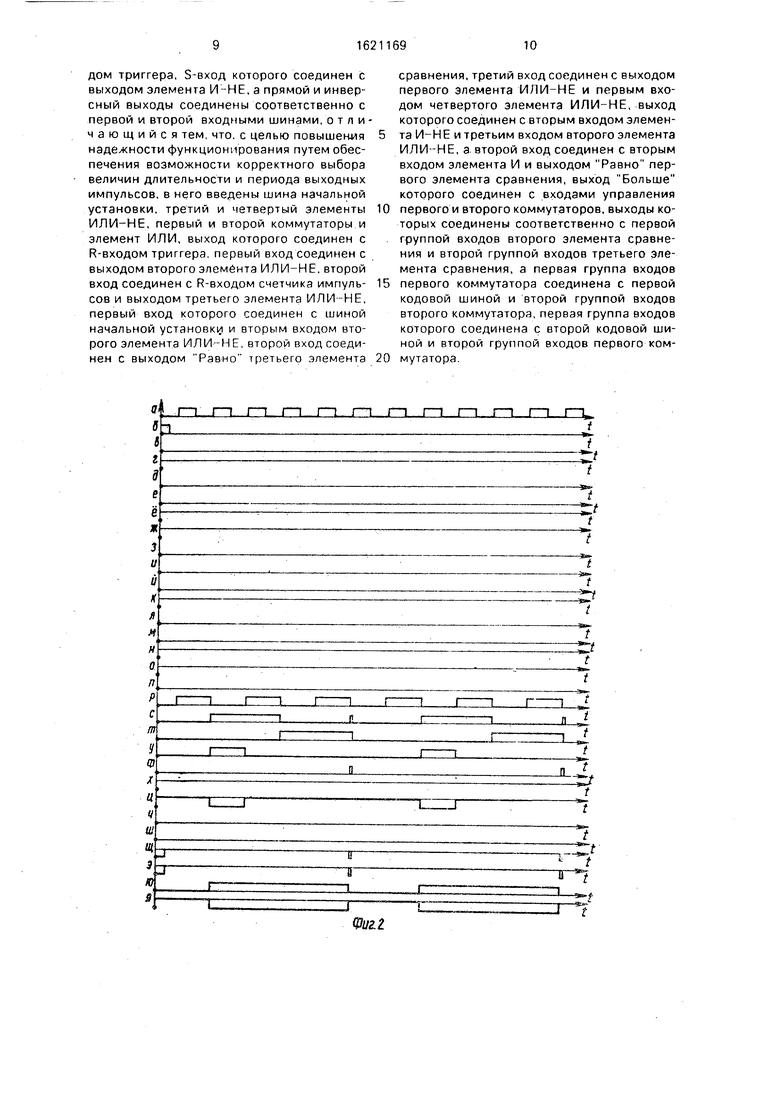

При составлении временных диаграмм

было принято, что разрядность кодовых шин 1 и 2. коммутаторов 18 и 19, элементов 3,4 и 10 сравнения и счетчика 8 равна трем.

На временных диаграммах фиг,2-4

обозначены: а - сигнал на шине 9; б - сигнал ча шине 15; в,г,д - сигналы на кодовой шине

1(в - младший, д - старший разряды); е.ё.ж - сигналы на кодовой шине 2 (е - младший,

ж - старший разряды), з,и - сигналы на выходах Равно1 и Больше элемента 3 сравнения соответственно, и,к,л - сигналы на выходах коммутатора 18 (и - младший, л - старший разряды), м,н,о - сигналы на

выходах коммутатора 19 (м - младший, о - старший разряды), п - сигнал на выходе элемента ИЛИ-НЕ 6; р,с,т - сигналы на выходах счетчика 8 (р - младший, т - старший разряды); у,ф - сигналы на выходах элементов 4 и 10 сравнения; х,ч,ш,щ,э - сигналы нз выходах элементов ИЛИ-НЕ 17, И-НЕ 5, И 11, ИЛИ-НЕ 7 и 16 и ИЛИ 20 соответственно, ю - сигнал на ишне 13, я - сигнал на шине 14 На фиг 2 принято, что на кодовых

шинах 1 и 2 заданы коды соответственно чисел 2 и 6; на фиг.З - на кодовых шиках 1 и

2заданы коды соответственно чисел 6 и 2, на фиг 4 - на кодовых шинах 1 и 2 заданы коды числа 3

Управляемый делитель частоты (УДЧ)

работает следующий образом

В качестве признака, по которому устройство осуществляет выбор кода длительности и кода периода следования выходных

импульсов, выступает величина чиспового эквивалента каждого из двух кодов При этом алгоритм функционирования устройства состоит из следующих фаз:

1. Сравнение величин заданных программирующих -,o,tiQB между собой;

2 Если величины исходных кодоз не равны, то выбор кода, имеющего минимальное значение, в ПРОТИВНОМ случае - выбор

любого из кодов

3.Сравнение выбранного значения с нулевым значением,

4.При положительном результате сравнения запрет работы устройства, при отри- цателочом- инициала г ция рабочего цикла

и формирование выходного импульса заданной длительности;

5. По окончании формирования выходного импульса выбор второго из программирующих кодов и продолжение работы по формированию заданного периода следования выходного сигнала.

Выбранный алгоритм функционирования УДЧ исключает возможность некорректного программного обращения к нему по кодовым шинам, поскольку в результате селекции программирующих кодов по заданному признаку минимальной из поступивших кодов (независимо от того на какой из кодовых шин он находится) трактуется УДЧ как код длительности выходного импульса, а максимальный код - как код периода следования выходных импульсов Подача на данное устройство одного или одновременно двух нулевых кодов может рассматриваться как преднамеренный программный запрет его работы,

После включения УДЧ должен быть установлен в исходное состояние подачей положительного импульса на шину 15 При этом на выходах элементов ИЛИ -НЕ 7 и 16 и на выходе элемента ИЛИ 20 во время действия этого импульса имеется уровень О, который устанавливает в О все разряды счетчика 8 импульсов и триггер 12

В исходном состоянии УДЧ тактовые импульсы на шину 9 не поступают на кодовых шинах 1 и 2 заданы произвольные двоичные коды, счетчик 8 импупьсов и триггер 12 установлены в О на шине 15 имеется уровень О

Пусть в исходном состоянии на кодовых шинах 1 и 2 заданы нулевые коды В этом случае на выходе Равно элемента 3 сравнения имеется уровень 1, который формирует уровни О и 1 на выходах соответственно элементов ИЛИ- НЕ 17 и 5, на выходах коммутатора 18 и 19 имеются нулевые коды; на выходе элемента ИЛИ-НЕ 6, выходах Равно элементов 4 и 10 сравнения и выходе элемента И 11 действуют уровни 1, а на выходах элементов ИЛИ- НЕ 7 и 16 и на выходе элемента ИЛИ 20 - уровни О. Подача тактовых импульсов в этом режиме на шину 9 не приводит к изменению состояния УДЧ, поскольку счетчик 8 импульсов и триггер 12 блокированы по их R-входам.

Пусть в исходном состоянии на кодовой шине 1,задан нулевой код, а на кодовой шине 2 - код, отличный от нулевого. В этом случае на обоих выходах элемента 3 сравнения действуют уровни О, на выходы коммутатора 18 проходит код с кодовой шины 1, на выходы коммутатора 19 проходит код

с кодовой шины 2 (коммутаторы 18 и 19 при уровне О на их входах управления пропускают на свои выходы код с первой группы входов, а при уровне 1 - код второй группы

входов); на выходе элемента ИЛИ-НЕ 6, на выходе Разно элемента 4 сравнения и на выходе элемента И-НЕ 5 имеются уровни 1, а на выходе Равно элемента 10 сравнения, на выходе элемента ИЛИ-НЕ 17, на

выходе элемента И 11 и на выходах элементов ИЛИ-НЕ 7 и 16 и ИЛИ 20 действуют уровни О. Подача тактовых импульсов в этом режиме на шину 9 не приводит к изменению состояния УДЧ, поскольку счетчик 8

импульсов и триггер 12 блокированы по их R-входам.

Пусть в исходном состоянии на кодовой шине 1 задан код, отличный от нулевого, а на кодовой шине 2 - нулевой код. В этом

случае на выходе Больше элемента 3 сравнения действует уровень 1, на выходы коммутаторов 18 и 19 проходят коды соответственно с кодовых шин 2 и 1; на выходе элемента ИЛИ -НЕ 6, на выходе Равно элемента 4 сравнения и на выходе элемента И-НЕ 5 имеются уровни 1, а на выходе Равно элемента 10 сравнения, на выходах элементов ИЛИ- НЕ 17 и И 11 и на выходах элементов ИЛИ НЕ 7 и 16 и ИЛИ 20 действуют уровни О Подача тактовых импульсов в стом режиме и ч шину Ј тачже не приводит к изменению состояния УДЧ поскольку счетчик 8 ммпульсов м три (ер 12 блокированы по их R-ьходам.

ЗЕ

Таким образом, если в программного обращения к УДЧ хотя бы оцмн из программирующих КОДОР, заданных на кодовых шинах 1 i. 2, имеет нулевое значение, то УДЧ находится в исходном состоя0 нии независимо от наличия или отсутствия тактовых импульсов на шине 9 Следовательно, подобный режим является режимом программного запрета работы УДЧ.

Пусть в исходном состоянии на кодовых

5 шинах 1 и 2 заданы коды, отличные от нулевых, причем значение первого из них меньше значения второго (фиг.2) В этом случае на обоих выходах элемента 3 сравнения имеются уровни О, на выходы коммутатора

0 18 проходит коде кодовой шины 1, на выходы коммутатора 19 - код с кодовой шины 2; на выходе элемента ИЛИ-НЕ 6, на выходах Равно элементов 4 и 10 сравнения, на выходах элементов И 11 и ИПИ-НЕ 7 установ5 лены уровни О, а на выходах элементов И-НЕ 5, ИЛИ-НЕ 17 и 16 и ИЛИ 20-уровни 1. После подачи тактовых импульсов на шину 9 счетчик 8 импульсов осуществляет их пересчет. Когда состояние счетчика 8 импульсов становится равным значению кода,

имеющегося на выходах коммутатора 18, на выходе Равно элемента 4 сравнения и на выходе элемента И-НЕ 5 последовательно формируются уровни 1 и О соответственно, что вызывает переключение в 1 триггера 12 и изменение состояния шин 13 и 14, на которых формируются передние фронты выходных импульсов, Под действием следующего тактового импульса состояние счетчика 8 импульсов увеличивается на единицу, вследствии чего на выходе Равно элемента 4 сравнения устанавливается уровень О, а на выходе элемента И-НЕ 5 формируется уровень 1, который переводит триггер 12 в режим хранения предыдущего состояния. Далее счетчик 8 импульсов продолжает пересчет тактовых импульсов до тех пор, пока его состояние не станет равным величине кода, имеющегося на выходах коммутатора 19 При этом на выходе Равно элемента 10 сравнения формирует ся уровень 1, а на выходах элементов ИЛИ-НЕ 16 и ИЛИ 20 - уровни 0 , что вызывает сброс в О всех разрядов счетчика 8 импульсов, триггера 12 и возврат УДЧ в исходное состояние. На этом иикл работы УДЧ завершен Если тактовые мпугь- сы продолжают поступать НА шину 9, to дальнейшая работа УДЧ осуществляется аналогично.

Пусть в исходном сое гоянии на кодовых шинах 1 и 2 заданы коды, отличные от нулевых, причем значение первого из них больше значения второго {фиг 3) В этом случае на выходе Больше элемента 3 сравнения имеется уровень 1, что обеспечивает прохождение на выходы коммутаторов 18 кодов соответственно с кодовых шин 2 и 1 При этом на выходе элемента ИЛИ-НЕ 6, на выходах Равно элементов 4 и 10 сравнения, на выходах элементов 14 11 и ИЛИ-НЕ 7 установлены уровни О, а на выходах эле ментов И-НЕ 5, ИЛИ-НЕ 17 и 16 и ИЛИ 20 действуют уровни 1. После подачи тактовых импульсов на шину 9 функционирование УДЧ осуществляется аналогично описанному в предыдущем режиме работы

Таким образом, если в результ&ге программного обращения к УДЧ на кодовых шинах 1 и 2 заданы коды, от нулевых и имеющие различную величину, то УДЧ производит селективный выЬср кодов длительности и периода следования выходных импульсов При этом минимальный из прс граммирующих кодов приминается УДЧ за код длительности, а максимальный - за код периода, независимо от того на какой из кодовых шин 1 и 2 установлен каждый из кодов

Пусть в исходном состоянии УДЧ на ко- доьых шинах 1 и 2 заданы коды равные по . величине и отличные от нулевых (фиг 4) В этом случае на выходе Равно элемента 3

сравнения имеется уровень 1, на выходах коммутаторов 18 и 19 установлен один и тот же код; на выходе элемента ИЛИ-НЕ 6, на выходах Равно элементов 4 и 10 сравнения и на выходах элементов ИЛИ-НЕ 17 и И

11 действует уровень О, а на выходах элементов И-НЕ 5, ИЛИ-НЕ 7 и 16 и ИЛИ 20 уровень 1. После подачи тактовых импульсов на шину 9 счетчик 8 импульсов осуществляв их пересчет до rex пор, пока его

состояние не станет равным величине кода, имеющегося на выходах коммугатооов 18 и 19 При этом на выходах Равно элементов } и 10 сравнения формируется уровень 1, что вызывает формирование уровней 1 и

0 на выходах элементов И 11 и ИЛИ-НЕ 16 В результате этого происходит переключение по счетному входу в 1 триггера 12 и сброс по R-входу в О всех разрядов счетчика 8 импульсов Это приводит к формироваьи о уровней 0 на выходах Равно элементов 4 и 10 сравнения и элемента И 11 и уровня 1 на виходе элемен а ИЛИ-НЕ 15 Дагьнеишая работа УДЧ осуществляет ия налогично с IBM отличием что последуюшие переключения триггера 12 по его счетному входу проис одят поочередно в противоположные состояния

Та к образом если L результате про- фгммного обращения к ДЧ на кодовых

чинал 1 и ° заданы коды равные по величина v огли ч jie /i нулевых УДЧ г ьоеходит в режим формирования выходного сигнала по сумме про рсэммиоующих кодоь при этом он формирует выходной сигнал типа меа ндр

Формула изобретения / раоляемо й депитель частоты, содержащий перБу ю v вторую кодовые шин коьрые соединены соответственно с пеовой и второй группами входов первого элемента спавнения второй элемент сравнения выход Рззно кото )ого „оедииен с первым входом олрмома И-НЕ первая группа еходо в соединена с соответствующими входами первого цемента ИЛ /-НЕ выход которого соеп чеч с первым входом второго элемент 1/ЛИ НС . ч и к импульсов, счетный йход коюрого соединен с входной

шкчой, разрядное выходы сое, йены с второй группой входов второго элемента сравнения v, первой группой входов третьего элемента сравнения, БЫ/-ОД Равно кото рого соединен с i входом элемента И, в1. од /от орого соединен со счетч, м входом триггера, S-вход которого соединен с выходом элемента И-НЕ, а прямой и инверсный выходы соединены соответственно с первой и второй входными шинами, отличающийся тем, что. с целью повышения надежности функционирования путем обеспечения возможности корректного выбора величин длительности и периода выходных импульсов, в него введены шина начальной установки, третий и четвертый элементы ИЛИ-НЕ, первый и второй коммутаторы и элемент ИЛИ, выход которого соединен с R-входом триггера, первый вход соединен с выходом второго элемента ИЛИ-НЕ. второй вход соединен с R-входом счетчика импульсов и выходом третьего элемента ИЛИ-НЕ, первый вход которого соединен с шиной начальной установки и вторым входом второго элемента ИЛИ-НЕ, второй вход соединен с выходом Равно третьего элемента

сравнения, третий вход соединен с выходом первого элемента ИЛИ-НЕ и первым входом четвертого элемента ИЛИ-НЕ, выход которого соединен с вторым входом элемента И-НЕ и третьим входом второго элемента ИЛИ-НЕ, а второй вход соединен с вторым входом элемента И и выходом Равно первого элемента сравнения, выход Больше которого соединен с входами управления

первого и второго коммутаторов, выходы которых соединены соответственно с первой группой входов второго элемента сравнения и второй группой входов третьего элемента сравнения, а первая группа входов

первого коммутатора соединена с первой кодовой шиной и второй группой входов второго коммутатора, первая группа входов которого соединена с второй кодовой шиной и второй группой входов первого коммутатора

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый делитель частоты | 1989 |

|

SU1704281A1 |

| Управляемый делитель частоты | 1989 |

|

SU1691955A1 |

| Управляемый делитель частоты | 1988 |

|

SU1517131A1 |

| Управляемый делитель частоты | 1988 |

|

SU1598175A2 |

| Управляемый делитель частоты | 1986 |

|

SU1387193A1 |

| Устройство для регистрации положения поршней в оппозитном дизельном двигателе | 1987 |

|

SU1481615A1 |

| Управляемый делитель частоты | 1988 |

|

SU1499492A1 |

| КОРРЕЛЯЦИОННАЯ ИЗМЕРИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2007753C1 |

| Делитель частоты следования импульсов с регулируемой длительностью импульсов | 1987 |

|

SU1499490A1 |

| Преобразователь серии импульсов в прямоугольный импульс | 1986 |

|

SU1422382A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники. Цель изобретения - повышение надежности функционирования за счет обеспечения возможности корректного выбора величин длительности и периода выходных импульсов - достигается путем введения в делитель элементов ИЛИ-НЕ 16,17, коммутаторов 18,19, элемента ИЛИ 20 и образования новых функциональных связей. Кроме того, делитель содержит элементы сравнений 3,4,10, элемент И-НЕ 5. элементы ИЛИ- НЕ 6,7, счетчик 8 импульсов, элемент И 11, триггер 12, шины 1,2,9,13.14,15: первую кодовую, вторую кодовую, входную, перёую выходную, вторую выходную, начальной установки соответственно. 4 ил.

(7.

ВЬ t

I

д

е

ё ж

з и

и

н

о п р с т

Ч Ф / U Ч

ш щ

:г т

ю

.Г1 -П.. П.

±ч

/

t

-Ј,

t t

JC1

J.

л J

t

-t

т

Фиг. 2.

-«да г

e

ж

tf л

л

IT

T

T-7

П

т

| Делитель частоты следования импульсов с регулируемой длительностью импульсов | 1986 |

|

SU1403366A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Делитель частоты с дискретной регулировкой длительности импульсов | 1984 |

|

SU1226662A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-01-15—Публикация

1988-11-15—Подача