С 4 N| 00 vj

ч|

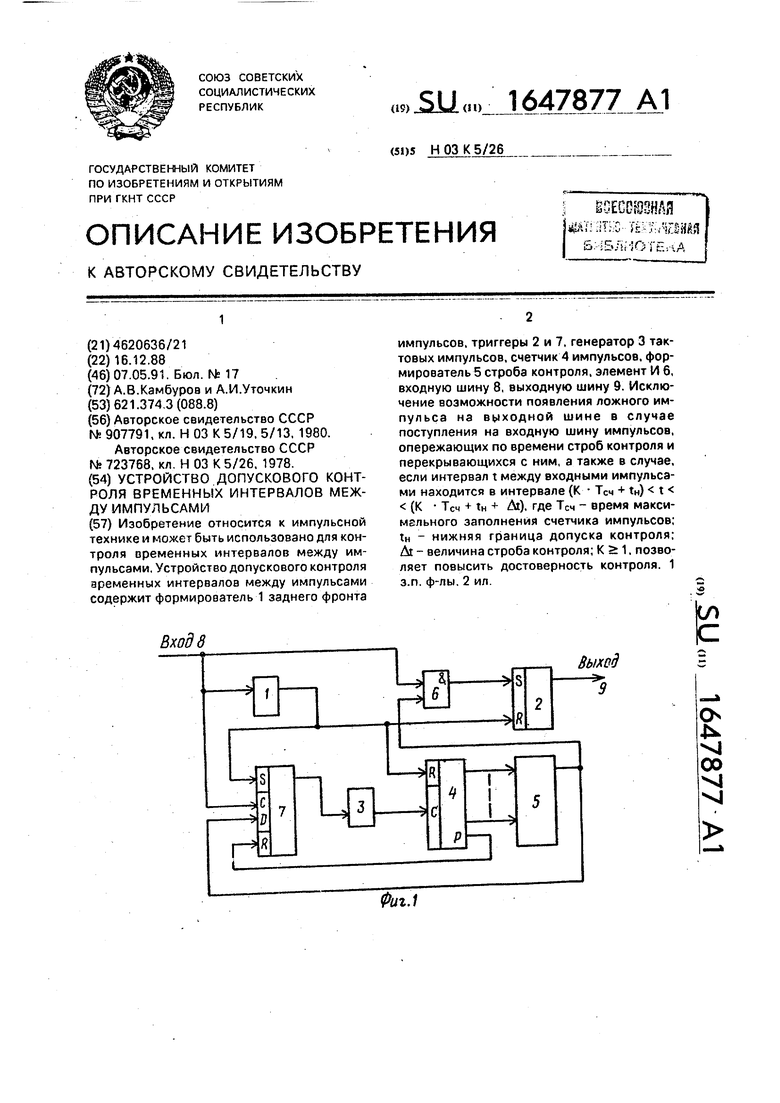

Изобретение относится к импульсной технике и может быть использовано для контроля временных интервалов между импульсами.

Цель изобретения - повышение достоверности контроля за счет исключения возможности появления ложного импульса на выходной шине в случае поступления на входную шину испульсов, опережающих по времени строб контроля и перекрывающихся с ним, а также в случае, если интервал между входными импульсами t находится в интервале (К ТСч + tn) . t (К -104 + 111 + + At), где ТСч- время максимального заполнения счетчика импульсов, in - нижняя граница допуска контроля, At- величина строба контроля, К 1.

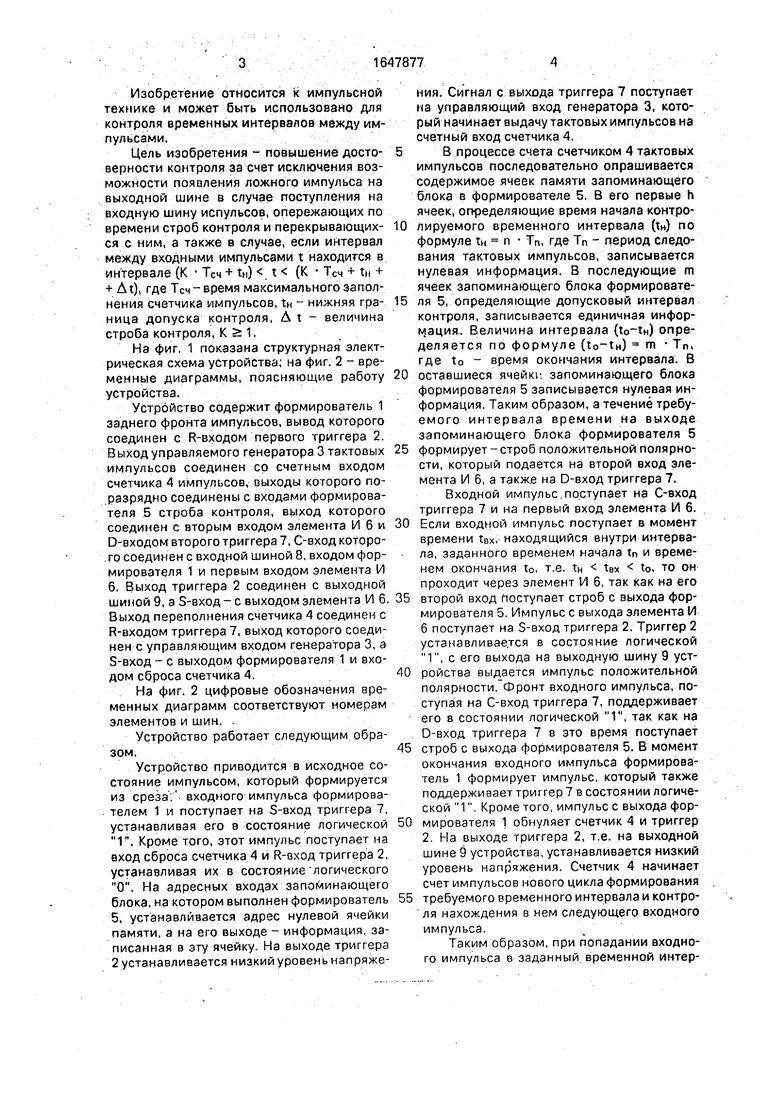

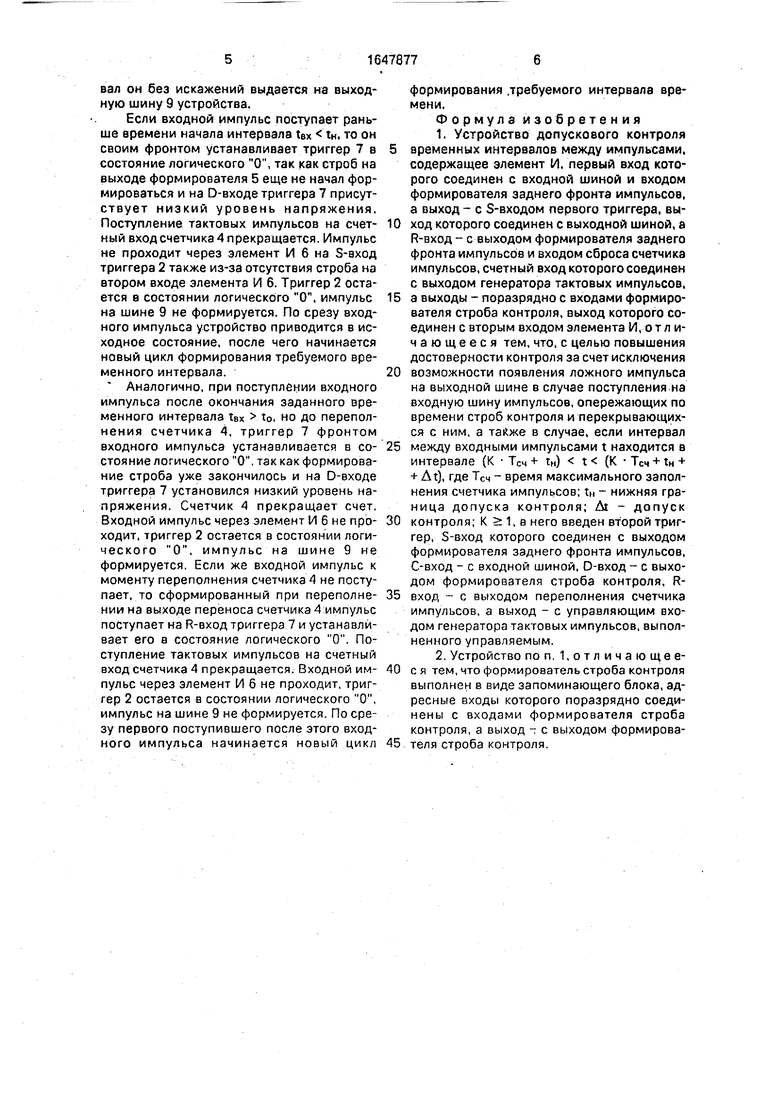

На фиг. 1 показана структурная электрическая схема устройства; на фиг, 2 - временные диаграммы, поясняющие работу устройства.

Устройство содержит формирователь 1 заднего фронта импульсов, вывод которого соединен с R-входом первого триггера 2. Выход управляемого генератора 3 тактовых импульсов соединен со счетным входом счетчика 4 импульсов, выходы которого поразрядно соединены с входами формирователя 5 строба контроля, выход которого соединен с вторым входом элемента И б и D-входом второго триггера 7, С-вход которого соединен с входной шиной 8, входом формирователя 1 и первым входом элемента И 6. Выход триггера 2 соединен с выходной шиной 9, а S-вход - с выходом элемента И 6. Выход переполнения счетчика 4 соединен с R-входом триггера 7, выход которого соединен с управляющим входом генератора 3, а S-вход - с выходом формирователя 1 и входом сброса счетчика 4,

На фиг. 2 цифровые обозначения временных диаграмм соответствуют номерам элементов и шин. .

Устройство работает следующим образом.

Устройство приводится в исходное состояние импульсом, который формируется из среза. входного импульса формирователем 1 и поступает на S-вход триггера 7, устанавливая его в состояние логической 1. Кроме того, этот импульс поступает на вход сброса счетчика 4 и R-оход триггера 2, устанавливая их в состояние логического О. На адресных входах запоминающего блока, на котором выполнен формирователь 5, устанавливается адрес нулевой ячейки памяти, а на его выходе - информация, записанная в эту ячейку. На выходе триггера 2устанавливается низкийуровеньнапряжения. Сигнал с выхода триггера 7 поступает на управляющий вход генератора 3, который начинает выдачу тактовых импульсов на счетный вход счетчика 4.

В процессе счета счетчиком 4 тактовых

импульсов последовательно опрашивается содержимое ячеек памяти запоминающего блока в формирователе 5. В его первые h ячеек, определяющие время начала контролируемого временного интервала (т.н) по формуле tn п Тп, где Тп - период следования тактовых импульсов, записывается нулевая информация. В последующие m ячеек запоминающего блока формирователя 5, определяющие допусковый интервал контроля, записывается единичная информация. Величина интервала (t0-tH) определяется по формуле () m Тп, где to - время окончания интервала. В

оставшиеся ячейкг запоминающего блока формирователя 5 записывается нулевая информация. Таким образом, а течение требуемого интервала времени на выходе запоминающего блока формирователя 5

формирует - строб положительной полярности, который подается на второй вход элемента И 6, а также на D-вход триггера 7.

Входной импульс поступает на С-вход триггера 7 и на первый вход элемента И 6.

Если входной импульс поступает в момент времени tnx, находящийся внутри интервала, заданного временем начала tr и временем окончания to, т.е. tH tB to, то он проходит через элемент 1/1 б, так как на его

второй вход поступает строб с выхода формирователя 5. Импульс с выхода элемента И б поступает на S-вход триггера 2. Триггер 2 устанавливается в состояние логической 1, с его выхода на выходную шину 9 устройства выдается импульс положительной полярности. Фронт входного импульса, поступая на С-вход триггера 7, поддерживает его в состоянии логической 1, так как на D-вход триггера 7 в это время поступает

строб с выхода формирователя 5. В момент окончания входного импульса формирователь 1 формирует импульс, который также поддерживает триггер 7 в состоянии логической 1. Кроме того, импульс с выхода формирователя 1 обнуляет счетчик 4 и триггер 2. На выходе триггера 2, т.е. на выходной шине 9 устройства, устанавливается низкий уровень напряжения. Счетчик 4 начинает счет импульсов нового цикла формирования

требуемого временного интервала и контроля нахождения в нем следующего входного импульса.

Таким образом, при попадании входного импульса в заданный временной интервал он без искажений выдается на выходную шину 9 устройства.

Если входной импульс поступает раньше времени начала интервала tax tH, то он своим фронтом устанавливает триггер 7 в состояние логического О, так как строб на выходе формирователя 5 еще не начал формироваться и на D-входе триггера 7 присутствует низкий уровень напряжения. Поступление тактовых импульсов на счетный вход счетчика 4 прекращается. Импульс не проходит через элемент И 6 на S-вход триггера 2 также из-за отсутствия строба на втором входе элемента И б. Триггер 2 остается в состоянии логического О, импульс на шине 9 не формируется. По срезу входного импульса устройство приводится в исходное состояние, после чего начинается новый цикл формирования требуемого временного интервала.

Аналогично, при поступлении входного импульса после окончания заданного временного интервала tex t0, но до переполнения счетчика 4, триггер 7 фронтом входного импульса устанавливается в состояние логического О, так как формирование строба уже закончилось и на D-входе триггера 7 установился низкий уровень напряжения. Счетчик 4 прекращает счет. Входной импульс через элемент И 6 не проходит, триггер 2 остается в состоянии логического О, импульс на шине 9 не формируется. Если же входной импульс к моменту переполнения счетчика 4 не поступает, то сформированный при переполнении на выходе переноса счетчика 4 импульс поступает на R-вход триггера 7 и устанавливает его в состояние логического О. Поступление тактовых импульсов на счетный вход счетчика 4 прекращается. Входной импульс через элемент И б не проходит, триггер 2 остается в состоянии логического О, импульс на шине 9 не формируется. По срезу первого поступившего после этого входного импульса начинается новый цикл

формирования .требуемого интервала времени.

Формула изобретения

1.Устройство допускового контроля временных интервалов между импульсами,

содержащее элемент И, первый вход которого соединен с входной шиной и входом формирователя заднего фронта импульсов, а выход - с S-входом первого триггера, выход которого соединен с выходной шиной, а R-вход - с выходом формирователя заднего Фронта импульсов и входом сброса счетчика импульсов, счетный вход которого соединен с выходом генератора тактовых импульсов,

а выходы - поразрядно с входами формирователя строба контроля, выход которого соединен с вторым входом элемента И, о т л и- чающееся тем, что, с целью повышения достоверности контроля за счет исключения

возможности появления ложного импульса на выходной шине в случае поступления на входную шину импульсов, опережающих по времени строб контроля и перекрывающихся с ним, а также в случае, если интервал

между входными импульсами t находится в интервале (К ТСч + tH) t (К Тсч + Тн + + At), где Тсч - время максимального заполнения счетчика импульсов; t(l - нижняя граница допуска контроля; At - допуск

контроля; К 1, в него введен второй триггер, S-вход которого соединен с выходом формирователя заднего фронта импульсов, С-вход - с входной шиной, О-вход - с выходом формирователя строба контроля, Rвход - с выходом переполнения счетчика импульсов, а выход - с управляющим входом генератора тактовых импульсов, выполненного управляемым.

2.Устройство поп. 1,отличающее- с я тем, что формирователь строба контроля

выполнен в виде запоминающего блока, адресные входы которого поразрядно соединены с входами формирователя строба контроля, а выход - с выходом формирова- теля строба контроля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации импульсов | 1985 |

|

SU1322434A1 |

| УСТРОЙСТВО ДЛЯ ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1990 |

|

RU2024906C1 |

| Устройство для допускового контроля частоты | 1990 |

|

SU1781633A1 |

| Устройство для контроля двух импульсных последовательностей | 1988 |

|

SU1569834A1 |

| Селектор серий импульсов | 1988 |

|

SU1615875A1 |

| Устройство задержки прямоугольных импульсов | 1986 |

|

SU1385278A1 |

| Устройство для допускового контроля частоты | 1990 |

|

SU1748240A1 |

| Формирователь импульсов | 1989 |

|

SU1626353A2 |

| Частотный компаратор | 1988 |

|

SU1555843A2 |

| Устройство для допускового контроля длительности последовательности временных интервалов | 1988 |

|

SU1647508A1 |

Изобретение относится к импульсной технике и может быть использовано для контроля временных интервалов между импульсами. Устройство допускового контроля аременных интервалов между импульсами содержит формирователь 1 заднего фронта Входе импульсов, триггеры 2 и 7, генератор 3 тактовых импульсов, счетчик 4 импульсов, формирователь 5 строба контроля, элемент И 6, входную шину 8, выходную шину 9. Исключение возможности появления ложного им- пульса на выходной шине в случае поступления на входную шину импульсов, опережающих по времени строб контроля и перекрывающихся с ним, а также в случае, если интервал t между входными импульсами находится в интервале (К ТСч + tH) t (К Тсч + tH + At), где Тсч - время максимального заполнения счетчика импульсов; tH - нижняя граница допуска контроля; At - величина строба контроля; К 1. позволяет повысить достоверность контроля. 1 з.п. ф-лы. 2 ил. . w ё

| Селектор импульсов по интервалу между импульсами | 1980 |

|

SU907791A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство допускового контроля временных интервалов между импульсами | 1978 |

|

SU723768A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-07—Публикация

1988-12-16—Подача