(21) 4626661/07J 4626745/07 422) 27.12.88 (46) 07.07.91. Бкхл. Р 25

(71)Рыбинский авиационный технологический институт

(72)В.В.Юдин

(53)621.316.722.1(088.8)

(56)Авторское свидетельство СССР № 976432, кл. С 05 F 1/20, 1981.

Авторское свидетельство СССР № 1291942 кл. G 05 F 1/20, 1985.

(54)СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ

(57)Изобретение относится к электротехнике и может найти применение в системах электропитания радиоэлектронной аппаратуры. .Целью изобретения является повышение точности стабилизации выходного напряжения в условиях нестабильности частоты входного напряжения. Стабилизация выходного напряжения осуществляется регулирующим органом 1 дискретного , действия с помощью цифрового блок а управления. Измерение выходного напряжения происходит в блоке 10 выборки-хранения в момент равенства двух пилообразных напряжений, формируемых интеграторами 11 и 12. Постоянные времени интеграторов 11 и 12 выбраны такими, что в момент равенства иппряжений на их выходах выходное напряжение достигает амплитудного значения. Изменение частоты входного напряжения не приводит к смещению управляющего импульса на выходе узла 13 сравнения относительно положения максимума измеряемого напряжения, т.к. постоянные времени интеграторов 11 и 12 в процессе работы остаются неизменными. 1 з.п, ф-льт,

7 ил. I

&

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизатор переменного напряжения | 1988 |

|

SU1628050A1 |

| Стабилизатор переменного напряжения | 1984 |

|

SU1246068A1 |

| Стабилизатор переменного напряжения | 1982 |

|

SU1026123A1 |

| СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2012 |

|

RU2501154C1 |

| Стабилизатор переменного напряжения | 1985 |

|

SU1317411A1 |

| СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2011 |

|

RU2474864C1 |

| Способ и установка для определения вариативности передаточного отношения редуктора | 2016 |

|

RU2658138C1 |

| Стабилизатор переменного напряжения | 1984 |

|

SU1246064A1 |

| СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1994 |

|

RU2072550C1 |

| Стабилизатор переменного напряжения | 1986 |

|

SU1374197A1 |

Изобретение относится к электротехнике и может найти применение в системах электропитания радиоэлектронной аппаратуры. Целью изобретения является повышение точности стабилизации выходного напряжения в условиях нестабильности частоты входного напряжения. Стабилизация выходного напряжения осуществляется регулирующим органом 1 дискретного действия с помощью цифрового блока управления. Измерение выходного напряжения происходит в блоке 10 выборки-хранения в момент равенства двух пилообразных напряжений, формируемых интеграторами 11 и 12. Постоянные времени интеграторов 11 и 12 выбраны такими, что в момент равенства напряжений на их выходах выходное напряжение достигает амплитудного значения. Изменение частоты входного напряжения не приводит к смещению управляющего импульса на выходе узла 13 сравнения относительно положения максимума измеряемого напряжения, т. к. постоянные времени интеграторов 11 и 12 в процессе работы остаются неизменными. 1 з.п. ф-лы, 7 ил.

а о

i

со

СЛ

Изобретение относится к электроехнике и может найти применение в истемах электропитания радиоэлекронной аппаратуры.

Цель изобретения - повышение точности стабилизации выходного напряения в условиях нестабильности частоты входного напряжения.

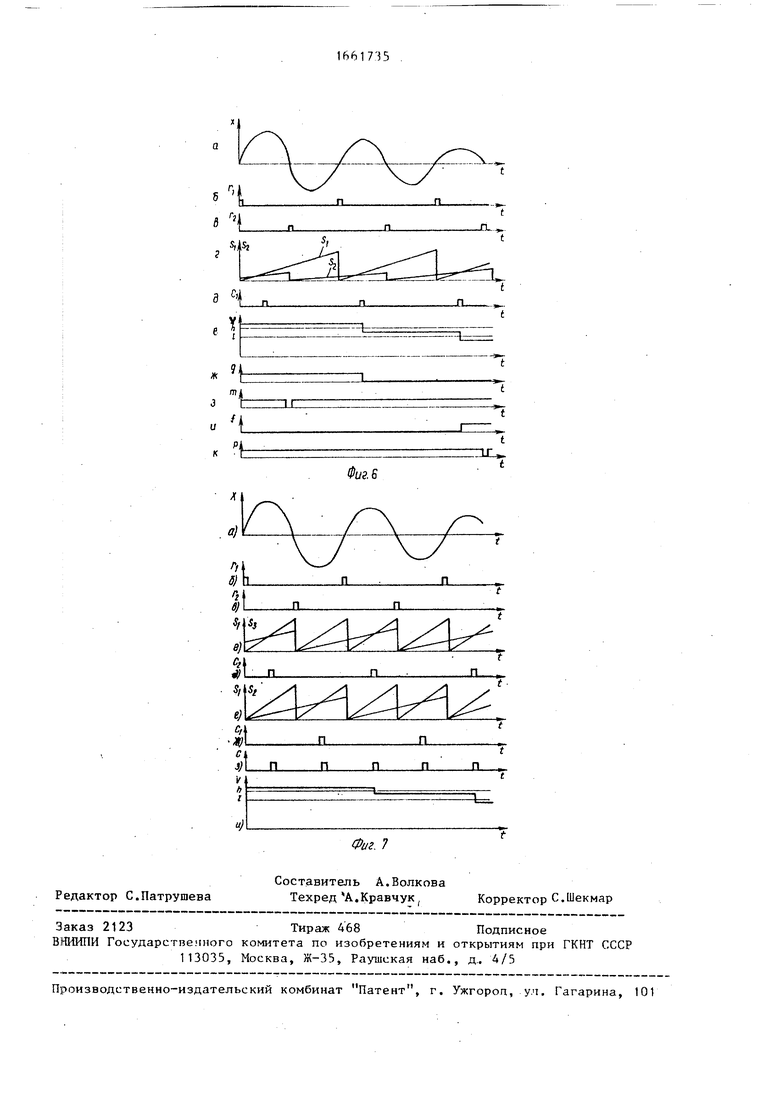

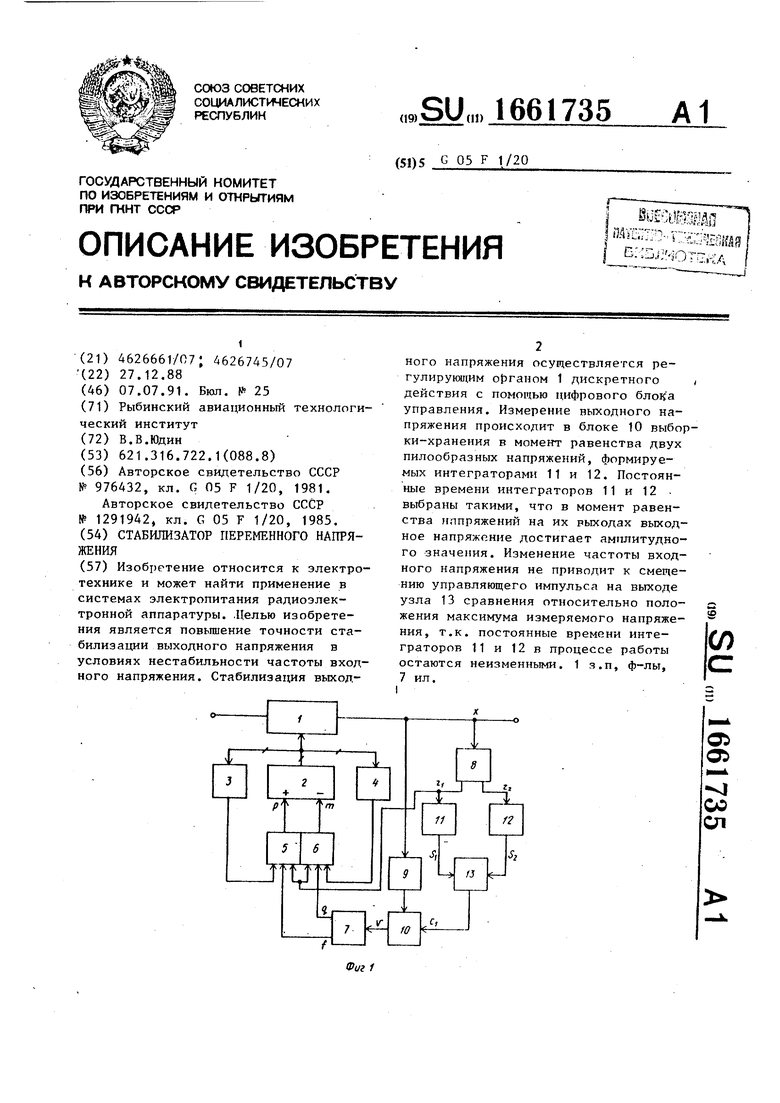

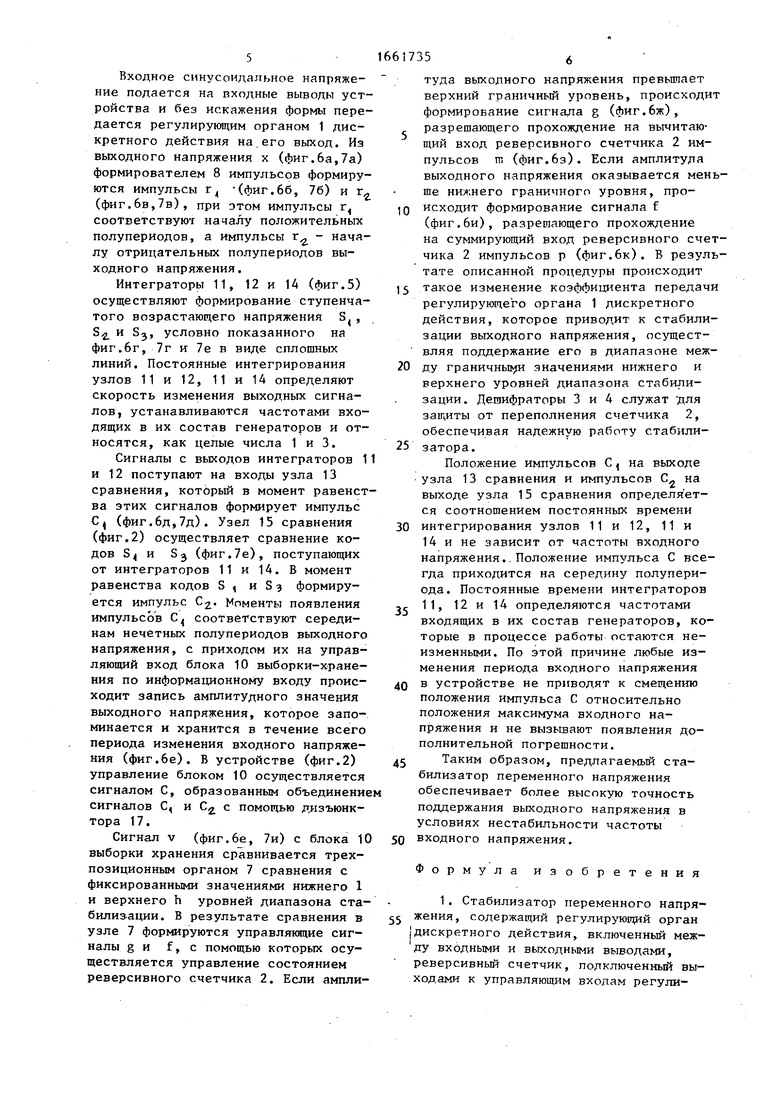

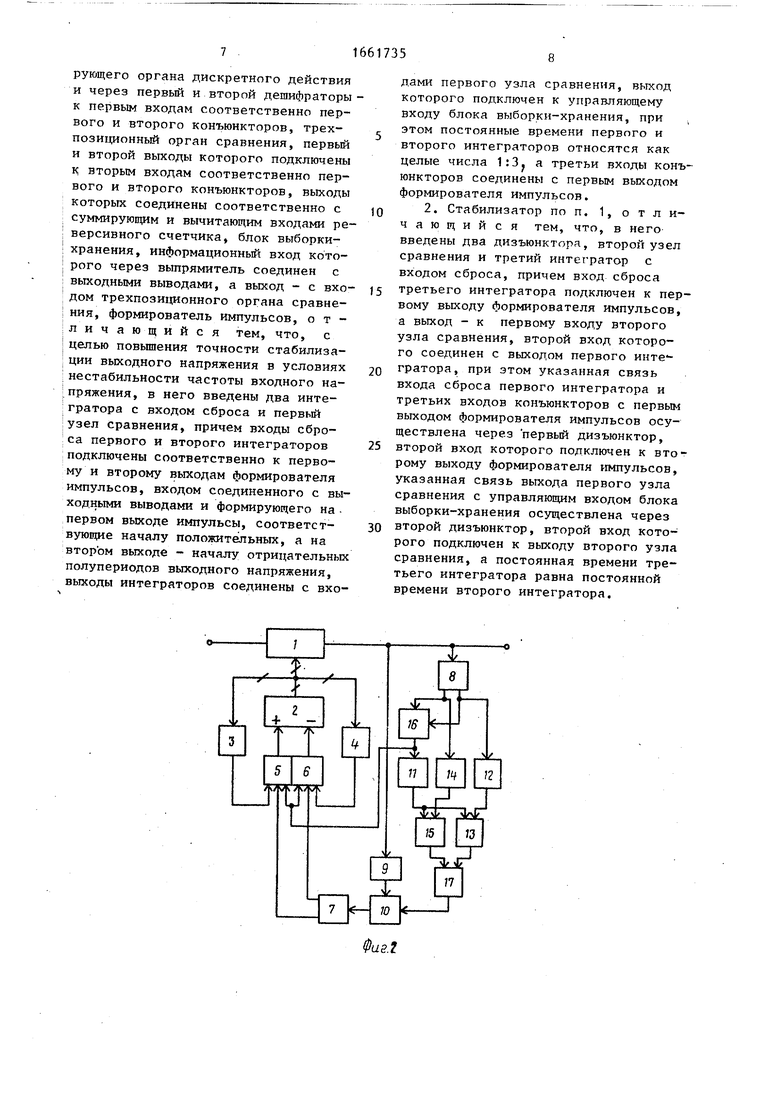

На фиг. 1 изображена электриче- jn екая схема стабилизатора переменного напряжения с двумя интегратораи; на фиг. 2 - электрическая схема стабилизатора переменного напряжения с тремя интеграторами; на фиг. 3 - схема трехпозиционного, органа сравнения; на фиг. 4 - схема формирователя импульсов; на фиг. 5 - схема интегратора; на фиг. 6 - временные диаграммы, поясняющие работу стабилиза- 20 тора,представленного на фиг. 1 , на фиг. 7 - временные диаграммы, поясняющие работу стабилизатора, представленного на фиг.2.

Стабилизатор переменного напряже- 25 ния (фиг.1) содержит регулирующий орган 1 дискретного действия, включенный между входными и выходными выводами, реверсивный счетчик 2, подключенный выходами к управляющим входам 0 регулирующего органа 1 дискретного действия и через дешифраторы 3 и 4 - к первым входам конъюнкторов 5 и 6, вторые входы которых соединены с вы- ходами трехпозиционного органа 7 сравнения, а выходы - соответственно с суммирующим и вычитающим входами реверсивного счетчика 2, формирователь 8 импульсов, входом подключенный к выходным выводам, к которым через дд выпрямитель 9 подключен также информационный вход блока 10 выборки-хранения, выход которого соединен с входом трехпозиционного органа 7 сравнения, первый 11 и второй 12 интегра- дз торы и узел 13 сравнения, выход которого соединен с управляющим входом блока 10 выборки-хранения, а входы подключены к выходам интеграторов 11 и 12, входы сброса которых подключе- 0 ны соответственно к первому и второму выходам формирователя S импульсов, формирующего на первом выходе импульсы, соответствующие началу положительных, а на втором выходе - началу отрицательных полупериодов выходного напряжения, при этом третьи входы конъюнкторов 5 и 6 соединены с одним из выходов формирователя 8 импульсов.

35

55

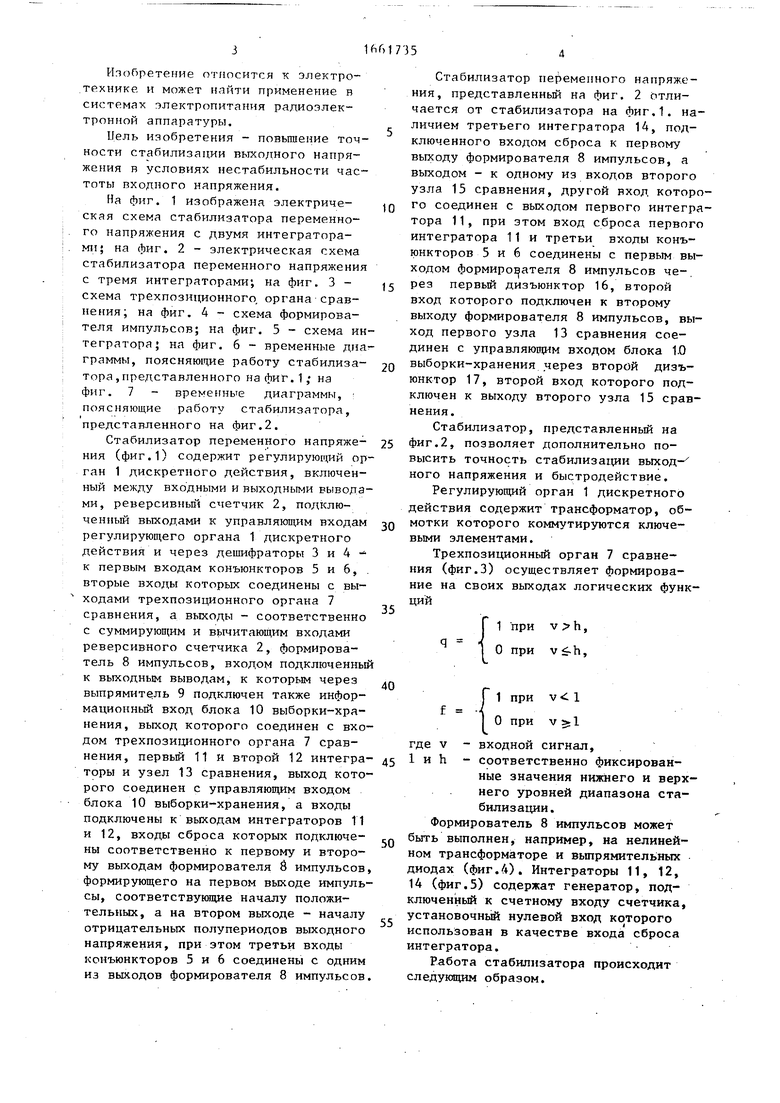

Стабилизатор переменного напряжения, представленный на фиг. 2 отличается от стабилизатора на фиг.1. наличием третьего интегратора 14, подключенного входом сброса к первому выходу формирователя 8 импульсов, а выходом - к одному из входов второго узла 15 сравнения, другой яход которого соединен с выходом первого интегратора 11, при этом вход сброса первого интегратора 11 и третьи входы конъюнкторов 5 и 6 соединены с первым выходом формирователя 8 импульсов через первый дизъюнктор 16, второй вход которого подключен к второму выходу формирователя 8 импульсов, выход первого узла 13 сравнения соединен с управляющим входом блока 1.0 выборки-хранения через второй дизъюнктор 17, второй вход которого подключен к выходу второго узла 15 сравнения.

Стабилизатор, представленный на фиг.2, позволяет дополнительно повысить точность стабилизации выход- ного напряжения и быстродействие.

Регулирующий орган 1 дискретного действия содержит трансформатор, обмотки которого коммутируются ключевыми элементами.

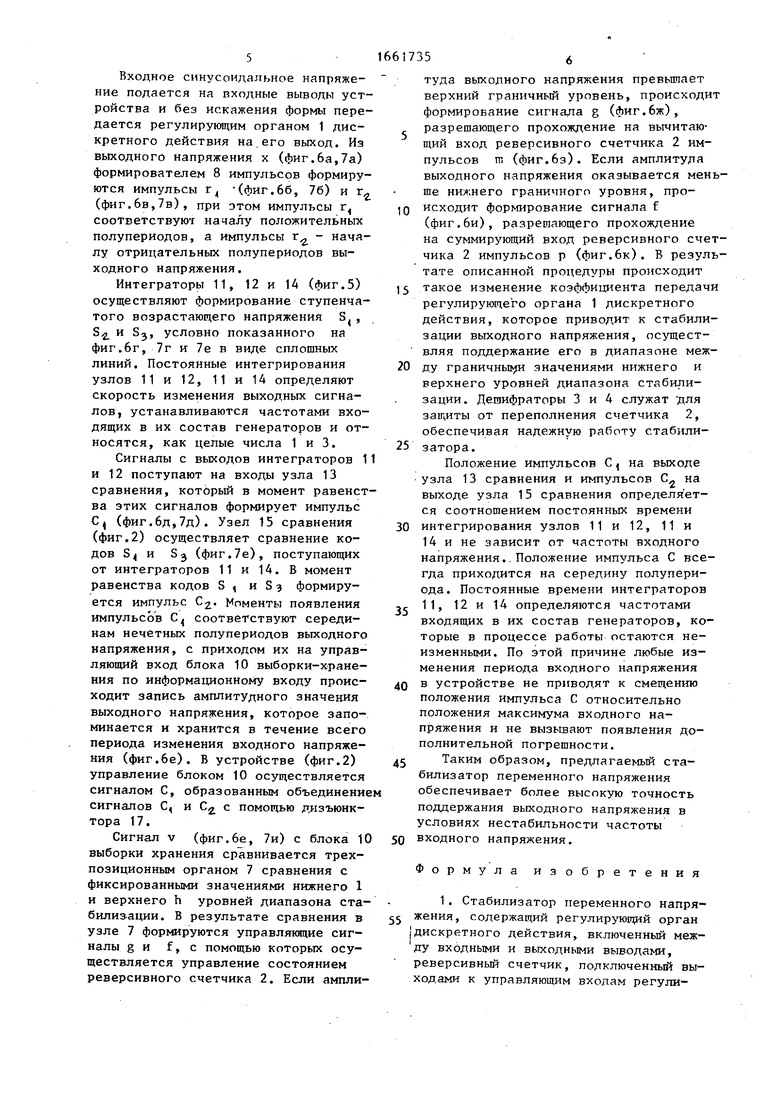

Трехпозиционный орган 7 сравнения (фиг.З) осуществляет формирование на своих выходах логических функций

q

1 при v h,

0при vЈ-h,

1при v 1 О при v 1

где v - входной сигнал, 1 и h - соответственно фиксированные значения нижнего и верхнего уровней диапазона стабилизации.

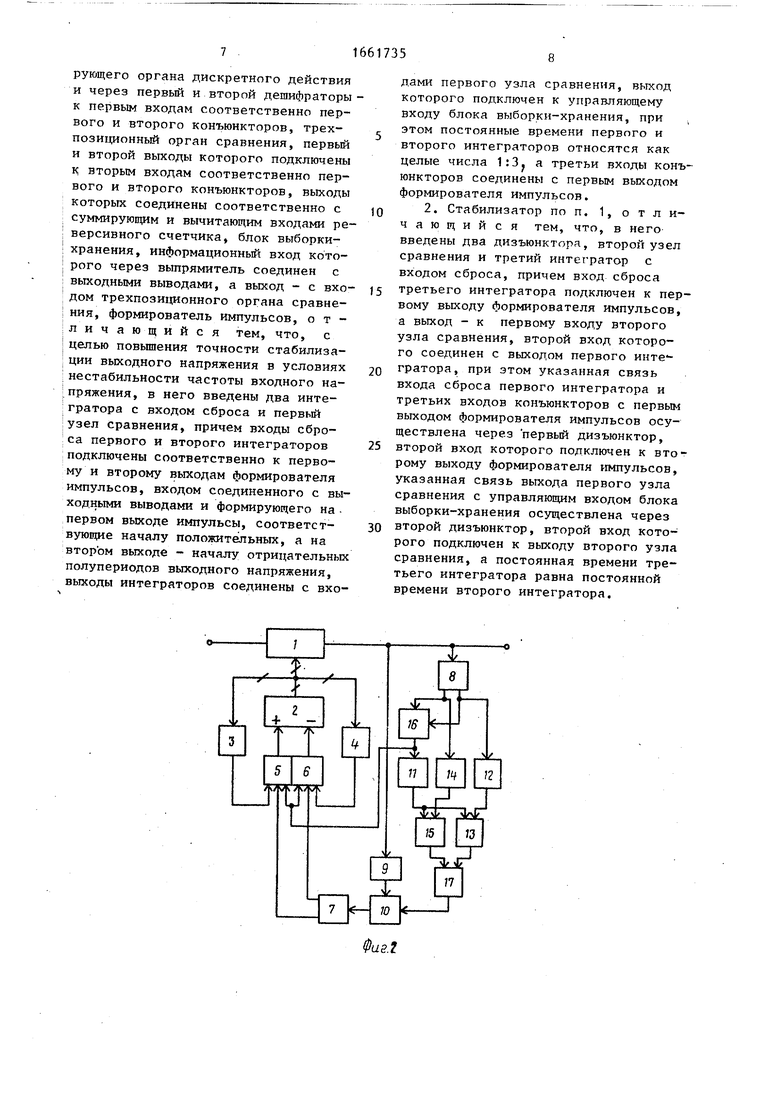

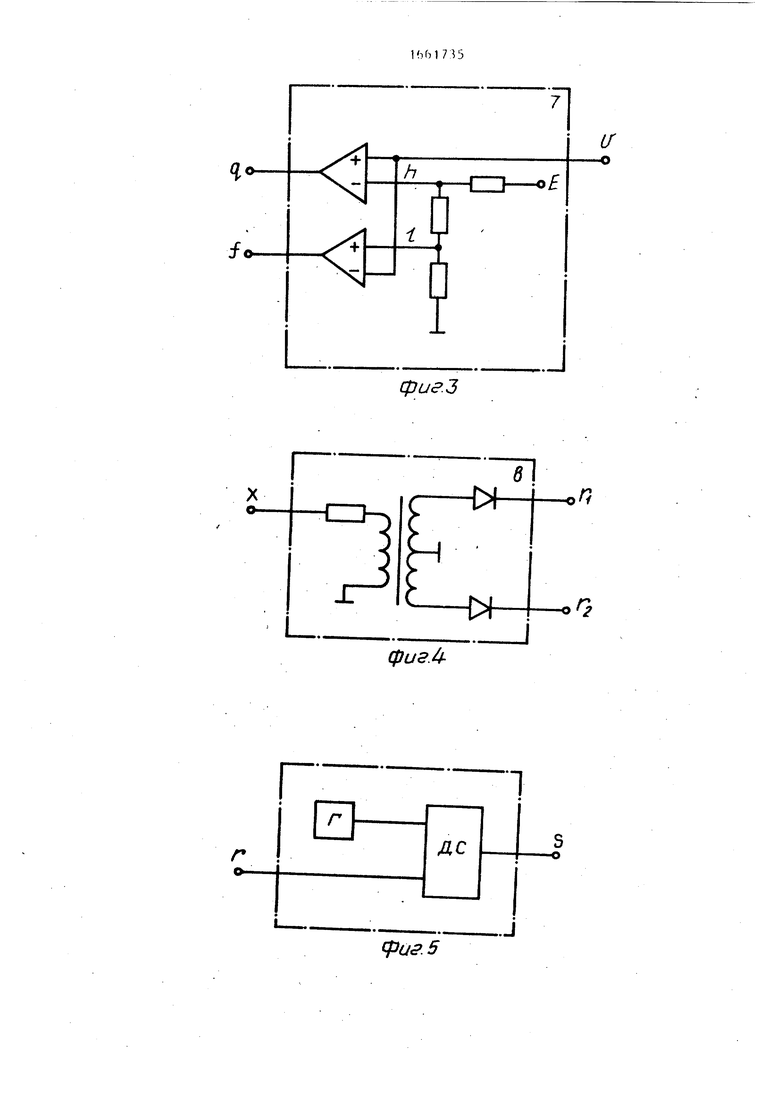

Формирователь 8 импульсов может быть выполнен, например, на нелинейном трансформаторе и выпрямительных диодах (фиг.4). Интеграторы 11, 12, 14 (фиг.З) содержат генератор, подключенный к счетному входу счетчика, установочный нулевой вход которого использован в качестве входа сброса интегратора.

Работа стабилизатора происходит следующим образом.

Входное синусоидальное напряжение подается на входные выводы устройства и без искажения формы передается регулирующим органом 1 дискретного действия на его выход. Из выходного напряжения х (фиг.6а,7а) формирователем 8 импульсов формируются импульсы гд (фиг.66, 76) и г (фиг.6в,7в), при этом импульсы г,, соответствуют началу положительных полупериодов, а импульсы г - началу отрицательных полупериодов выходного напряжения.

Интеграторы 11, 12 и 14 (фиг.5) осуществляют формирование ступенчатого возрастающего напряжения S,

Sx, и S

J

3

условно показанного на

фиг.бг, 7г и 7е в виде сплошных линий. Постоянные интегрирования узлов 11 и 12, 11 и 14 определяют скорость изменения выходных сигналов, устанавливаются частотами входящих в их состав генераторов и относятся, как целые числа 1 и 3.

Сигналы с выходов интеграторов 1 и 12 поступают на входы узла 13 сравнения, который в момент равенства этих сигналов формирует импульс GI (фиг.6д,7д). Узел 15 сравнения (фиг.2) осуществляет сравнение кодов S и 83 (фиг.7е), поступающих от интеграторов 11 и 14. Б момент равенства кодов S и S формируется импульс С2. Моменты появления импульсов С соответствуют серединам нечетных полупериодов выходного напряжения, с приходом их на управляющий вход блока 10 выборки-хранения по информационному входу происходит запись амплитудного значения выходного напряжения, которое запоминается и хранится в течение всего периода изменения входного напряжения (фиг.бе). В устройстве (фиг.2) управление блоком 10 осуществляется сигналом С, образованным объединение сигналов С, и С с помощью дизъюнк- тора 17.

Сигнал v (фиг.бе, 7и) с блока 10 выборки хранения сравнивается трех- позиционным органом 7 сравнения с фиксированными значениями нижнего 1 и верхнего h уровней диапазона стабилизации. В результате сравнения в узле 7 формируются управляющие сигналы g и f, с помощью которых осуществляется управление состоянием реверсивного счетчика 2. Если ампли0

5

0

5

0

5

0

5

0

туда выходного напряжения превышает верхний граничный уровень, происходит формирование сигнала g (фиг.бж), разрешающего прохождение на вычитающий вход реверсивного счетчика 2 импульсов те (фиг.бз). Если амплитуда выходного напряжения оказывается меньше нижнего граничного уровня, происходит формирование сигнала f (фиг.би), разрешающего прохождение на суммирующий вход реверсивного счетчика 2 импульсов р (фиг.бк). В результате описанной процедуры происходит такое изменение коэффициента передачи регулирующего органа 1 дискретного действия, которое приводит к стабилизации выходного напряжения, осуществляя поддержание его в диапазоне между граничными значениями нижнего и верхнего уровней диапазона стабилизации. Дешифраторы 3 и 4 служат для защиты от переполнения счетчика 2, обеспечивая надежную работу стабилизатора.

Положение импульсов С, на выходе

узла 13 сравнения и импульсов С на выходе узла 15 сравнения определяется соотношением постоянных времени интегрирования узлов 11 и 12, 11 и 14 и не зависит от частоты входного напряжения. Положение импульса С всегда приходится на середину полупериода. Постоянные времени интеграторов 11, 12 и 14 определяются частотами входящих в их состав генераторов, которые в процессе работы остаются неизменными. По этой причине любые изменения периода входного напряжения в устройстве не приводят к смещению положения импульса С относительно положения максимума входного напряжения и не вызывают появления дополнительной погрешности.

Таким образом, предлагаемый стабилизатор переменного напряжения обеспечивает более высокую точность поддержания выходного напряжения в условиях нестабильности частоты входного напряжения.

Ф

ормула изобретения

Г

X

оГ

л

оh

41oЈ

J

фигЗ

фиг 4S

Ч)

фиг. 5

..J

«ft

«ffc

Фиг

Авторы

Даты

1991-07-07—Публикация

1988-12-27—Подача