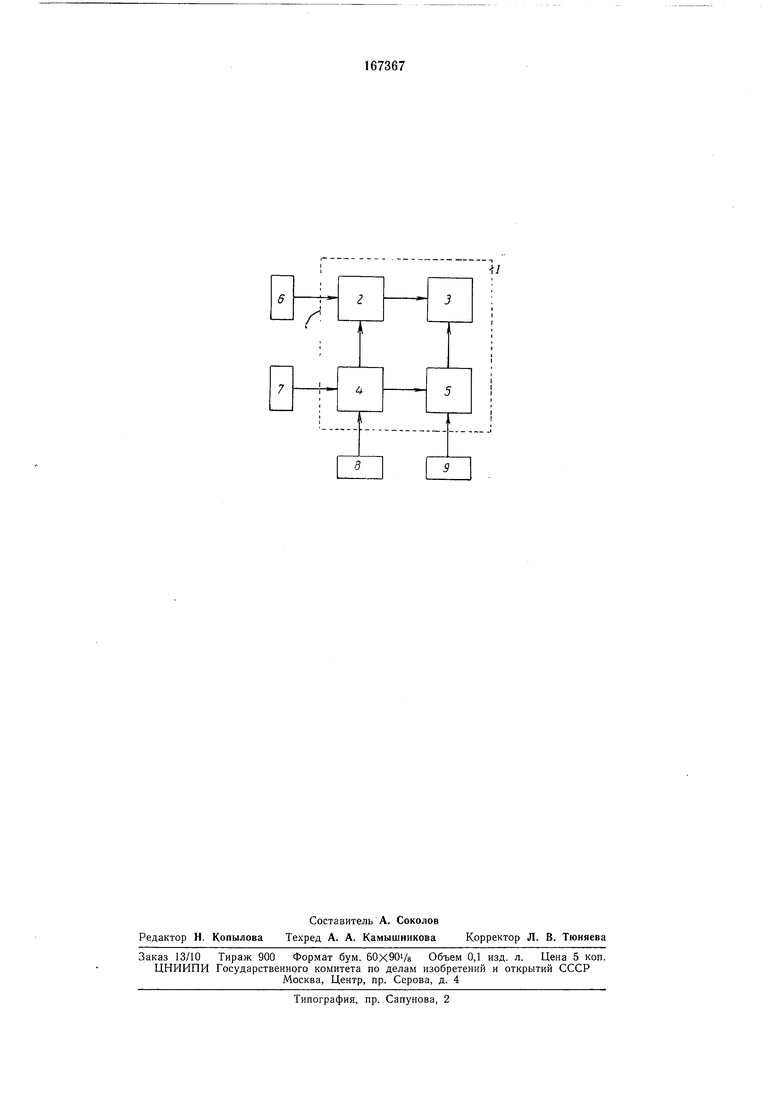

Известен снособ прошивки избирающей матрицы запоминающего устройства с линейным выбором, построенной на ферритовых сердечниках с прямоугольной петлей гистерезиса, позволяющий в избранных колонке и строке суммировать токи большого числа источников. Недостатком такого способа прошивки являются большая длина прошивающих проводов и большое количество проводов, пронизывающих каждый сердечник. Предлагаемый способ прошивки избирающей матрицы запоминающего устройства отличается от известного тем, что избирающую матрицу разделяют на ряд блоков меньшей емкости, прошивку блоков осуществляют в соответствии с кодом, количество разрядов которого зависит только от емкости блока, и соответствующие координатные обмотки соседних (по координатам х и у) блоков соединяют последовательно. Если, например, избирающая матрица разделена на т2 блоков, то предлагаемый способ прошивки позволяет в т раз уменьшить длину координатной шины и во столько же раз сократить количество проводов, проходящих через каждый сердечник, т. е. уменьшить в т раз активное сопротивление шины. Избирающую матрицу / емкостью N разделяют, например, на четыре блока 2, 3, 4, 5 емкостью - - каждый. Координатные 4 обмотки X соединяют последовательно у блоков 4, 2 и 5, 3, обмотку у соединяют последовательно у блоков 2, 3 н 4, 5. К. координатным обмоткам X присоединяют системы источников импульсов тока 6 ц 7, к обмоткам у - системы источников - 8 и 9. При каждом обращении к запоминающему устройству работает одна из систем источников ио каждой координате. Предмет изобретения Способ прошивки избирающей матрицы запоминающего устройства с линейным выбором, построенной на ферритовых сердечниках с прямоугольной петлей гистерезиса с объединением энергии большого числа источников, отличающийся тем, что, с целью уменьшения длины прошивающих проводов и сокращения числа проводов, пронизывающих каждый сердечник, избирающую матрицу разделяют на ряд блоков меньшей емкости, прошивку блоков осуществляют в соответствии с кодом, количество разрядов которого зависит от емкости блока, и соответствующие координатные обмотки соседних (по координатам х ti у} блоков соединяют последовательно.

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Матрица оперативного запоминающего устройства типа зд | 1972 |

|

SU448482A1 |

| ПРЕОБРАЗОВАТЕЛЬ К ДЕФЕКТОСКОПУ ДЛЯ ТЕПЛОВОГО КОНТРОЛЯ | 1990 |

|

RU2088897C1 |

| Способ изготовления запоминающих матриц для блоков памяти | 1975 |

|

SU669407A1 |

| Запоминающее устройство | 1957 |

|

SU118655A1 |

| АНАЛИЗАТОР КОДОВ | 1967 |

|

SU197694A1 |

| Контактное устройство для автоматизированного контроля печатных плат | 1990 |

|

SU1751866A1 |

| Способ обращения к запоминающему устройству на ферритовых сердечниках типа 2,5 Д | 1984 |

|

SU1144151A1 |

| Запоминающая матрица | 1977 |

|

SU641496A1 |

| Устройство для прошивки матриц | 1972 |

|

SU441869A1 |

| Устройство для изготовления разрядныхОбМОТОК B блОКАХ пАМяТи МАТРичНОгОТипА | 1972 |

|

SU798992A1 |

Даты

1965-01-01—Публикация