ь

ш. &

Ј

coL о

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизатор переменного напряжения | 1988 |

|

SU1583928A1 |

| РЕГУЛЯТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2003 |

|

RU2246745C2 |

| СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1994 |

|

RU2072550C1 |

| РЕГУЛЯТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2009 |

|

RU2399084C1 |

| РЕГУЛЯТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2012 |

|

RU2494436C1 |

| РЕГУЛЯТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2007 |

|

RU2339071C1 |

| Регулируемый преобразователь переменного напряжения | 1986 |

|

SU1396127A1 |

| РЕГУЛЯТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2011 |

|

RU2468410C1 |

| Преобразователь частоты | 1983 |

|

SU1201988A1 |

| РЕГУЛЯТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2009 |

|

RU2393524C1 |

Изобретение относится к электротехнике и может найти применение в устройствах электропитания аппаратуры. Целью изобретения является повышение точности стабилизации действующего знамения несинусоидального выходного напряжения. Цель достигается за счет введения в стабилизатор делителя 10 частоты, перестраиваемого делителя 11 частоты и дополнительного счетчика 1:2, Точность стабилизации действующего значения выходного напряжения определяется точностью операции возведения в квадрат выходного напряжения. Эта операция разбита на два линейных процесса: линейного нараста- ния во времени значения кода на выходе счетчика 12 и линейной зависимости частоты импульсов на выходе перестраиваемого делителя 11 частоты от значения этого кода. 1 з.п. ф-лы, k ил. 3 (Л с

Фиг.

. 3 . Изобретение относится к электротехнике и может найти применение в устройствах электропитания аппаратуры.

Целью изобретения является повыше- ие точности стабилизации действующего значения несинусоидального выходного напряжения. .

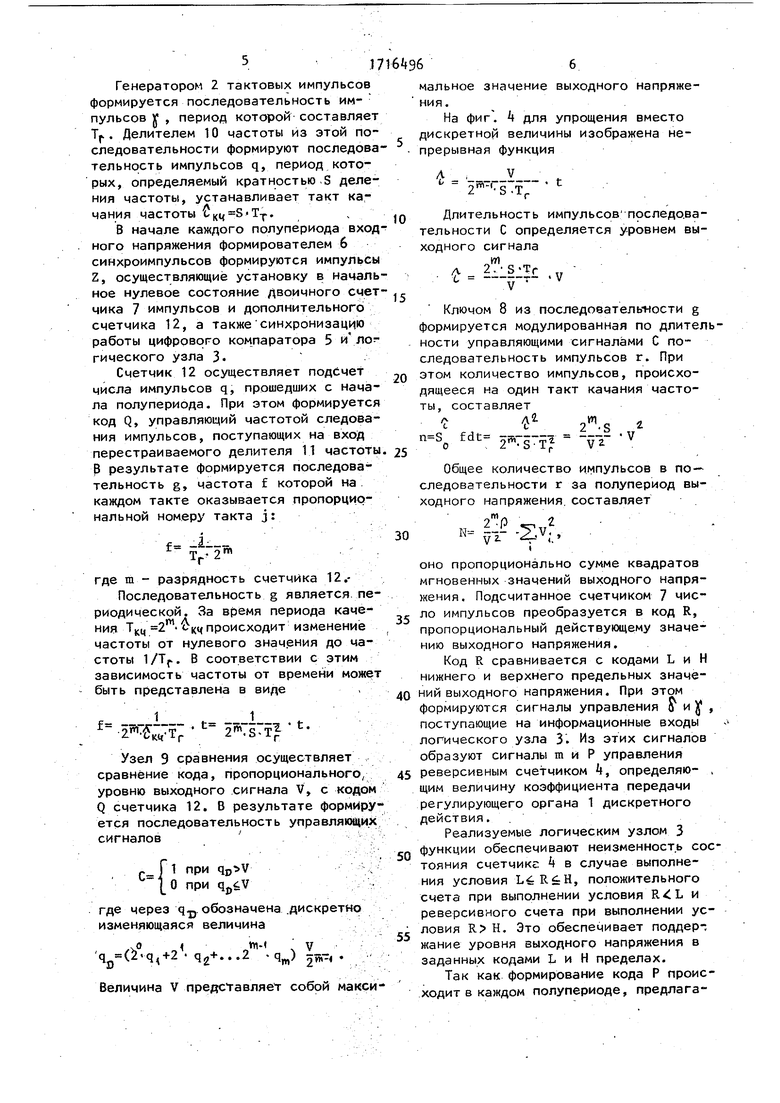

На фиг. 1 приведена блок-схема

стабилизатора переменного напряжения; JQ лельной группы подсоединены к ним

15

30

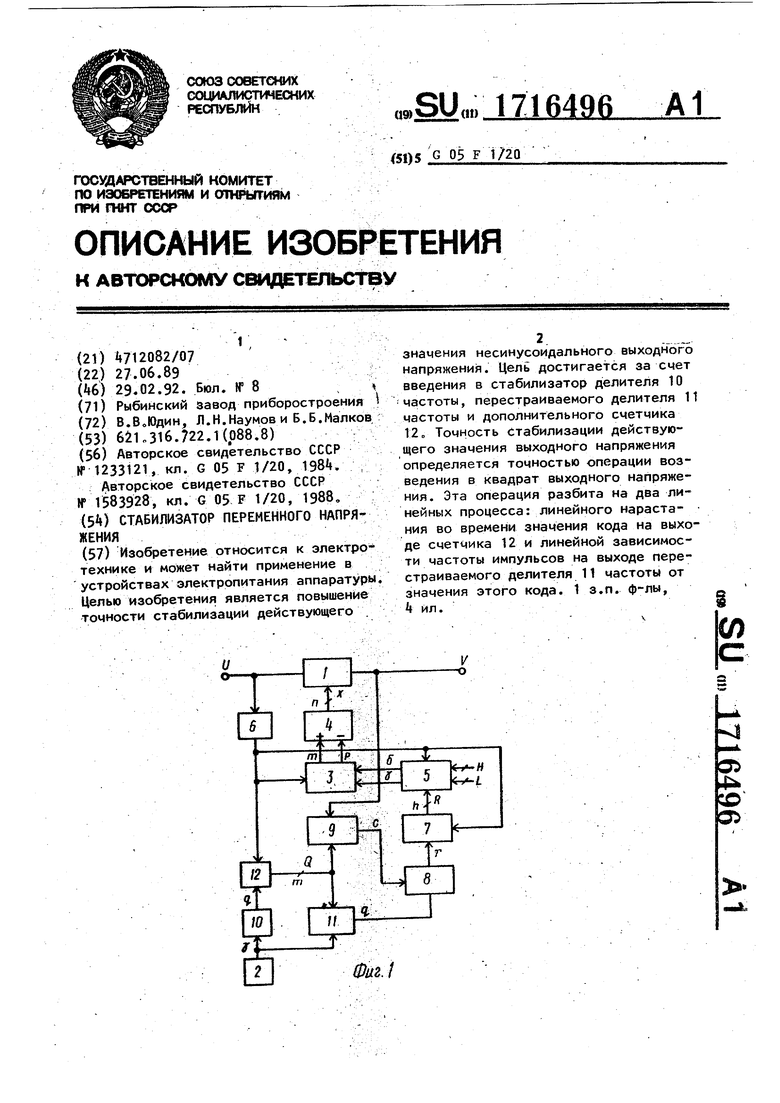

на фиг. 2 - схема регулирующего органа дискретного действия; на фиг.З - схема измерения; на фиг. А - временные диаграммы, поясняющие принцип работы стабилизатора.

Стабилизатор переменного напряжения (фиг. 1) содержит регулирующий орган 1 дискретного действия, включенный между входными и выходными выводами, генератор 2 тактовых импуль- о сов, логический узел 3, выходы которого через реверсивный счетчик 4 подключены к управляющим входам регулирующего органа 1 дискретного действия , первый и второй информационные 25 зходы логического узла 3 соединены соответственно с первым и вторым выходами -, цифрового компаратора 5, а синхронизирующий вход через формирователь 6 импульсов - к входным выводам, выход формирователя 6 импульсов подключен также к синхронизирующему входу цифрового компаратора 5 и установочному нулевому входу двоичного счетчика 7 импульсов, выходы которого подключены к информационным входам цифрового компаратора 5, а вход - к выходу ключа 8, соединенно- го управляющим входом через узел 9 сравнения с выходными выводами, делитель 10 частоты, перестраиваемый делитель частоты 11 и дополнительный двоичный счетчик 12, нулевой, установочный вход которого подключен к выходу формирователя 6 синхроимпульсов, . счетный вход - к выходу делителя 10 частоты, а выходы - к цифровым входам узла 9 сравнения к управляющим входам перестраиваемого делителя 11 частоты, счетный вход которого соединен с выходом генератора 2 тактовых импульсов, который подключен также к входу делителя 10 частоты.

Регулирующий орган дискретного действия (фиг. 2) выполнен на трансформаторе с секционированной вторичной обмоткой, для чисел витков которой С0( ,СЭа.. .u)n справедливы соотношения

2(0k (К-1,2,...,п-1)

посредством логических инверторов.

Логический узел 3 реализует сис му функций ,

Р гГ&,

,

где Z - сигнал на выходе формирова ля 6 синхроимпульсов; сигналы соответственно на первом и втором выходах ци вого компаратора 5. Реализуемая цифровым компаратор 5 функция описывается системой ура нений

&иу Ч

ft

при L R при L Ј R

при при

RЈH

35

где L и Н - коды соответственно ни него и верхнего уровне диапазона стабилизации -R - код на информационных

входах цифрового компа тора 5.

Период обнуления дополнительног двоичного счетчика 12 в п раз мень полупериода входного напряжения, г 40 п - целое числом

Частота сигнала на выходе перес иваемого делителя 1.1 частоты прямо пропорциональна значению кода на е управляющих входах.

Стабилизатор работает следующим образом.

Входное напряжение U поступает регулирующий орган 1 дискретного д ствия, коэффициент передачи К кото 50 го определяется скалярным произвед нием вектора управления ,ХЛ,. Х.Д и вектора коэффициента передач J- «2 «и1

.m

ICDo С30

u&J

т.е. .

СО

В результате формируется выходн напряжение

U

ко

Секции вторичной обмотки объединены в общую схему посредством групп последовательных и групп параллельных ключей. Управляющие входы последовательной группы ключей непосредственно подсоединены к управляющим входам регулирующего органа 1 дискретного действия. Управляющие входы парал

посредством логических инверторов.

Логический узел 3 реализует систему функций ,

Р гГ&,

,:

где Z - сигнал на выходе формирователя 6 синхроимпульсов; сигналы соответственно на первом и втором выходах цифрового компаратора 5. Реализуемая цифровым компаратором 5 функция описывается системой уравнений

&иу

Ч

ft

при L R при L Ј R

при при

RЈH

5

5

где L и Н - коды соответственно нижнего и верхнего уровней диапазона стабилизации; -R - код на информационных

входах цифрового компара-1 тора 5.

Период обнуления дополнительного двоичного счетчика 12 в п раз меньше ; полупериода входного напряжения, где 0 п - целое числом

Частота сигнала на выходе перестраиваемого делителя 1.1 частоты прямо пропорциональна значению кода на его управляющих входах.

Стабилизатор работает следующим образом.

Входное напряжение U поступает на регулирующий орган 1 дискретного действия, коэффициент передачи К которо- 0 го определяется скалярным произведением вектора управления ,ХЛ,..., Х.Д и вектора коэффициента передачи J- «2 «и1

.m

ICDo С30

u&J

т.е. .

В результате формируется выходное напряжение

U

Генератором 2 тактовых импульсов формируется последовательность импульсов у , период которой составляет Ту . Делителем 10 частоты из этой последовательности формируют последовательность импульсов q, период которых, определяемый кратностью,S деления частоты, устанавливает такт качания частоты .

В начале каждого полупериода вход- ного напряжения формирователем 6 синхроимпульсов формируются импульсы Z, осуществляющие установку в начальное нулевое состояние двоичного счетчика 7 импульсов и дополнительного счетчика 12, а также синхронизацию работы цифрового компаратора 5 й .ло гического узла 3Счетчик 12 осуществляет подсчет числа импульсов q, прошедших с начала полупериода. При этом формируется код Q, управляющий частотой следования импульсов, поступающих на вход перестраиваемого делителя 1.1 частоты. В результате формируется последовательность g, частота f которой на каждом такте оказывается пропорциональной номеру такта j:

f- , Тг- 2т

где m - разрядность счетчика 12,Последовательноеть g является периодической. За время периода качения Ткц 2™- Јкч происходит изменение частоты от нулевого значения до частоты 1/Тр. В соответствии с этим зависимость частоты от времени может быть представлена в виде ,

1

TiTv t- З Тт Узел 9 сравнения осуществляет сравнение кода, пропорционального, уровню выходного сигнала V, с кодом Q счетчика 12. В результате формируется последовательность управляющих сигналов .

41

при О при

где через q. обозначена изменяющаяся величина

2%,,+...2

ПИ

, V Чт

-О - -1 - V

Величина V представляет собой макси

мальное значение выходного напряжения.

На фиг. А для упрощения вместо дискретной величины изображена непрерывная функция

А , V - t

Длительность импульсов последовательности С определяется уровнем выходного сигнала

Ј

S-Тг ----

Ключом 8 из последовательности g формируется модулированная по длительности управляющими сигналами С последовательность импульсов г. При этом количество импульсов, происхо- дящееся на один такт качания частоты, составляет

С

41

fdt-

§./ V V

Общее количество импульсов в последовательности г за полупериод выходного напряжения, составляет

2

. V

V2N- Ј -Tvr

14 -

5

оно пропорционально сумме квадратов мгновенных значений выходного напряжения. Подсчитанное счетчиком 7 число импульсов преобразуется в код R, пропорциональный действующему значению выходного напряжения.

Код R сравнивается с кодами L и Н нижнего и верхнего предельных значе0 ний выходного напряжения. При этом формируются сигналы управления Ј и , поступающие на информационные входы логического узла 3. Из этих сигналов образуют сигналы m и Р управления

5 реверсивным счетчиком k, определяю- , щим величину коэффициента передачи регулирующего органа 1 дискретного действия.

Реализуемые логическим узлом 3 функции обеспечивают неизменность состояния счетчике 4 в случае выполнения условия Lu RЈ:H, положительного счета при выполнении условия и реверсивного счета при выполнении условия R Н, Это обеспечивает поддер-; жание уровня выходного напряжения в заданных кодами L и Н пределах.

Так как формирование кода Р происходит в каждом полупериоде, предлага0

5

717

емая схема стабилизатора обладает большим быстродействием. Она отслеживает изменения действующей величины выходного напряжения, происходящие в течение любого полупериода.

По сравнению с известным стабилизатором переменного напряжения предлагаемое техническое решение обеспечивает большую точность стабилизации действующих значений напряжений. При одинаковом количестве уровней коэффициентов передачи регулирующего органа 1 дискретного действия стабил

ность действующего значения выходного (5 пульсов и к синхронизирующему входу

напряжения определяется точностью определения его фактической величины. В предлагаемом устройстве квадратичное суммирование обеспечивается за счет одновременного выполнения двух встречных процессов- формирования линейной временной зависимости i и линейного преобразования временной шкалы. При этом используется цифровая реализация каждого из процессов, линейная зависимость формируется путем суммирования равномерно следу20

25

цифрового компаратора, и генератор тактовых импульсов, при этом цифрово компаратор соответственно на первом и втором выходах реализует функции

Z при L R при L Ј R

Ч

и

при при

RЈH

на

а логический узел соответственно первом и втором выходах функции

ное преобразование временной шкалы - путем изменения частоты следования тактовых импульсов.

Замена аналогового формирования параболического сигнала двумя одновременно выполненными цифровыми линеными преобразованиями обеспечивает повышение стабильности действующего значения несинусоидального выходного напряжения.

формула изобретения

8

ключа, первый и второй управляющие входы - к выводам для подключения источников задания соответственно верхнего и нижнего уровней диапазона стабилизации, а первый и второй выходы цифрового компаратора соединены соответственно с первым и вторым информа - ционным входами логического узла, формирователь .синхроимпульсов, вход которого подключен к входным выводам, а выход - к синхронизирующему входу логического узла, к установочному нулевому входу двоичного счетчика им0

5

0

5

цифрового компаратора, и генератор тактовых импульсов, при этом цифровой компаратор соответственно на первом и втором выходах реализует функции

Z при L R при L Ј R

Ч

и

при при

RЈH

на

а логический узел соответственно первом и втором выходах функции

P-Z45-,

,

где R - код на информационных входах t цифрового компаратора;

выходной сигнал формирователя

синхроимпульсов;

коды соответственно верхнего

и нижнего уровней диапазона

стабилизации, поступающие от

соответствующих источников

задания,

Z Н и L 0

5

0

о т л и

чающийся тем, что, с

целью повышения точности стабилизации действующего значения несинусоидального выходного напряжения, в него введены делитель частоты, перестраиваемый делитель частоты и дополни- тельный двоичный счетчик, период обнуления которого в п раз меньше полупериода входного напряжения, где п - целое число, причем нулевой установочный вход дополнительного двоичного счетчика подключен к выходу формирователя синхроимпульсов, счетный вход - к выходу делителя частоты, а выходы - к цифровым входам узла сравнения и к управляющим входам перестраиваемого делителя частоты, счетный вход которого соединен с выходом генератора тактовых импульсов, подключенного также к входу делителя частоты, а

выход перестраиваемого делителя ча- стоты соединен с входом ключа, при этом частота -сигнала На выходе перестраиваемого делителя частоты прямо пропорциональна значению кода на его управляющих входах.

выпрямительный мост соединен с вто- ричной обмоткой трансформатора, первичная обмотка которого использована в качестве аналогового входа узла сравнения, и узле сравнения кодов, первые входы которого подключены.к выходам аналого-цифрового преобразователя, вторые входы использованы в качестве цифровых входов узла сравнения , а выход - в качестве выхода узла сравнения.

иъ. 3

С |

7

J-I

J

II

I l i l I I t I l I II II

Фиг. 4

Т

| Стабилизатор переменного напряжения | 1984 |

|

SU1233121A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| ; | |||

Авторы

Даты

1992-02-28—Публикация

1989-06-27—Подача