Изобретение относится к вычислительной технике может быть использовано при разработке и моделировании систем массового обслуживания и касается усовершенствования устройства по авт. св. № 1387009.

Устройство для моделирования систем массового обслуживания по основному авт. св. № 1387009 содержит первый элемент И, первый вход которого и информационный вход первого элемента запрета объединены и являются входом заявок низкого приоритета устройства, выход первого элемента запрета соединен с первым входом первого элемента ИЛИ, выход которого подключен к входу запуска первого блока задержки, выход которого соединен с первым входом второго элемента ИЛИ, а вход сброса первого блока задержки подключен к выходу второго элемента И, первый вход третьего элемента И и информационный вход второго элемента запрета объединены и являются входом заявок высокого приоритета устройства, выход третьего элемента ИЛИ подключен к входу запуска второго блока задержки, выход которого соединен с информационным входом третьего элемента запрета и первым входом четвертого элемента И, выход которого подключен к вычитающему входу реверсивного счетчика очереди заявок высокого приоритета, выход переполнения которого подключен к первому входу пятого элемента И, выход которого является выходом потерянных заявок высокого приоритета устройства, выход первого блока задержки соединен с первым выходом четвертого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента запрета, а выход четвертого элемента ИЛИ подключен к первому входу шестого элемента И, выход которого соединен с вычитающим входом реверсивного счетчика очереди заявок низкого приоритета и вторым входом первого элемента ИЛИ, выход переполнения реверсивного счетчика очереди заявок низкого приоритета соединен с управляющим входом четвертого элемента

(/)

VJ

Јь

4 СП

кэ

запрета и первым входом седьмого элемента И, выход которого является выходом потерянных заявок низкого приоритета, первый вход восьмого элемента И соединен с входом заявок низкого приоритета устрой- ства, а выход восьмого элемента I/I подключен к первому входу пятого элемента ИЛИ, второй вход которого подключен к выходу первого элемента И, а выход пятого элемента ИЛИ соединен с первым входом шестого элемента ИЛИ, выход которого подключен к второму входу седьмого элемента И и-ин- формационному входу четвертого элемента запрета, выход которого соединен с входом первого триггера и суммирующим входом реверсивного счетчика очереди заявок низкого приоритета, выход обнуления которого подключен к нулевому входу первого триггера, прямой выход которого соединен с вторым входом шестого элемента И и пер- вым управляющим входом первого элемента запрета, второй управляющий вход которого подключен к прямому выходу второго триггера, второму входу первого элемента И и первому входу второго элемента И, второй вход которого соединен с входом заявок высокого приоритета устройства, а выход подключен к второму входу шестого элемента ИЛИ и второму входу второго элемента ИЛИ, выход которого подключен к единичному входу второго триггера, нулевой вход которого соединен с выходом первого элемента ИЛИ, выход третьего элемента И соединен с вторым входом пятого элемента И и информационным входом пятого элемента запрета, выход которого подключен к единичному входу третьего триггера и суммирующему входу реверсивного счетчика очереди заявок высокого приоритета, выход переполнения которого соединен с управляющим входом пятого элемента запрета, а выход обнуления - с нулевым входом третьего триггера, прямой выход которого подключен к второму входу четвертого элемента И, управляющему вхо- ду третьего элемента запрета и первому уп- равляющему входу второго элемента запрета, выход которого подключен к первому входу третьего элемента ИЛИ, второй вход которого соединен с выходом четвер- того элемента И, а выход третьего элемента ИЛИ подключен к единичному входу четвертого триггера, нулевой вход которого соединен с выходом второго блока задержки, прямой выход четвертого триггера соеди- нен с вторым управляющим входом второго элемента запрета, вторым входом третьего элемента И, третьим управляющим входом первого элемента запрета и вторым входом восьмого элемента И.

Недостатком известного устройства является то, что оно не учитывает различной длительности обслуживания приборов, обрабатывающих заявки абсолютного приоритета.

Цель изобретения - расширение функциональных возможностей устройства за счет учета различной длительности обслуживания двух приборов, обрабатывающих заявки высокого приоритета.

Эта цель достигается тем, что в устройство по авт. св. № 1387009 введены третий блок задержки, второй реверсивный счетчик очереди заявок высокого приоритета, таймер, пятый и шестой счетчики, шестой элемент запрета, седьмой и восьмой элементы ИЛИ, девятый и десятый элементы И, инверсный выход третьего триггера подключен к первому входу девятого элемента И, выход третьего элемента ИЛИ соединен с первым входом седьмого элемента ИЛИ, выход третьего элемента И подключен к первому входу десятого элемента И и информационному входу шестого элемента за- прета, выход которого подключен к суммирующему входу второго реверсивного счетчика очереди заявок высокого приоритета, выход которого соединен с вторым входом девятого элемента И, выход которого подключен к второму входу седьмого элемента ИЛИ, выход которого через третий блок задержки соединен с суммирующим входом пятого счетчика и первым входом восьмого элемента ИЛИ, второй вход которого соединен с выходом таймера, а выход подключен к вычитающему входу второго реверсивного счетчика очереди заявок высокого приоритета, выход которого соединен с управляющим входом шестого элемента запрета и вторым входом десятого элемента И, выход которого подключен к суммирующему входу шестого счетчика.

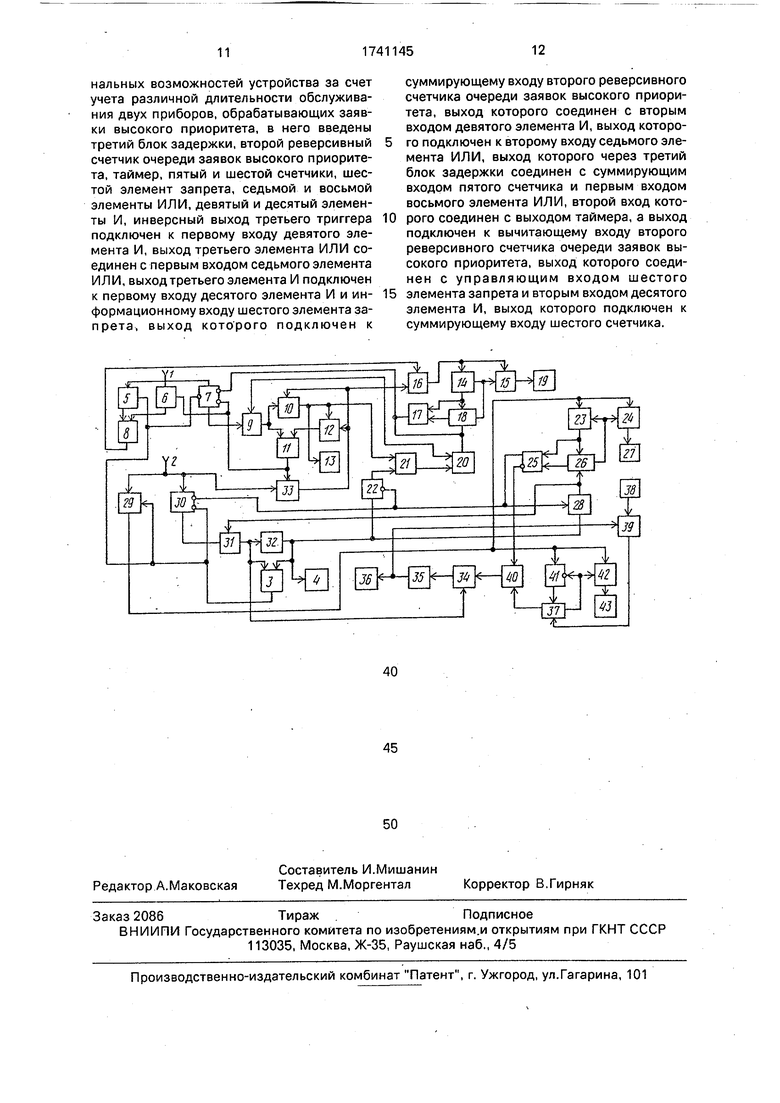

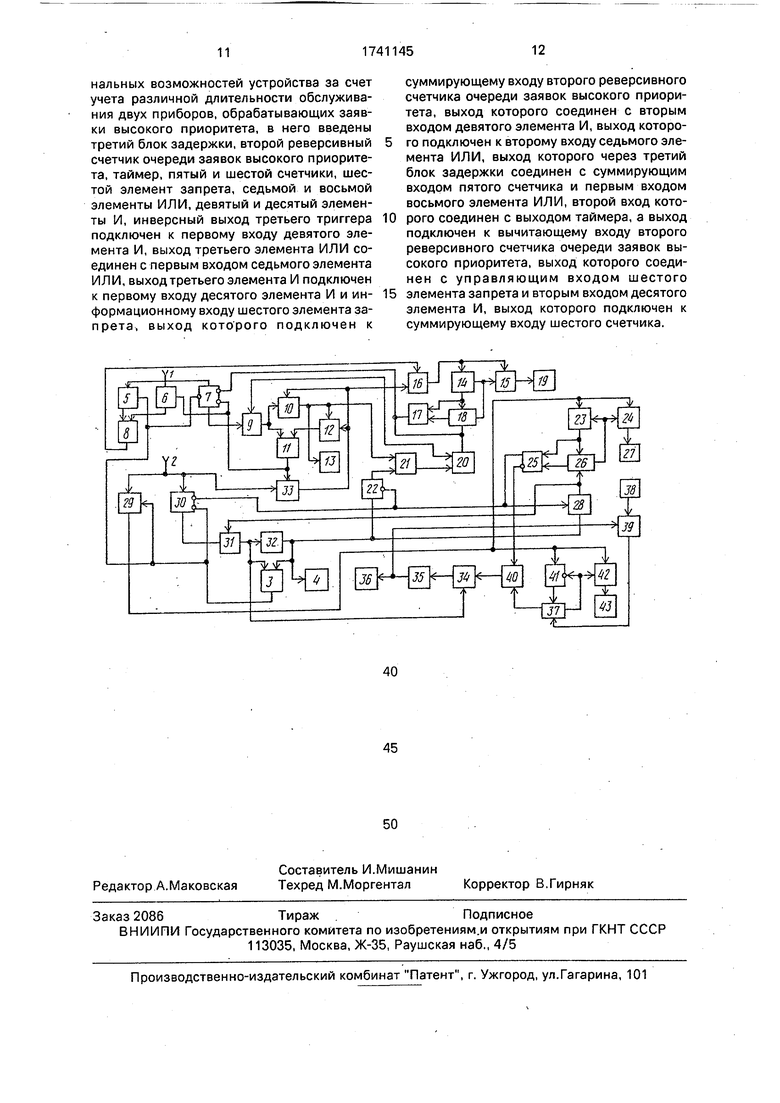

На чертеже представлена структурная схема устройства.

В практике проектирования систем массового обслуживания участились случаи не- обходимости включения одной высокоприоритетной заявки приборов разной длительности обслуживания. Для моделирования таких систем предлагается настоящее устройство.

Устройство содержит входы заявок низкого 1 и высокого 2 приоритетов, четвертый триггер 3, счетчик 4, восьмой 5 и первый 6 элементы И, первый элемент 7 запрета, пятый 8 и первый 9 элементы ИЛИ, первый блок 10 задержки, второй триггер 11, второй элемент ИЛИ 12, счетчик 13, четвертый эле- мент 14 запрета, седьмой элемент И 15, изветом элемент ИЛИ 16, первый триггер 17,

реверсивный счетчик 18 очереди заявок низкого приоритета, счетчик 19, шестой элемент И 20, четвертый элемент ИЛИ 21, третий элемент 22 запрета,пятый элемент 23 запрета, пятый элемент И 24, третий триггер 25, первый реверсивный счетчик 26 очереди заявок высокого приоритета, счетчик 27, четвертый 28 и третий 29 элементы И, второй элемент30 запрета, третий элемент ИЛИ 31, второй блок 32 задержки, второй элемент И 33, седьмой элемент ИЛИ 34, блок 35 задержки, пятый счетчик 36, второй реверсивный счетчик 37 очереди заявок высокого приоритета, таймер 38, восьмой элемент ИЛИ 39, девятый элемент И 40, шестой элемент 41 запрета, десятый элемент И 42, шестой счетчик 43; первый вход первого элемента И 6 и информационный вход первого элемента 7 запрета объединены и являются входом заявок низкого приоритета устройства, выход первого элемента 7 запрета соединен с первым входом первого элемента ИЛ И 9, выход которого подключен к входу запуска первого блока 10 задержки, выход которого соединен с первым входом второго элемента ИЛИ 12, а вход сброса первого блока 10 задержки подключен к выходу второго элемента И 33, первый вход третьего элемента И 29 и информационный вход второго элемента 30 запрета объединены и являются входом заявок высокого приоритета устройства, выход третьего элемента ИЛИ 31 подключен к входу запуска второго блока 32 задержки, выход которого соединен с информационным входом третьего элемента 22 запрета и первым входом четвертого элемента И 28, выход которого подключен к вычитающему входу первого реверсивного счетчика 26 очереди заявок высокого приоритета, выход переполнения которого подключен к первому входу пятого элемента И 24, выход которого является выходом потерянных заявок высокого приоритета устройства, выход первого блока 10 задержки соединен с первым входом четвертого элемента ИЛИ 21, второй вход которого соединен с выходом третьего элемента 22 запрета, а выход четвертого элемента ИЛИ 21 подключен к первому входу шестого элемента И 20, выход которого соединен с вычитающим входом реверсивного счетчика 18 очереди заявок низкого приоритета и вторым входом первого элемента ИЛИ 9, выход переполнения реверсивного счетчика 18 очереди заявок низкого приоритета соединен с управляющим входом четвертого элемента 14 запрета и первым входом седьмого элемента И 15, выход которого является выходом потерянных заявок низкого приоритета; первый вход восьмого элемента И 5 соединен с входом заявок низкого приоритета устройства, а выход восьмого элемента И 5 подключен к первому входу пятого элемента ИЛИ 8, второй вход которого подключен к выходу

первого элемента И 6, а выход пятого элемента ИЛИ 8 соединен с первым входом шестого элемента ИЛИ 16, выход которого подключен к второму входу седьмого элемента И 15 и информационному входу чет0 вертого элемента 14 запрета, выход которого соединен с единичным входом первого триггера 17 и суммирующим вхо дом реверсивного счетчика 18 очереди заявок низкого приоритета, выход обнуления

5 которого подключен к нулевому входу первого триггера 17, прямой выход которого соединен с вторым входом шестого элемента И 20 и первым управляющим входом пер0 вого элемента 7 запрета, второй управляющий вход которого подключен к прямому выходу второго триггера 11, второму входу первого элемента И 6 и первому входу второго элемента И 33, второй вход

5 которого соединен с входом заявок высокого приоритета устройства, а выход подключен к второму входу шестого элемента ИЛИ 16 и второму входу второго элемента ИЛИ 12, выход которого подключен к единично0 му входу второго триггера 11, нулевой вход которого соединен с выходом первого элемента ИЛИ 9; выход третьего элемента И 29 соединен с вторым входом пятого элемента И 24 и информационным входом пятого эле5 мента 23 запрета, выход которого подключен к единичному входу третьего триггера 25 и суммирующему входу первого реверсивного счетчика 26 очереди заявок высокого приоритета, выход переполнения которого

0 соединен с управляющим входом пятого элемента 23 запрета, а выход обнуления - с нулевым входом третьего триггера 25, прямой выход которого подключен к второму входу четвертого элемента И 28, управляющему

5 входу третьего элемента 22 запрета и первому управляющему входу второго элемента 30 запрета , выход которого подключен к первому входу третьего элемента ИЛИ 31, второй вход которого соединен с выходом четвертого эле0 мента И 28, а выход третьего элемента ИЛИ 31 подключен к единичному входу четвертого триггера 3, нулевой вход которого соединен с выходом второго блока 32 задержки, прямой выход четвертого триггера 3 соединен с вто5 рым управляющим входом второго элемента 30 запрета, вторым входом третьего элемента И 29, третьим управляющим входом первого элемента 7 запрета и вторым входом восьмого элемента И 5, первый вход девятого элемента И 40 подключен к инверсному выходу третьего триггера 25, первый

вход седьмого элемента ИЛИ 34 соединен с входом третьего элемента ИЛИ 31, информационный вход шестого элемента 41 запрета и первый вход десятого элемента И 42 подключен к выходу третьего элемента И 29, суммирующий вход второго реверсивного счетчика 37 очереди заявок высокого приоритета подключен к выходу шестого элемента 23 запрета, а вычитающий вход - к выходу восьмого элемента ИЛИ 39, первый вход которого подключен к выходу таймера 38, а второй вход восьмого элемента ИЛИ 39 соединен с входом пятого счетчика 36 и выходом третьего блока 35 задержки, вход которого подключен к выходу седьмого элемента ИЛИ 34, второй вход которого соединен с выходом девятого элемента И 40, второй вход которого подключен к первому выходу второго реверсивного счетчика 37 очереди заявок высокого приоритета, второй выход которого соединен с управляющим входом шестого элемента 41 запрета и с вторым входом десятого элемента И 42, выход которого подключен к входу шестого счетчика 43.

Блок 35 задержки имитирует работу прибора II и имеет значительно большую длительность обслуживания заявок высокого приоритета. Таймер 38 вырабатывает метки времени с периодом повторения, равным времени старения заявок высокого приоритета.

В начальный момент времени все триггеры находятся в нулевом состоянии. Импульс с входа 1, имитирующий сообщение низкого приоритета, поступает через элемент 7 запрета и элемент ИЛИ 9 на вход блока 10 задержки и одновременно на вход триггера 11. Последний устанавливается в единичное состояние, запрещающее прохождение импульсов, имитирующих сообщения низкого приоритета, через элемент 7 запрета и разрешающее их прохождение через элемент И 6, элемент ИЛИ 8, элемент ИЛИ 16, элемент 14 запрета на суммирующий вход счетчика 18, который имитирует буфер сообщений низкого приоритета.

При полном заполнении буфера на выходе переполнения счетчика 18 устанавливается сигнал, запрещающий прохождение заявок через элемент 14 запрета и разрешающий их прохождение через элемент И 15 на счетчик 19, подсчитывающий количество потерянных сообщений низкого приоритета.

Импульс, задержанный на время Тн в блоке 10 задержки (имитация обслуживания заявок низкого приоритета), поступает на вход счетчика 13, подсчитывающего количество обработанных заявок низкого приоритета. Одновременно этот же импульс через элемент ИЛ И 12 устанавливает триггер 11 в нулевое состояние, а также через элемент ИЛИ 21 поступает на вход элемента И 20.

Если буфер сообщений низкого приоритета содержит сообщения (счетчик 18 не пуст), то элемент И 20 открыт, так как на втором его входе имеется единичный потенциал от триггера 17, установленного в это состояние

0 первой же заявкой, поступившей в буфер сообщений (счетчик 18). В этом случае импульс проходит через элемент И 20 и элемент ИЛИ 9 на вход блока 10 задержки, имитируя выдачу сообщения на обработку

5 из буфера. Этот же импульс поступает на вычитающий вход счетчика 18 и уменьшает его содержимое на единицу.

В момент обнуления буфера (счетчика 18) импульс с выхода обнуления перебрасы0 вает триггер 17, который блокирует элемент И 20 и подает разрешающий потенциал на вход элемента 7.

Импульс, имитирующий сообщение высокого приоритета, поступает с входа 2 че5 рез элемент 30 запрета, элемент ИЛИ 31 на вход блока 32 задержки, через элемент ИЛИ 34 на блок 35 задержки и одновременно на единичный вход триггера 3. Последний устанавливается в единичное состояние, запре0 щающее прохождение импульсов, имитирующих сообщения высокого приоритета, через элемент 30 запрета и разрешающее их прохождение через элемент И 29, элемент 23 запрета на суммирующий вход

5 счетчика 26, имитирующий буфер сообщений высокого приоритета прибора I, а также через элемент 41 запрета на суммирующий вход счетчика 37, имитирующий буфер сообщений высокого приоритета прибора II

0 (имеющего значительную длительность обслуживания заявок). Этот же сигнал от триггера 3 запрещает прохождение сообщений низкого приоритета через элемент 7 запрета и разрешает их прохождение через элемент

5 И 5, элемент ИЛИ 8, элемент ИЛИ 16, элемент 14 на суммирующий вход счетчика 18.

В случае полного заполнения счетчика 26 сообщения высокого приоритета проходят через элемент И 24 на счетчик 27, под0 считывающий количество необработанных заявок высокого приоритета (аналогично схеме для заявок низкого приоритета). Таким же образом в случае полного заполнения счетчика 37 сообщения высокого

5 приоритета, обслуживаемые прибором II, проходят через элемент И 42 на счетчик 43, подсчитывающий количество необработанных заявок высокого приоритета прибором, имеющим значительную длительность обслуживания.

Импульс, задержанный на время Т в блоке 32 задержки (имитация обслуживания сообщения высокого приоритета), поступает на вход счетчика 4, подсчитывающего количество обработанных заявок высокого приоритета. Одновременно этот же импульс устанавливает триггер 3 в нулевое состояние. Если в буфере сообщений высокого приоритета (счетчик 26) есть сообщение, то на выходе триггера 25 имеется потенциал, закрывающий элемент 22 и открывающий элемент И 28,

Импульс с выхода блока 32 задержки поступает через открытый элемент И 28 и элемент ИЛИ 31 на вход блока 32 задержки, имитируя выдачу сообщения из буфера сообщений высокого приоритета. Одновременно с этим содержимое счетчика 26 уменьшается на единицу, так как этот импульс поступает на вычитающий вход счетчика 26.

Импульс, задержанный на время Тд в блоке 35 задержки (имитация работы прибора II, имеющего значительную длительность обслуживания сообщений), поступает на вход счетчика 36, подсчитывающего количество обработанных заявок высокого приоритета прибором II. Одновременно этот же импульс поступает через элемент ИЛ И 39 на вычитающий вход реверсивного счетчика 37. Уменьшение количества заявок в счетчике 37 производится также таймером 38, ими- тируя тем самым стирание устаревшей заявки.

Если счетчик 26 становится пустым, то импульп с его выхода обнуления перебрасывает триггер 25 в нулевое состояние, в результате чего элемент И 28, элемент 22 запрета закрываются, а на элемент И 40 подается разрешающий потенциал. В этом случае опрашивается буфер сообщений низкого приоритета - импульс с выхода блока 32 задержки проходит через элемент 22, элемент ИЛИ 21 на элемент И 20 (если счетчик 18 не пуст) и далее через элемент ИЛИ 9 на вход элемента 10 задержки, имитируя выдачу сообщения низкого приоритета из буфера. В то же время разрешается прохождение заявок с буфера сообщений высокого приоритета прибора II (при их наличии на счетчике) через элемент И 40, элемент ИЛИ 34 на блок 35 задержки, имитируя выдачу сообщения высокого приоритета.

Если в устройстве обрабатывается заявка низкого приоритета и приходит заявка высокого приоритета, то обработка заявки низкого приоритета прекращается, она записывается в буфер низкого приоритета, а заявка высокого приоритета обрабатывается.

Имитация указанной ситуации происходит следующим образом.

При обслуживании заявки низкого приоритета на первый вход элемента И 33 подается единичный сигнал с выхода триггера 11. Импульс-заявка высокого приоритета через элемент 30, элемент ИЛИ 31 поступает на вход блока 32 задержки. Этот же импульс через вход элемента И 33 поступает

на сбрасывающий вход блока 10 задержки и устанавливает его в нулевое состояние, а также проходит через элемент ИЛИ 12 на триггер 1-1 и устанавливает его в нулевое состояние. Кроме того, этот импульс проходит через элемент 16, элемент 14 на суммирующий вход счетчика 18, имитируя перевод сообщения из обслуживающего прибора в буфер сообщения низкого приоритета. Счетчики 13 и 4 подсчитывают количество обработанных заявок низкого и высокого приоритетов соответственно, а счетчики 19 и 27 подсчитывают количество потерянных заявок соответственно низкого и высокого приоритетов. Счетчики 36 и 43 подсчитывают количество соответственно обработанных и не обработанных заявок высокого приоритета прибором II.

В процессе моделирования на основе рассматриваемых характеристик:

т, П2 - количество обработанных заявок низкого и высокого приоритетов I прибора соответственно;

mi, гп2- количество потерянных заявок низкого и высокого приоритетов I прибора

соответственно;

К, количество обработанных и необработанных заявок высокого приоритета II прибора соответственно;

Т - время процесса моделирования,

можно получить следующие показатели СМО:

а) -ф- ; fn ; /гз

Л

к + к

т - г - т

с где,«1 1(«2 ,/43 интенсивности обслуживания заявок низкого и высокого приоритетов I прибора и заявок высокого приоритета II прибора соответственно;

12 .„. К

0 б) Pl- TTh

Р2.

;Рз

л

П2 + 12 К + К

где Pi, Ра, Рз - вероятности потерь заявок низкого и высокого приоритетов I прибора и заявок высокого приоритета II прибора соответственно. 5 Формула изобретения

Устройство для моделирования систем массового обслуживания по авт, св. № 1 387009, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет учета различной длительности обслуживания двух приборов, обрабатывающих заявки высокого приоритета, в него введены третий блок задержки, второй реверсивный счетчик очереди заявок высокого приоритета, таймер, пятый и шестой счетчики, шестой элемент запрета, седьмой и восьмой элементы ИЛИ, девятый и десятый элементы И, инверсный выход третьего триггера подключен к первому входу девятого элемента И, выход третьего элемента ИЛИ соединен с первым входом седьмого элемента ИЛИ, выход третьего элемента И подключен к первому входу десятого элемента И и информационному входу шестого элемента за- прета, выход которого подключен к

0

5

суммирующему входу второго реверсивного счетчика очереди заявок высокого приоритета, выход которого соединен с вторым входом девятого элемента И, выход которого подключен к второму входу седьмого элемента ИЛИ, выход которого через третий блок задержки соединен с суммирующим входом пятого счетчика и первым входом восьмого элемента ИЛИ, второй вход которого соединен с выходом таймера, а выход подключен к вычитающему входу второго реверсивного счетчика очереди заявок высокого приоритета, выход которого соединен с управляющим входом шестого элемента запрета и вторым входом десятого элемента И, выход которого подключен к суммирующему входу шестого счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1387009A1 |

| Устройство для моделирования систем массового обслуживания | 1990 |

|

SU1716533A1 |

| Устройство для моделирования процесса обслуживания заявок с различными приоритетами | 1983 |

|

SU1096654A1 |

| Устройство для моделирования систем массового обслуживания | 1988 |

|

SU1532943A1 |

| Устройство для моделирования систем массового обслуживания | 1983 |

|

SU1151981A1 |

| Устройство для моделирования систем массового обслуживания | 1985 |

|

SU1290344A1 |

| Устройство для моделирования процесса обслуживания заявок | 1989 |

|

SU1667099A1 |

| Устройство для моделирования систем массового обслуживания | 1988 |

|

SU1612309A1 |

| Устройство для моделирования систем массового обслуживания | 1984 |

|

SU1191916A1 |

| Устройство для моделирования процесса обслуживания заявок с различными приоритетами | 1985 |

|

SU1305706A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке и моделировании систем массового обслуживания. Целью изобретения является расширение функциональных возможностей устройства за счет учета различной длительности обслуживания двух приборов, обрабатывающих заявки высокого приоритета. Устройство дополнительно содержит второй реверсивный счетчик очереди заявок высокого приоритета, блок задержки, таймер, элемент запрета, два счетчика, два элемента ИЛИ и два элемента И. В результате этого возможен учет количества обработанных и необработанных заявок абсолютного приоритета прибором, имеющим значительное время обслуживания заявок. 1 ил.

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1387009A1 |

Авторы

Даты

1992-06-15—Публикация

1989-10-23—Подача